目录

MROM,PROM,EEPROM 存储二进制信息 0/1 的原理

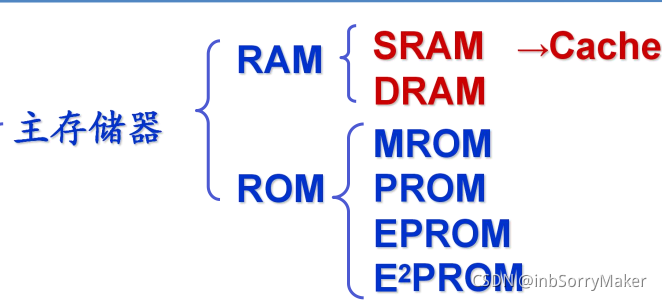

存储系统的概念

(1)按存储介质分类

• 半导体器件:半导体存储器(RAM、ROM,用作主存)

• 磁性材料:磁表面存储器(磁盘、磁带,用作辅存)

• 光介质:光盘存储器(用作辅存)

(2)按存取方式分类

• 随机存取存储器:存储器中任何存储单元的内容都能被 随机存取,且存取时间和存储单元的物理位置无关(主 存)

• 顺序存取存储器:存取时间和存储单元的物理位置有关 (磁盘、磁带)

• 相联存储器:按内容访问。

(3)按存储器的读写功能分类

• 只读存储器(ROM):一般隐含指随机存取。

• 读写存储器(RAM):一般隐含指随机存取。

(4)按信息的可保存性分类

• 永久记忆的存储器:又称非易失性存储器,在断电后还能保存信息(辅存、ROM)[系统区]

• 非永久记忆的存储器:又称易失性存储器,在断电后信息丢失(主存中的RAM)

(5)按在计算机系统中的作用分类

• 主存储器:又称内存,为主机的一部分,用于存放系统当前正在执行的数据和程序,属于临时存 储器。

• 辅助存储器:又称外存,为外部设备,用于存放暂不用的数据和程序,属于永久存储器。

MROM,PROM,EEPROM 存储二进制信息 0/1 的原理

基本原理

1. ROM的分类 — ROM、PROM、EPROM

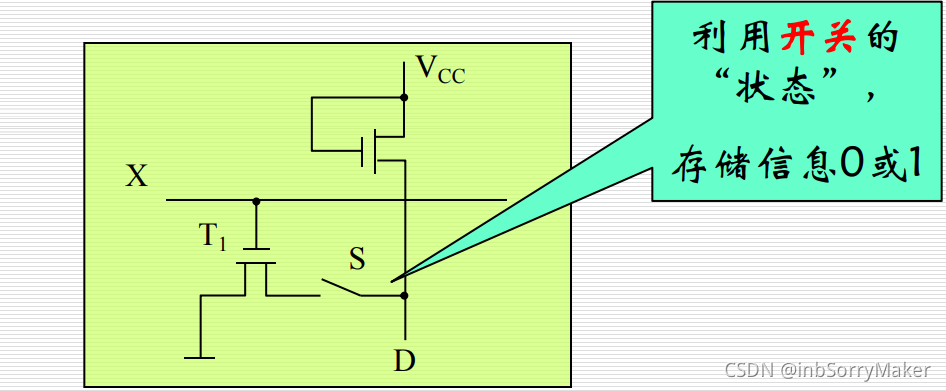

(MROM)掩模式只读存储器:

只能读出不能写入;可靠性高, 集成度高,价格便宜

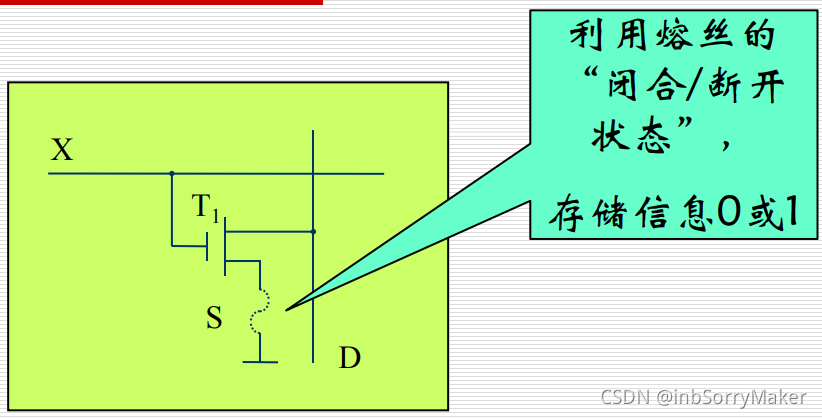

(PROM)一次编程只读存储器:

可进行一次性改写,以后只能 读出不能写入;可靠性差,基本不再使用

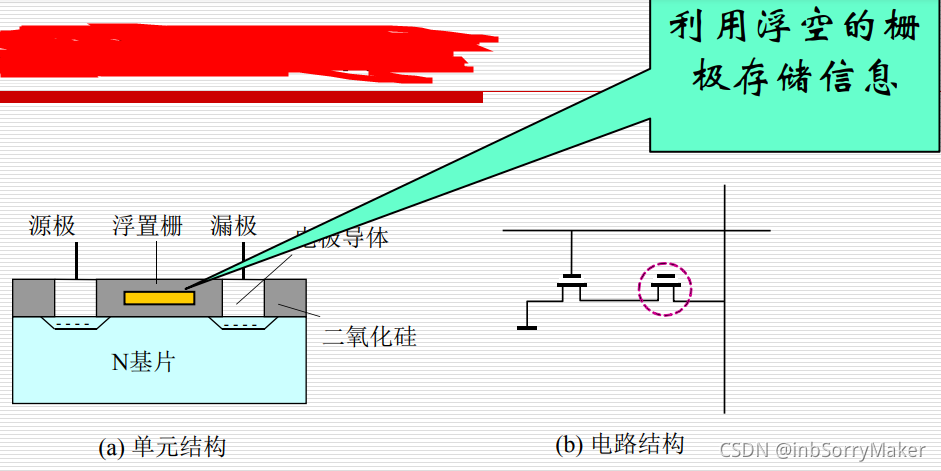

(EPROM)反复擦除编程只读存储器:

可多次改写;可靠性高, 编程简单,价格便宜,得到广泛使用

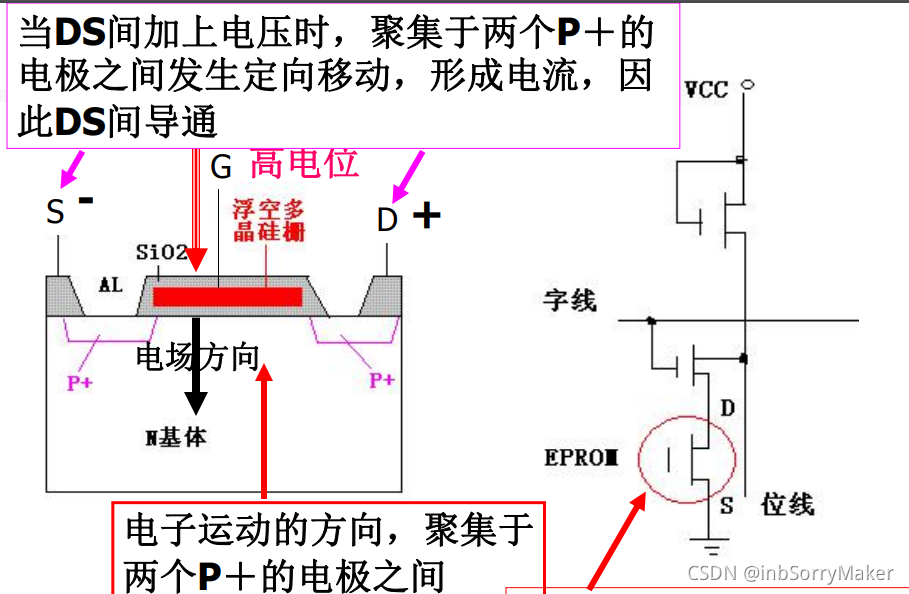

当在DS间施加高电压进行编程时,电子能被通过绝缘层注入到硅栅,并永久保留

光擦可编程ROM(EPROM)工作原理:

(1)多晶硅的G1栅极被Sio2包围,浮空栅

(2)原理:利用浮空栅G1存储信息,有电 子时存储“0” ,无电子时存储“1”

(3)EPROM出厂时存储矩阵输出为全‘1’ 。

(4)当在D端加上几十伏的脉冲电压,沟道 中造成雪崩产生很多高能电子,若G2栅极加 上正电压,可使沟道中电子注入到G1。

EEPROM(写多次读多次)

类似于EPROM,但是区别是EEPROM能单字节修改,电擦除且可以在线改写,而EPROM不能单字节修改,EPROM只能脱机改写

存储原理:

利用浮空栅极G1(控制栅)存储信息, 有电子,存储了“1” ,没有电子时,存储“0”

出厂时,存储内容为全“1”状态 n G1和D之间厚度极薄,可产生隧道效应。

G2(抹去栅)栅极加20V正脉冲电压时,可对G1进 行电子注入。

G2接地,D接20V正脉冲,G1电子返回衬底

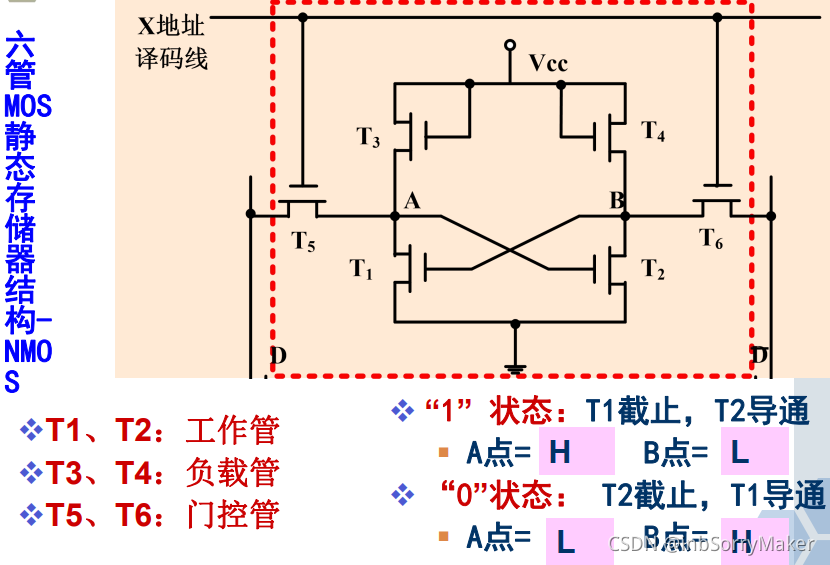

SRAM,DRAM存储二进制信息 0/1 的原理;

SRAM原理

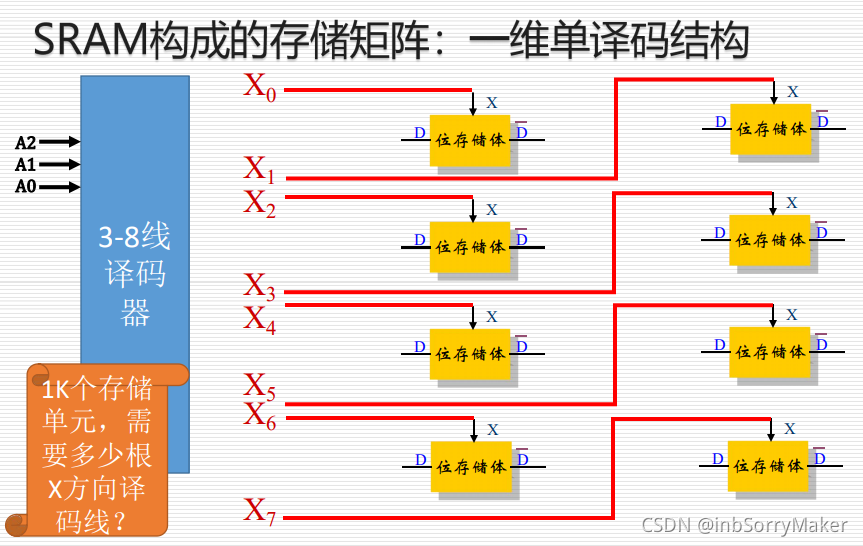

地址译码(X单方向):

线性译码方式: n位地址线,经过一维译码后,有2^n根选择线。N=12,则选择 线有2^12=4096根

1K个存储单元,需要多少根X方向译码线? 答:2^10个存储单元,要10根X方向译码线

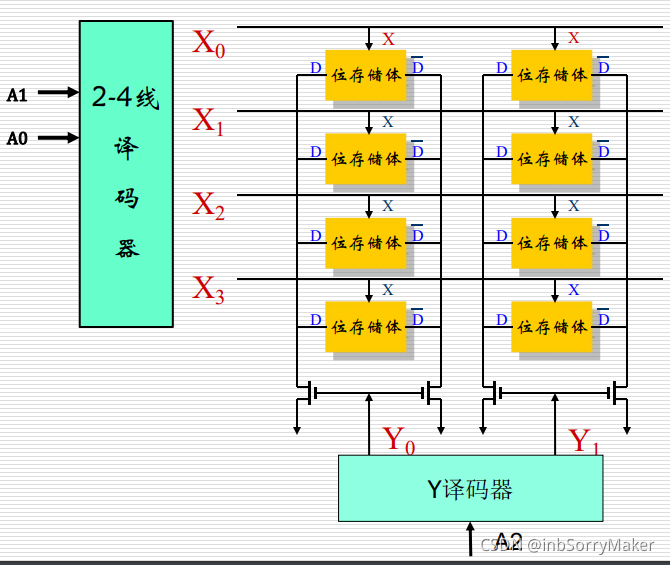

双向译码方式:

n位地址分为行、 列地址分别译码, 有2^([n/2]+1)根选择线

N=12,则行地址 6位,行选择线有2^6=64根;列地址6位,列选择 线有2^6=64根,共 128根。

选择线相对于X方向译码大大减少

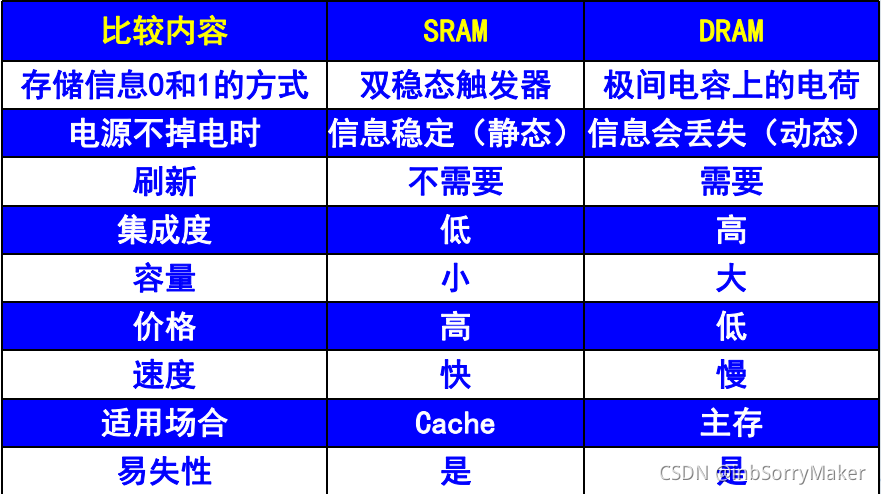

SRAM特点

使用双稳态触发器表示0和1代码。

电源不掉电的情况下,信息稳定保持(静态)。

存取速度快,集成度低(容量 小),价格高。

常用作高速缓冲存储器Cache

有片选,使能控制信号

DRAM特点

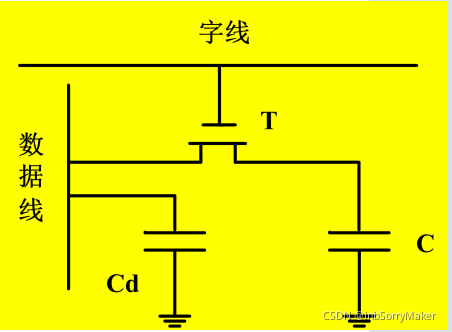

通过MOS动态存储器结构

“1”状态:电容C上有电荷

“0”状态:电容C上无电荷

平时(防止泄露):

字线=L(低),T截止, 数据线与C隔离

读写操作字线都要为高H ,T导通

读操作:字线=H(高),T导通

读“0” :C上无电荷流入数据线

读“1” :C放电,电荷流入数据线(破坏性读出)

破坏性读出:

{

再生:读出后信息可能被破坏,需要重写。

刷新:经过一段时间后,信息可能丢失,需要重写。

}

写操作:字线=H(高),T导通

写“0” :数据线=L,C若有电荷则放电

写“1” :数据线=H,对C充电

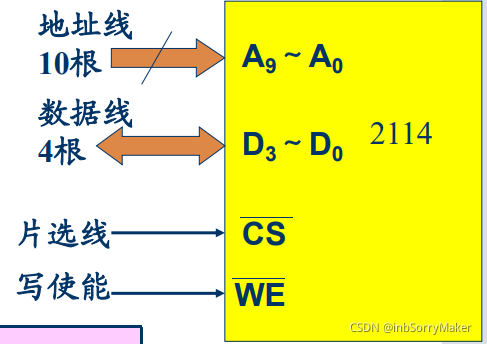

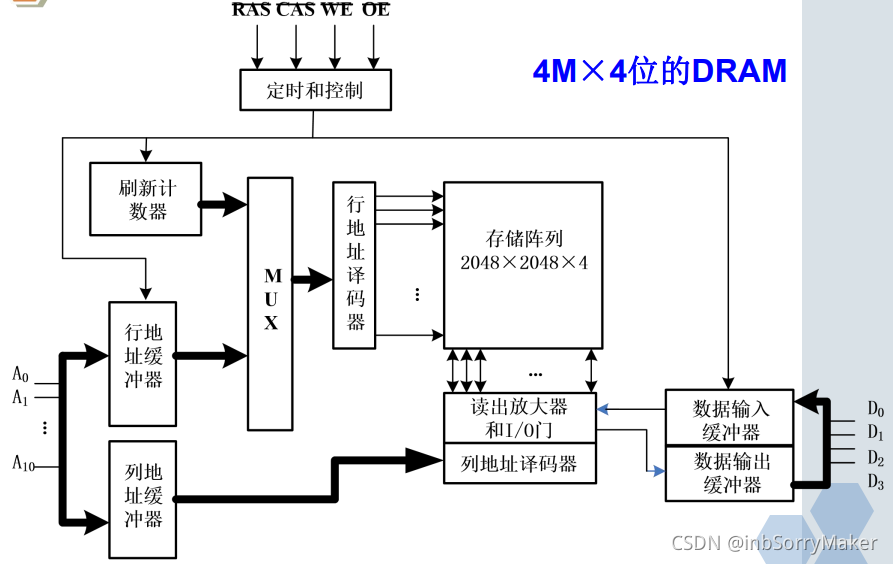

DRAM的位单元扩展成存储器,与SRAM不同的地方:

采用双向译码;(容量大)

芯片地址引脚Ai: • 约为存储器地址码位数的一半; • 行、列地址分时送入;

如何区分地址引脚上的地址是行地址还是列地址?

控制引脚:使用行地址选通信号RAS和列地址选通信号CAS来区分行列地址;

先送行地址,再送列地址;

即RAS先有效,CAS后有效;

含刷新和再生电路;

使用半导体器件中分布电容上有无电荷来表示0和1代码。 电源不掉电的情况下,信息也会丢失,因此需要不断刷新。 存取速度慢,集成度高(容量大),价格低常用作内存条。

DRAM刷新方式

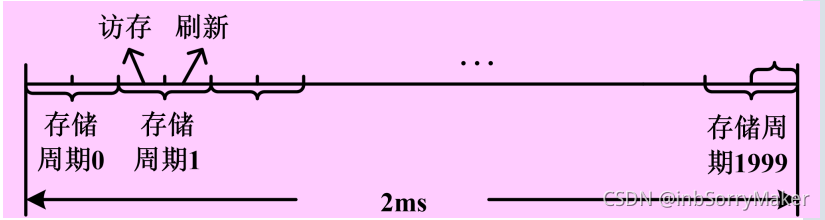

刷新操作:即是按行来执行内部的读操作。由刷新计数器产生行地址,选择当前要刷新的行,读即刷新, 刷新一行所需时间即是一个存储周期。

刷新周期:从上一次刷新结束到下一次对整个DRAM全部刷新一遍为止,这一段时间间隔称为刷新周期。

单元刷新间隔时间:DRAM允许的最大信息保持时间; 一般为2ms。

刷新行数:单个芯片的单个矩阵的行数。

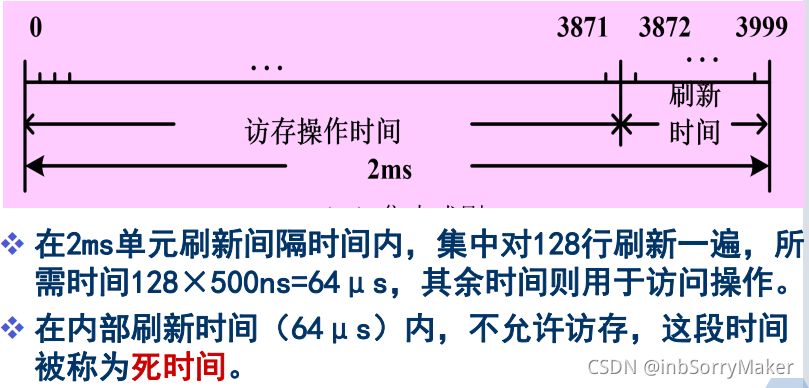

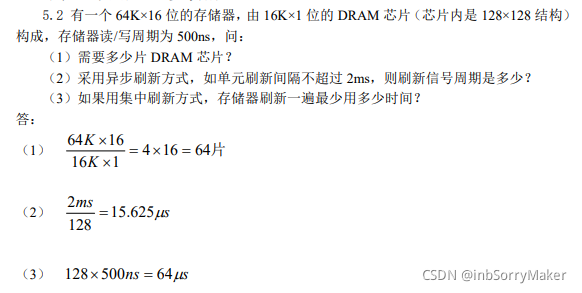

集中刷新

在刷新周期内,选一段时间,对DRAM的所有行全部刷新一遍,在此期间停止对存储器的读写操作,这段时间称为“死时间”,又称访存死区(死区太大整体降低了速度)。假设是128×128的DRAM,存储周期是500ns,则死区时间就是

500ns×128=64μs

分散刷新

一般来说,刷新一次的时间等于存取周期。而分散刷新就是在每个存储周期后刷新一行,这样假设原本0.5微秒的芯片存取周期,换成系统存取周期就变成1微秒了。刷新周期缩短,为128×1μs =128μs。

由于分散刷新每访问一次就刷一次,因此假设128×128个存储单元的DRAM,一次刷新周期内,刷新的行的次数都大于128了(占用了读更多数据的时间,亏了),降低了整机的速度。

在2ms的单元刷新间隔时间内,对DRAM刷新了 2ms÷128μs=15遍。(太浪费时间了)

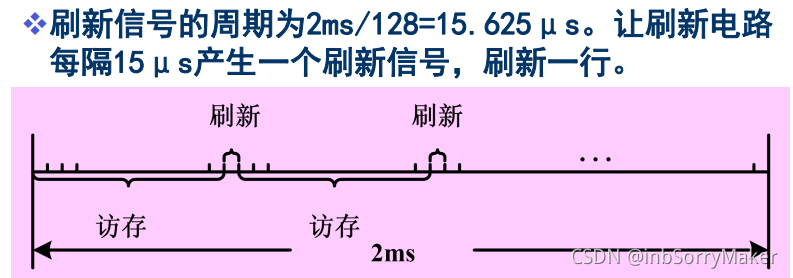

异步刷新

异步刷新结合了上面两种刷新,把集中刷新的死区时间平均分散开来,假设DRAM128×128,则只需要刷新128次,并且每2ms/128= 15.625μ秒刷新一行。

总结

相关作业习题

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?