单周期CPU的设计

一、实验目的:

- 掌握单周期cpu设计的方法和思想

- 使用verilog HDL补充单周期cpu相关各模块的代码

- 使用vivado软件对模块进行仿真测试

二、实验平台:

vivado设计套件

三、实验任务及要求:

- 补充各模块的代码,完成单周期cpu的设计。

1)完成adder加法器的verilog代码。

编写verilog代码,补全adder.v文件的代码内容,实现如下功能:

- 将32位二进制数operand1,operand2和低位的进位cin相加,并将结果为和result与向高位的进位cout;

- 输入信号operand1,operand2,cin。

- 输出信号result,cout。

2) 完成alu 算术逻辑部件的verilog代码。

编写verilog代码,补全alu.v文件的代码内容,实现如下功能:

输入两个32位操作数alu_src1, alu_src2,以及控制信号alu_control,输出运算结果alu_result.

- 实现两个操作数的逻辑运算:or,xor,and,nor

- 实现两个操作数的算术运算:add,sub,slt,sltu

- 实现移位操作:sll,srl,sra

- 实现高位加载:lui

3) 完成 单周期cpu的verilog代码

编写verilog代码,补全single_circle_cpu.v文件的代码内容,完成如下功能:

- 根据PC值取指令,并能够正确更新PC值

- 对指令译码,输出控制信号

- 读写寄存器

- 完成算术逻辑运算

- 读写存储器。

- 创建vivado工程,添加文件,并对其进行仿真

由仿真结果判断代码是否正确,如有错,根据提示修改。

四、实验过程及结果:

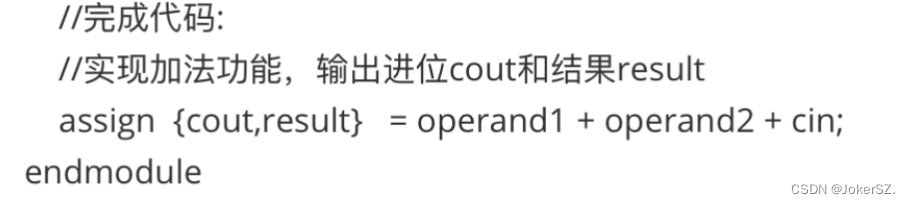

1、adder.v加法器的verilog代码

文件adder.v主要实现的功能是完成一个加法器,由两个输入端32位二进制操作数 operand1和operand2和 一个进位cin组成,输出为进位cout和结果result,则直接使用 assign连续赋值语句即可,{cout,result}代表最高位进位赋值给cout,本位结果存储在result 中。

2、alu.v算术逻辑部件的verilog代码

(1)按位或运算符号位“|”因此只需要ALU的操作数1和操作数2按位或运算,并赋 值给相应的result中,作为可供选择的赋值给最后result的选择项。

![]()

(2)两数按位异或,按位异或符号位“^”,直接将ALU的两个操作数按位异或运算, 并赋值给相应的result中,作为可供选择的赋值给最后result的选择项。

![]()

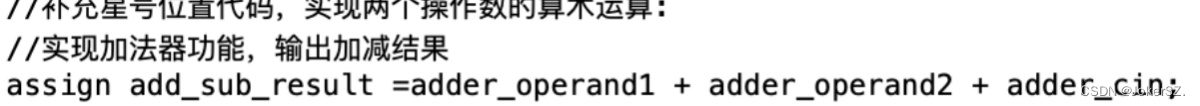

(3)完成加减结果的result返回,由变量声明可知,进行运算的变量是adder_operand1 和adder_operand2和adder_cin,将三者相加即可。

3、single_cycle_cpu.v文件

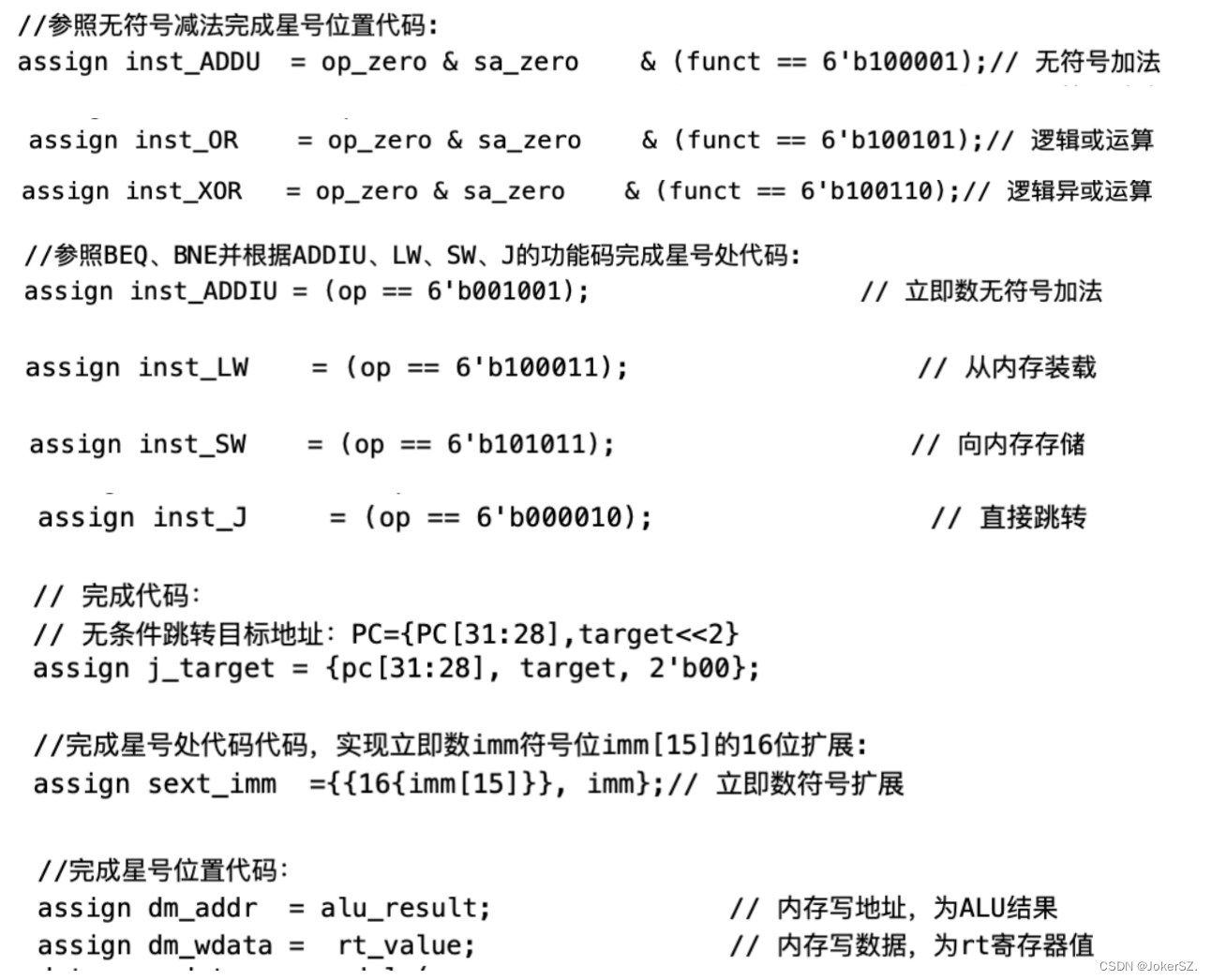

(1)实现无符号加法,只需把op_zero、sa_zero和功能码(这里的无符号加法的功能码 为100001,6位)相与即可实现无符号加法。

(2)逻辑或运算功能码funct为100101

(3)异或运算的功能码为100110

(4)立即数无符号加法的op位置的操作码为001001,填写(op=6’b001001)即可。

(5)对于load,store此类指令,分析操作码,发现指令码中由高六位主导,因此只需运 用操作码高六位进行判断执行何种指令。Lw是从内存装载,其操作码为100011,sw是 向内存存储,其操作码为101011。

(6)J指令是直接跳转,操作码为000010

(7)对于j型指令而言,需要确定目标地址。而在跳转指令中,地址是相对的,因此最 后确定的j_target需要用pc内地址加上相对地址左移2位后的结果(因为在内存中的编 址每一个单元是4的倍数)

- 立即数的符号扩展,实现立即数imm符号位imm[15]的16位扩展,将imm最高位 复制16遍添加到高位即可。

(8)dm_addr是要把ALU的结果的地址写到内存中去,因此直接让其等于alu_result即 可实现该功能;dm_wdata是要把寄存器rt的值写入内存中去,因此直接让其等于寄存器 rt的值(rt_value)即可。

部分代码如下:

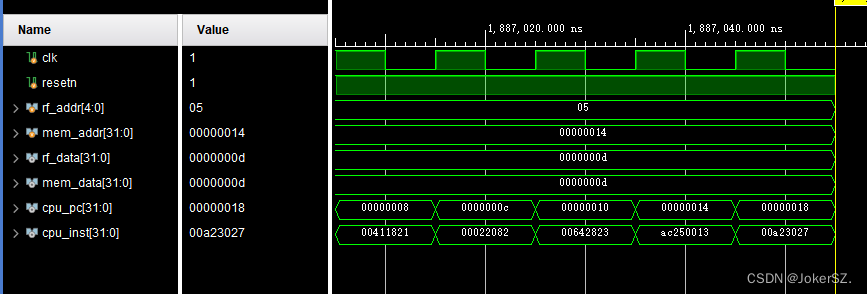

4.实验结果仿真截图:

五、实验总结

本次实验算是我自己设计的第一个简单的CPU,可以进行一些基本的运算等;通过老师和助教给的提示以及相关资料的阅读,我也慢慢地理解了单周期CPU的设计过程,在设计过程中变量也是非常多的,要注意区分好各个变量所表示的含义,还好本次实验难度也已经降低了,通过提示以及所学习的内容可以比较简单的填充好Verilog代码,在填充完成后也通过代码的阅读了解到了各种功能具体的实现方法。通过本次实验的完成,我对Verilog语言及其应用有了更深层次的认识和理解,也让我更清晰地理解并使用一些基本的操作指令。vivado中的仿真功能可以说是比较直观的展现结果,便于自己的理解以及纠错。verilog可以很简单的把复杂电路表示出来,通过代码编写完成单周期CPU在一个周期内的取、译、执、访、写操作。总之,此次实验使我收获了不少,对学习硬件语言以及CPU的设计有了更进一步的认识和理解。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?