-

FPGA设计流程如下图所示:

- 设计定义:确定要实现的功能,如用按键来控制LED灯的亮灭,本质是设计一个 多路选择器(由一个按键控制两路信号),即 将功能抽象成基本电路的组合设计。

- 设计输入:确定输入信号与输出信号,使用硬件描述语言来描述功能。

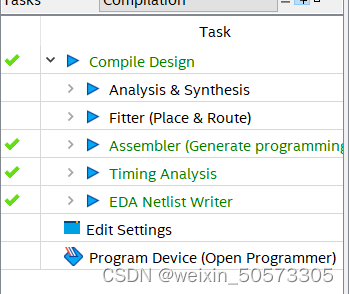

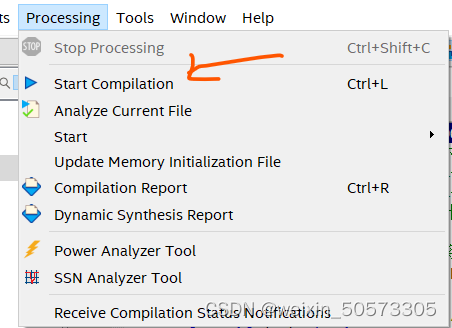

- 分析和综合:综合是将抽象的RTL语言转变成具体的电路的过程,编译(Compile)与纠错过程。

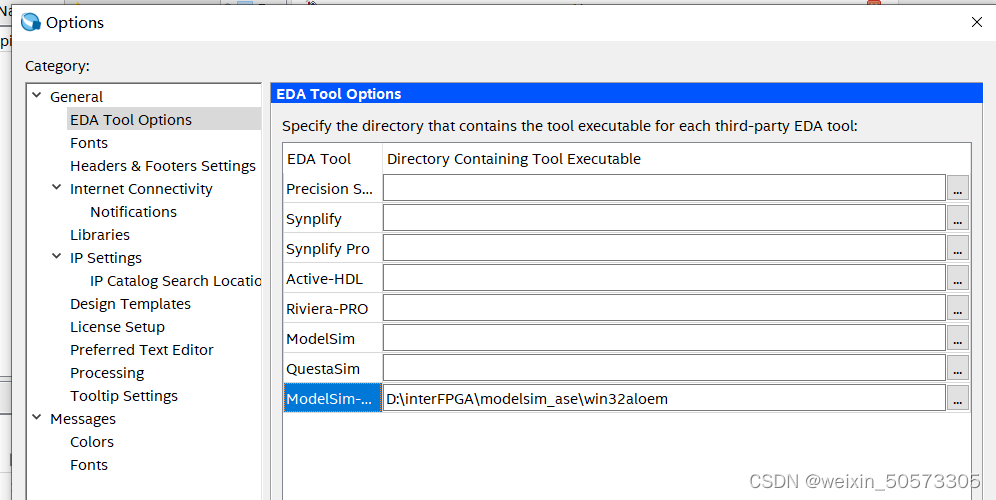

- 功能仿真:RTL级别仿真,通过quartus II软件可以直接调用modelsim-altera进行,初下载的配置操作:(1)quartus-tools-options-EDA Tool Options-Modelsim-Altera,在文本框中添加下载好的modelsim-altera的路径:eg:

- 布局布线:在quartus进行全编译过程中进行的,过程中会进行多个层次的综合,生成RTL图:

- 时序仿真:(又被称为门级仿真),会考虑元器件延时,是在仿真中的Gate Level Simulation进行的。

- IO分配以及配置文件生成:IO分配有两种方式,可以通过编程语句来指定引脚,也可以在Quartus-assignments-Pin planner中指定,需要注意的是,被下载的FPGA的芯片一定要与device中设置的一样,因为这里要绑定是的芯片引脚是与device中选择的芯片一致的,而非与FPGA一致的,二者关系:FPGA引脚(是核心芯片的引脚经过外围电路之后的引脚),软件绑定的引脚(device中所选择的芯片的引脚)。配置文件生成:后缀为.sof的文件。

- 配置(烧写FPGA):Tools-Progammer,注意硬件连接(Hardware),注意下载方式(JTAG),点击Start即可开始。

- 在线调试:包括signal tap logic analyzer,其他调试工具,后续补充。

本文详细介绍了FPGA设计流程,包括设计定义(功能抽象),输入信号确定,分析综合,功能和时序仿真,IO分配与配置文件生成,烧写FPGA以及在线调试等关键步骤。

本文详细介绍了FPGA设计流程,包括设计定义(功能抽象),输入信号确定,分析综合,功能和时序仿真,IO分配与配置文件生成,烧写FPGA以及在线调试等关键步骤。

196

196

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?