目录

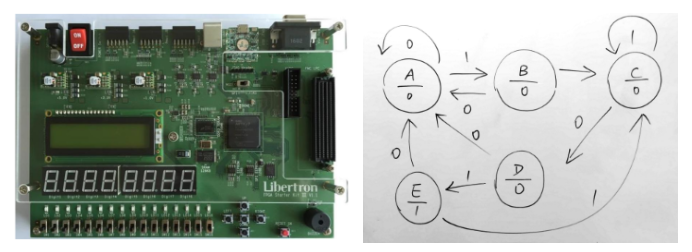

0x00 实现序列检测器(Mealy机): [Sequence 1101]

Ⅰ. 理论部分

0x00 有限状态机(FSM)

首先,状态机设计是一种使用 Flip-Flop 电路设计技术之一。通过定义整体操作为若干状态,根据用户输入或内部操作的结果,将操作移动到下一个状态的原理。

首先,状态机设计是一种使用 Flip-Flop 电路设计技术之一。通过定义整体操作为若干状态,根据用户输入或内部操作的结果,将操作移动到下一个状态的原理。

当前状态 (Current State) 表示任意给定时间点的状态,过渡 (Transition) 意味着通过某一事件(Event) 从一个状态转变到另一个状态。

目录

0x00 实现序列检测器(Mealy机): [Sequence 1101]

首先,状态机设计是一种使用 Flip-Flop 电路设计技术之一。通过定义整体操作为若干状态,根据用户输入或内部操作的结果,将操作移动到下一个状态的原理。

首先,状态机设计是一种使用 Flip-Flop 电路设计技术之一。通过定义整体操作为若干状态,根据用户输入或内部操作的结果,将操作移动到下一个状态的原理。

当前状态 (Current State) 表示任意给定时间点的状态,过渡 (Transition) 意味着通过某一事件(Event) 从一个状态转变到另一个状态。

4957

4957

8250

8250

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?