导读:

DAC(Digital to Analog Conver ),是指将数字信号转变为模拟信号的电子元件。

分类:

电压型(TLV5618):常作为高速 DAC 使用。

电流型(AD7533):

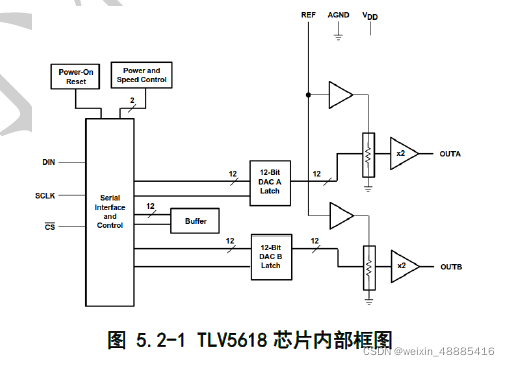

1、芯片简介

1.1、TLV5618工作原理

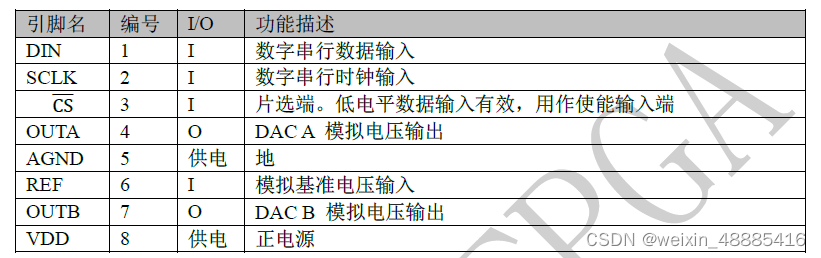

1.2、芯片引脚

1.3、输出电压计算

![]()

其中,REF 是基准电压,本电路中为 2.0 48V ;CODE 是数字电压输入值,范围 0 到 212 -1 。

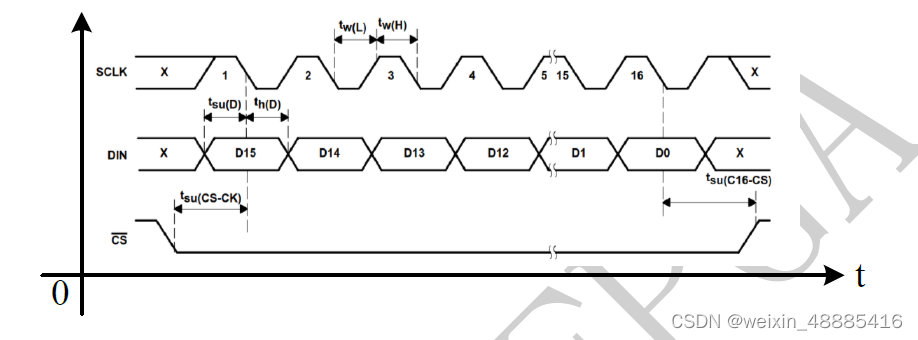

1.4、接口时序

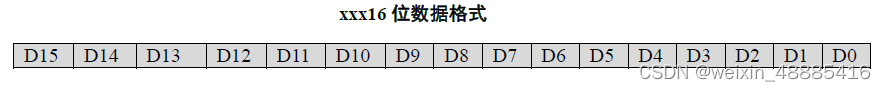

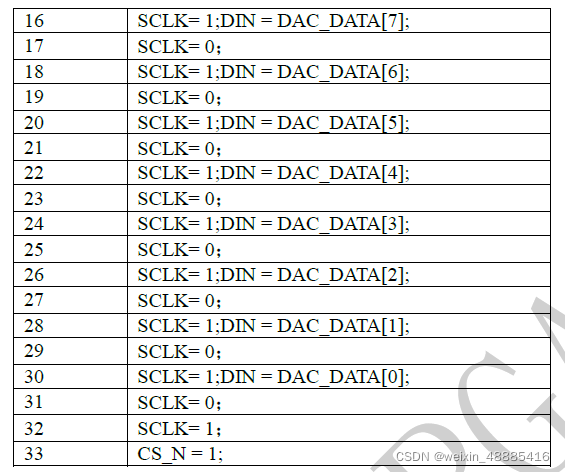

1 6 位 的 数据 按照高位在前, 低位在 后的顺序依次移入。

![]()

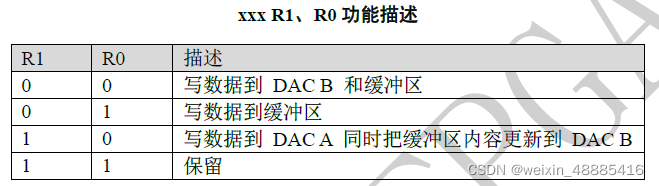

SP D 为速度控制位, PWR 为电源控制位。

2、线性序列机设计思想

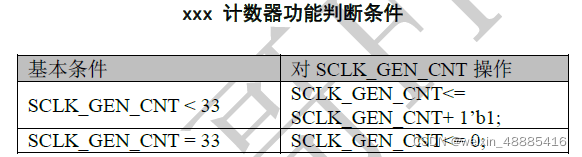

经查阅手册可知器件工作频率SCLK 最大为 20 MH z ,设计 时 留下 一定余量,因此 这里定义其工作频率为 12.5 MH z 。 设置一个两倍于 SCLK 的采样时钟 SCLK2X ,使用 50 M 系统时钟二分频而来即 SCLK2X 为 25 MH z

3、DAC驱动设计(tlv5618.v)

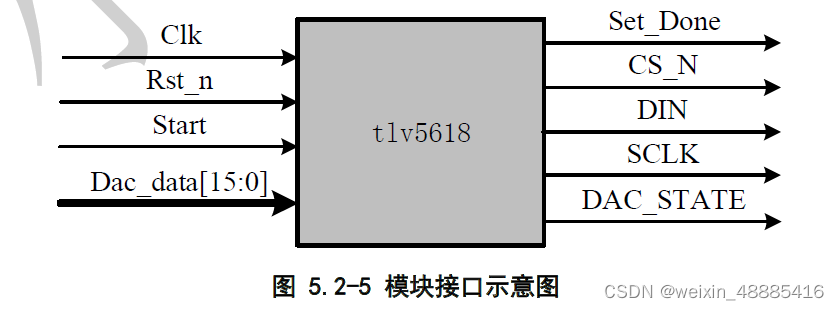

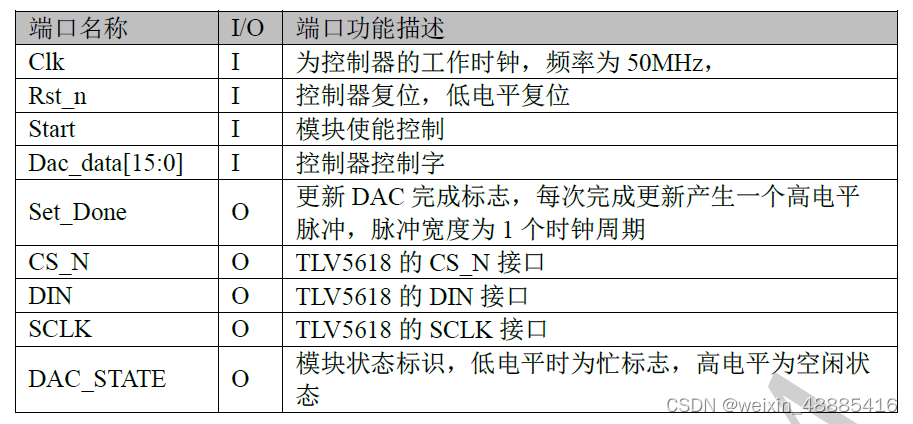

1、根据示意图编写端口

//========================================================================

module tlv5618(

Clk,

Rst_n,

DAC_DATA,

Start,

Set_Done,

DAC_CS_N,

DAC_DIN,

DAC_SCLK,

DAC_State

);

input Clk;

input Rst_n;

input [15:0]DAC_DATA;

input Start;

output reg Set_Done;

output DAC_CS_N;

output DAC_DIN;

output DAC_SCLK;

output DAC_State;

/* 具体如下*/

endmodule

//========================================================================

2、使能信号

//========================================================================

reg en;//转换使能信号

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

en <= 1'b0;

else if(Start)

en <= 1'b1;

else if(trans_done)

en <= 1'b0;

else

en <= en;

//========================================================================

3、生成2倍SCLK使能时钟计数器

//========================================================================

parameter DIV_PARAM = 2;

reg [3:0]DIV_CNT;//分频计数器

reg SCLK2X;//2倍SCLK的采样时钟

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

DIV_CNT <= 4'd0;

else if(en)begin

if(DIV_CNT == (DIV_PARAM - 1'b1))

本文介绍了如何在FPGA中设计一个用于驱动TLV5618 DAC的线性序列机。详细讨论了芯片接口时序,设计了一个2倍SCLK采样时钟,并提供了详细的Verilog代码实现,包括数据移位和转换完成信号的生成。

本文介绍了如何在FPGA中设计一个用于驱动TLV5618 DAC的线性序列机。详细讨论了芯片接口时序,设计了一个2倍SCLK采样时钟,并提供了详细的Verilog代码实现,包括数据移位和转换完成信号的生成。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1461

1461

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?