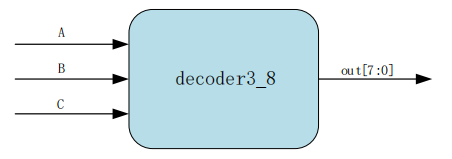

0、译码器的示意图。

----译码器的最典型应用,就是“地址译码”。比如图中n=3,则将3-bit的地址,转变为2^3或者8的片选信号。这个8个片选信号是【8选1】,绝对不会【8选2】,因此也叫【独热码】或者【One-Hot】。当然如果候选的芯片只有5个,则【5选1】也是没有问题的,不一定非要8。

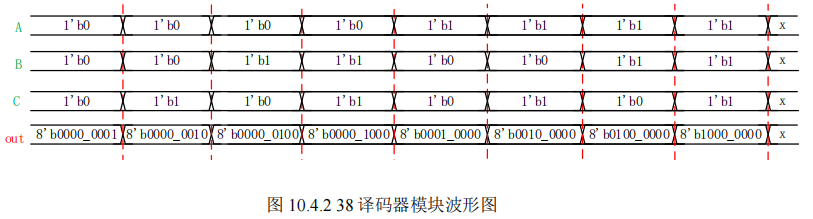

1、波形图。

----这个波形图中的Out是一个8bit的值,这样展示数字逻辑的波形图,很简洁高效。但不知道实际的波形图软件是否可以搞出这种波形图出来。

----先推测一下,个人觉得这个波形图是可能的。因为波形文件就是离散的时间点上的值,这个图同样也是离散的时间点上的值,可以在仿真器写波形文件时,把out的8-bit信号合并为一个数值。或者,也可能在波形文件解析和图形化显示的时候进行8-bit信号值的聚合并转变为数值(图中是二进制,显然也可以是10进制)。

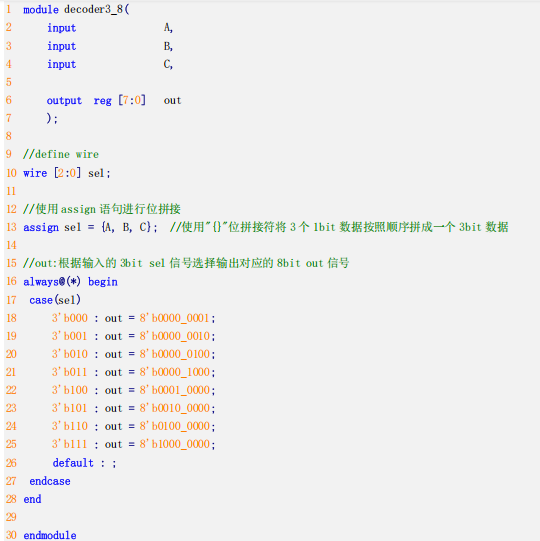

2、Verilog代码:

----再一次明确,always @(*)是一个不带时钟的alwa

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3801

3801

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?