本文是工程top文件DE10_Standard.v的代码解析。

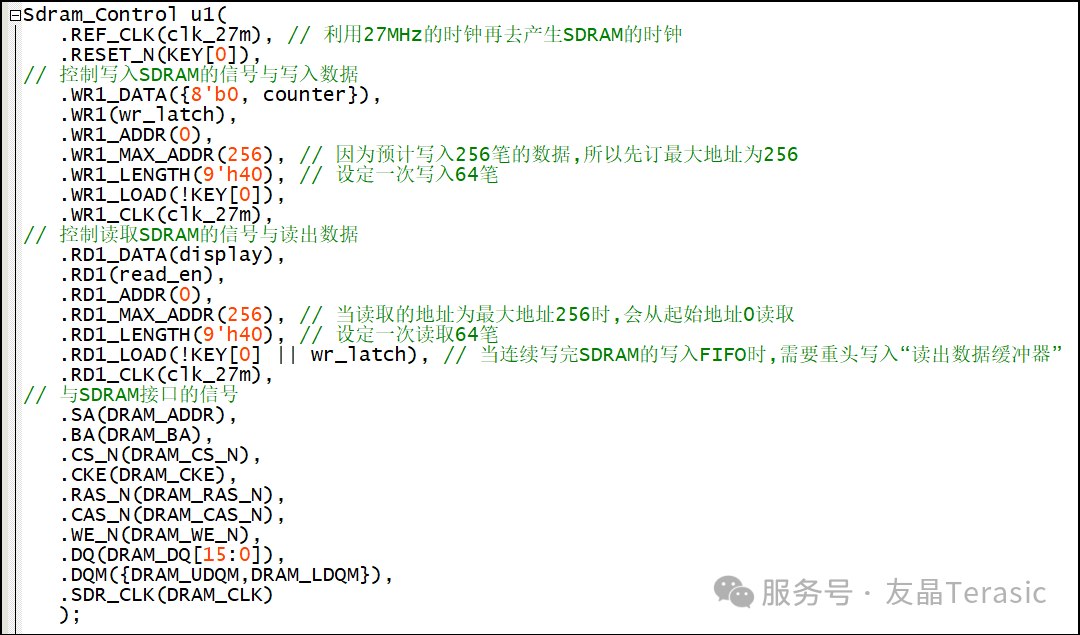

top文件里面首先是例化了 Sdram_Control模块。

按下KEY1触发FIFO写模块写入数据。写入的数据是0-255,接着将FIFO写模块缓存的数据读出并输出给SDRAM器件进行存储,这里设定从SDRAM器件的地址0开始存储、一次写入SDRAM器件的长度是64个数据,总共要写入256个数据。

当FIFO读模块离开复位状态后,系统自动将SDRAM器件的数据读出并缓存到FIFO读模块当中,从SDRAM器件的地址0开始读取数据。然后等待KEY2触发FIFO读操作。读操作是将缓存在FIFO读模块的数据一个一个取出并显示在数码管上。这里设定了一次读出SDRAM的长度是64个数据,总共要读出256个数据。

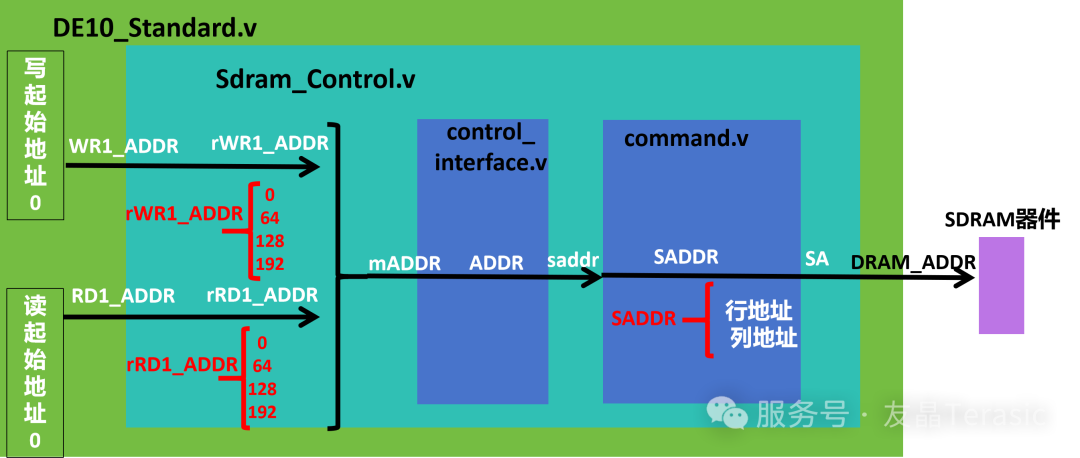

关于SDRAM读写地址的产生和控制可以参考下图:

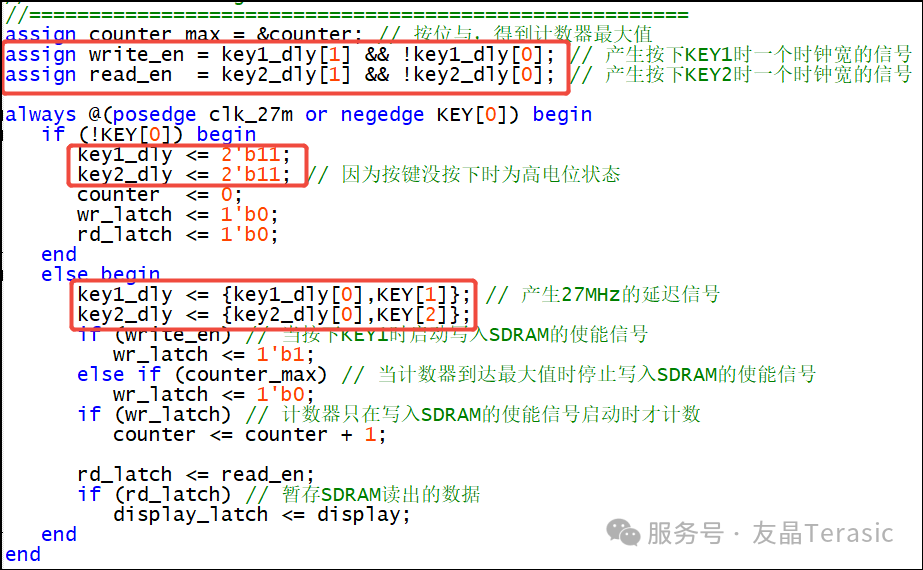

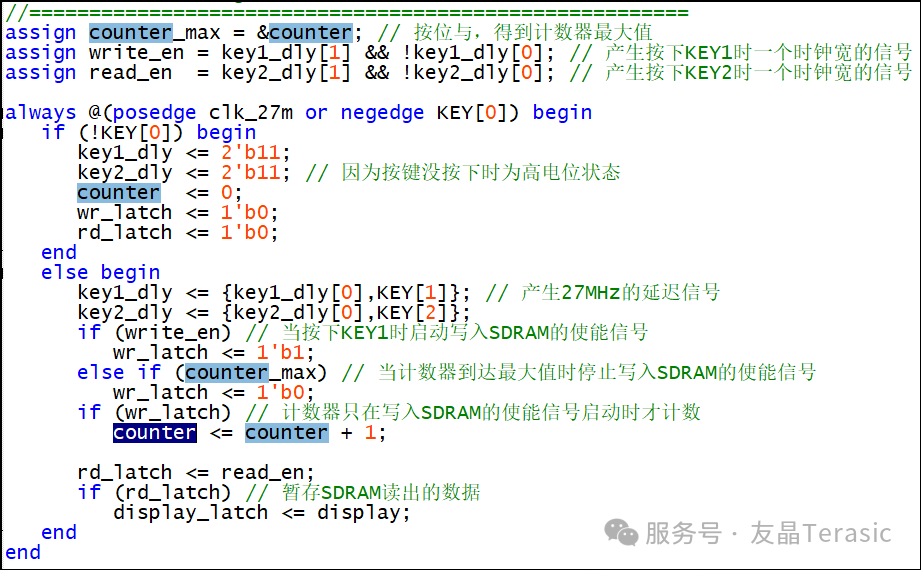

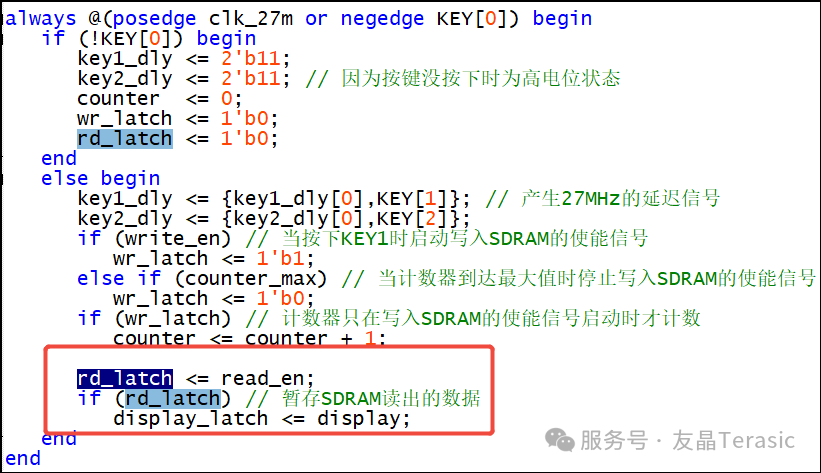

top文件对按键做了边沿捕获处理。延伸阅读:09-SDRAM控制器的设计——按键的处理(边沿捕获电路、硬件消抖、Verilog消抖)(后续发布)

系统通过计数器counter产生写入到FIFO写模块的数据0~255。

当系统检测到KEY1被按下时,counter从0开始计数。当这个计数器计数到最大值255时,计数器停止计数。counter产生的数据同时缓存到FIFO写模块内。

当计数器停止计数以后系统开始检测KEY2是否被按下,每按一次KEY2,暂存在FIFO读模块的数据就会被取出一个并送到数码管进行显示。

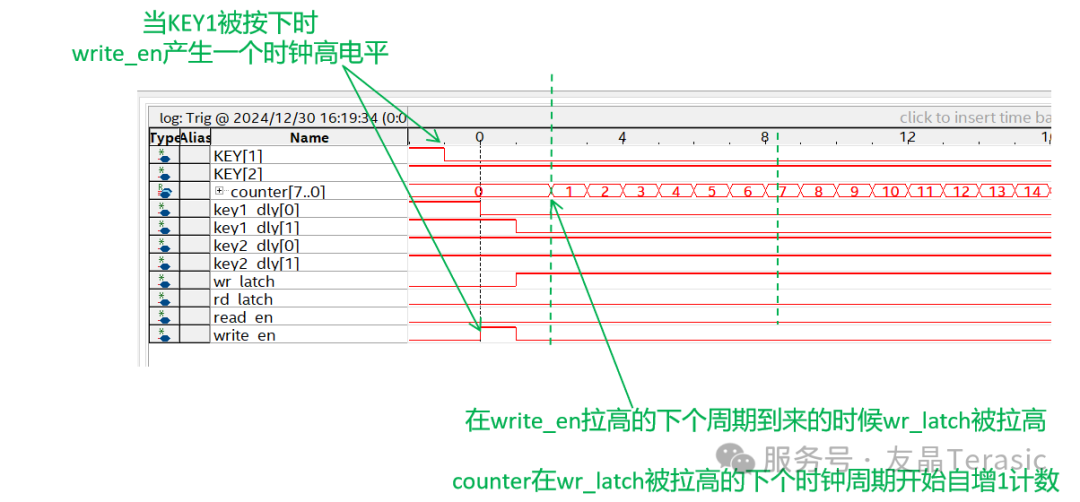

通过SignalTap波形我们可以看到,当KEY1被按下的时候,key1_dly检测到了下降沿,于是write_en产生一个时钟高电平(这里采样时钟也是27M),在下个周期到来的时候wr_latch被拉高,counter在wr_latch被拉高的下个时钟周期开始自增1计数。

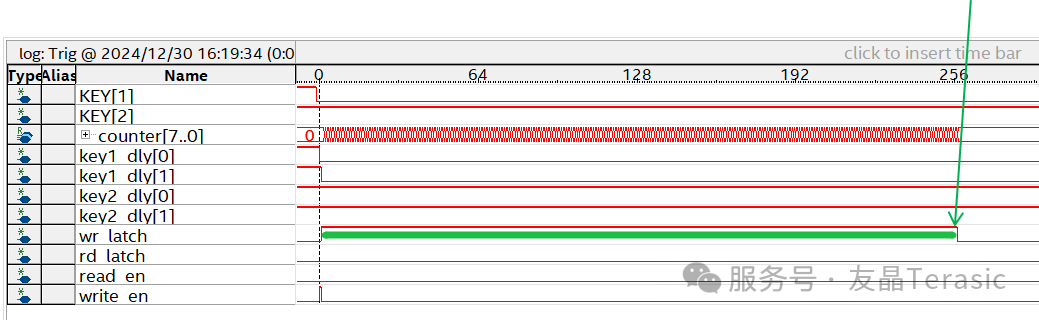

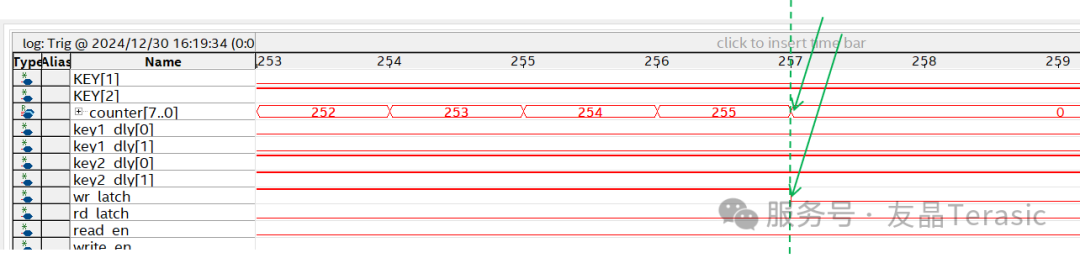

wr_latch信号在counter计数到最大值以后拉低。

counter计数到最大值放大以后的波形如下图:

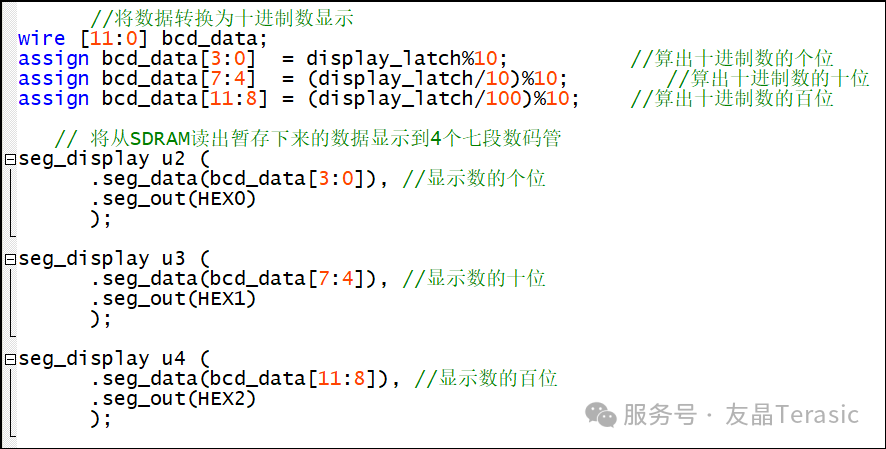

文件最后是数码管显示的处理。先将FIFO读模块里面取出的数据转换成能在数码管上以十进制显示的数字,然后再传递给数码管进行显示。数码管控制电路的延伸阅读:基于FPGA的贪吃蛇游戏设计(二)——数码管驱动模块

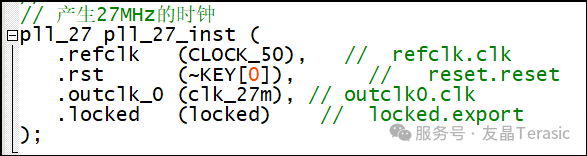

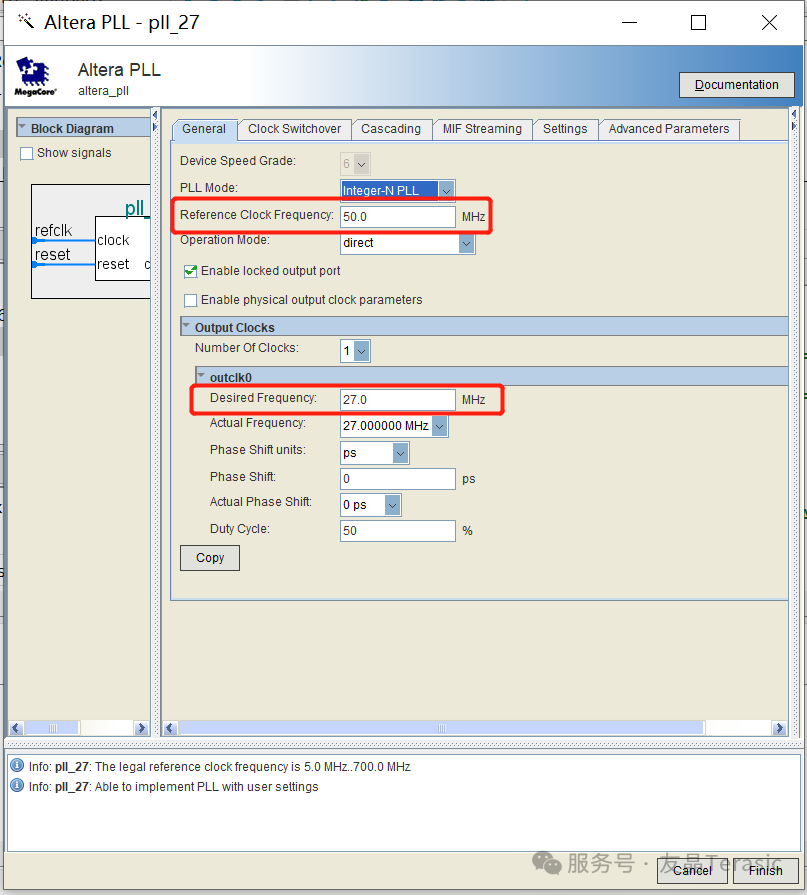

最后介绍一下时钟。本系统参考时钟是来自DE10-Standard板载50M时钟,经过PLL产生27M时钟输出给Top文件各个模块使用。PLL IP 复位是高电平有效。

pll_27界面设置如下:

PS:

本文的Signaltap波形图文件对应:

sdramcontrol\output_files\Sdram_Control.stptop.stp

往期阅读:

2288

2288

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?