前言▷▷▷

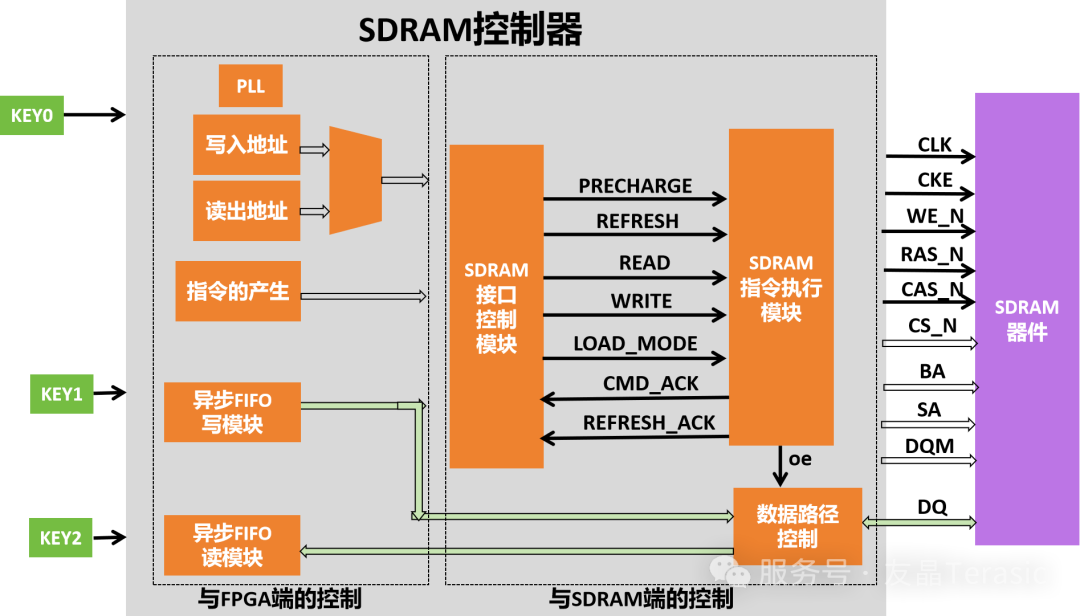

下图是本案例的功能框图。

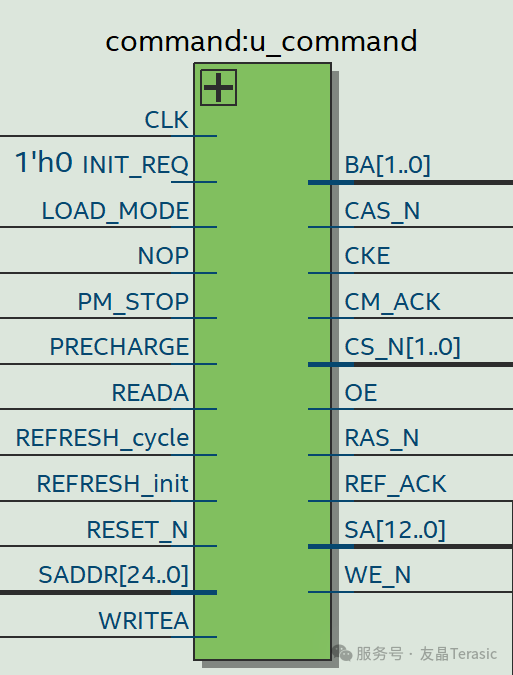

command.v文件对应图中SDRAM指令执行模块,它会从SDRAM接口控制模块接收指令,然后产生控制信号直接输出到SDRAM器件来完成所接收指令的动作。如下是该模块的RTL视图:

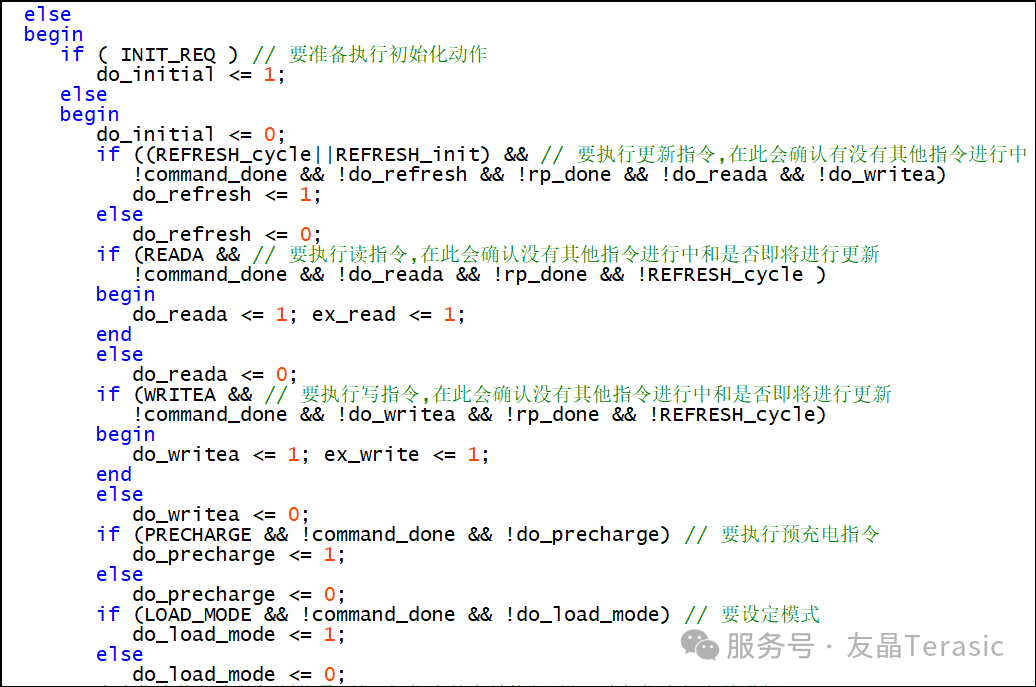

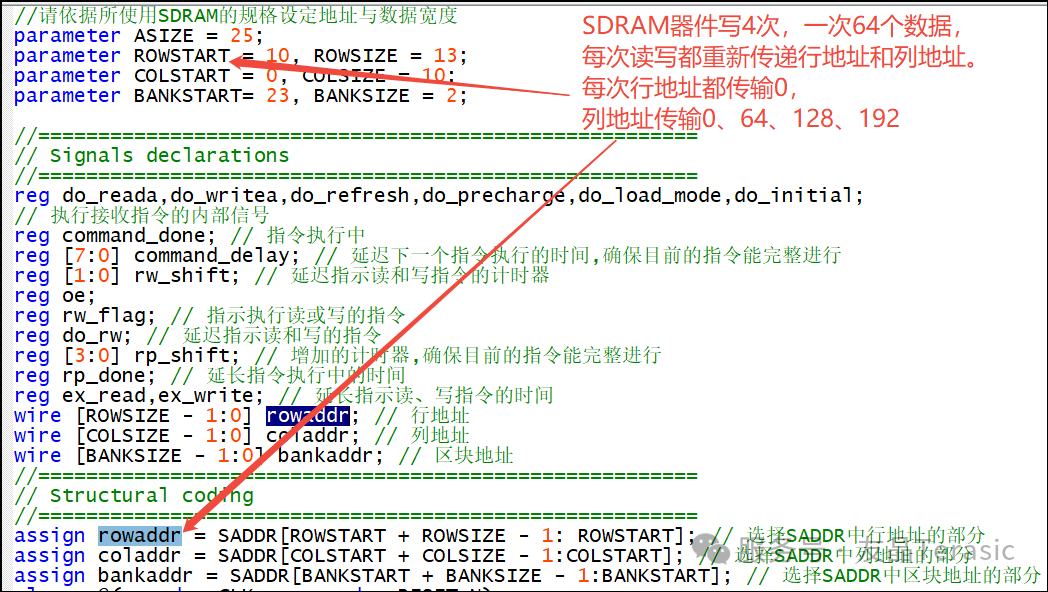

其具体代码讲解如下:

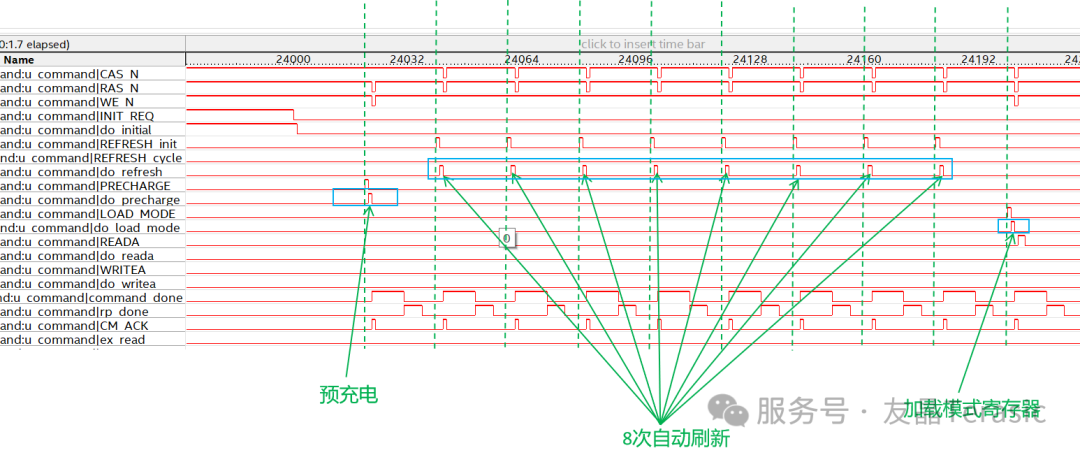

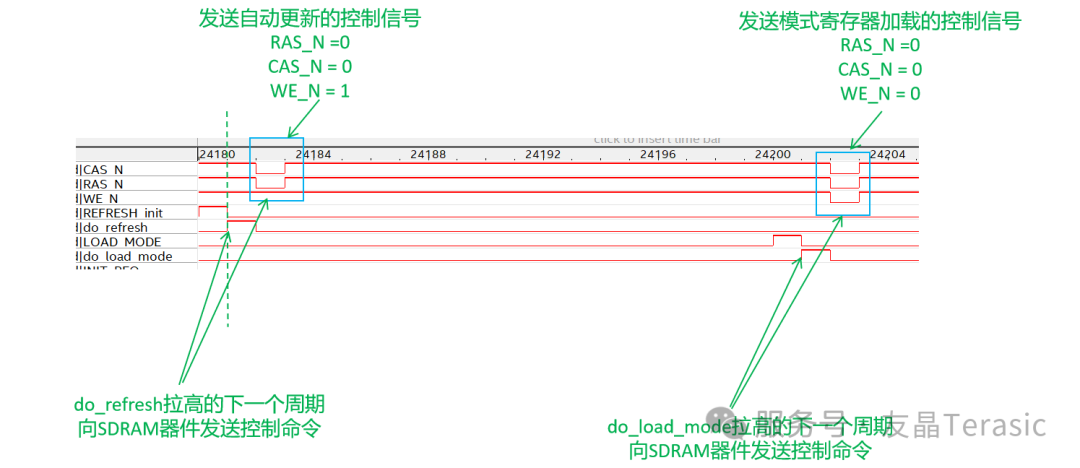

输入信号INIT_REQ指示的是SDRAM上电等待的24000个时钟周期,在这期间do_initial信号为高,系统只能发送NOP命令。

当初始化等待时间结束do_initial被拉低,首先确认在没有其他指令进行中时,若有刷新请求,则do_refresh信号拉高。

然后确认在没有其他指令进行中时,有读请求时,do_reada信号拉高。

然后确认在没有其他指令进行中时,有写请求时,do_writea信号拉高。

然后确认在没有其他指令进行中时,有预充电请求时,do_precharge信号拉高。

然后确认在没有其他指令进行中时,有模式寄存器加载请求时,do_load_mode信号拉高。

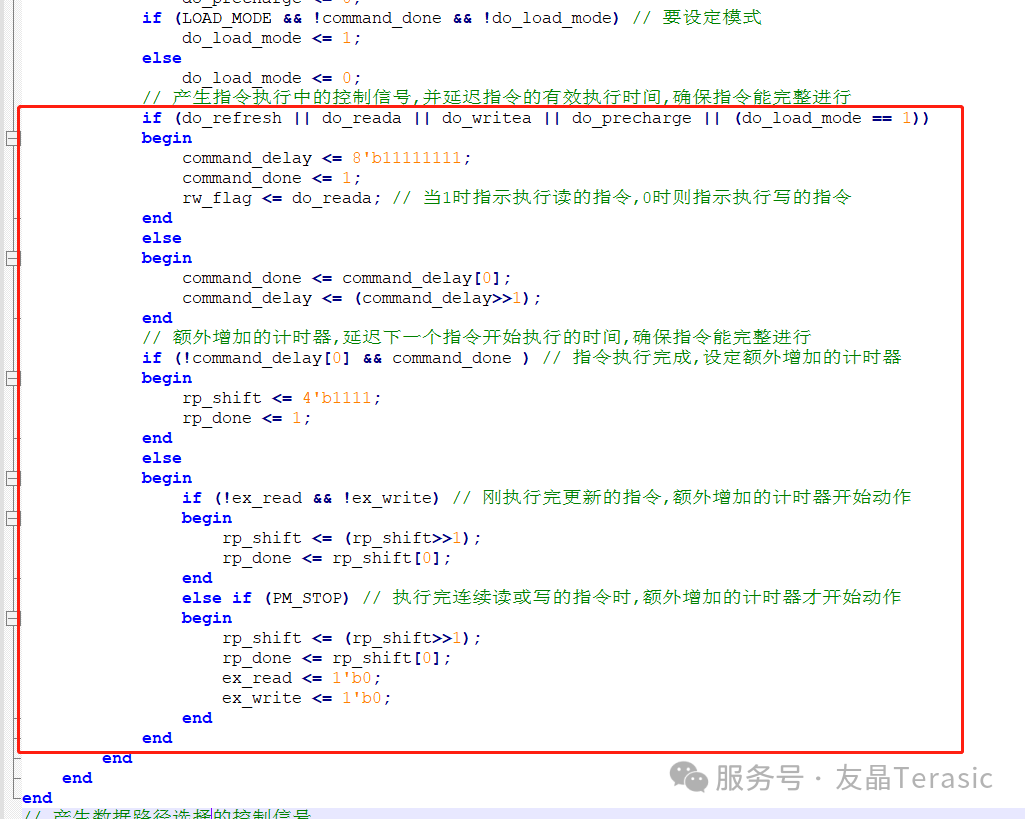

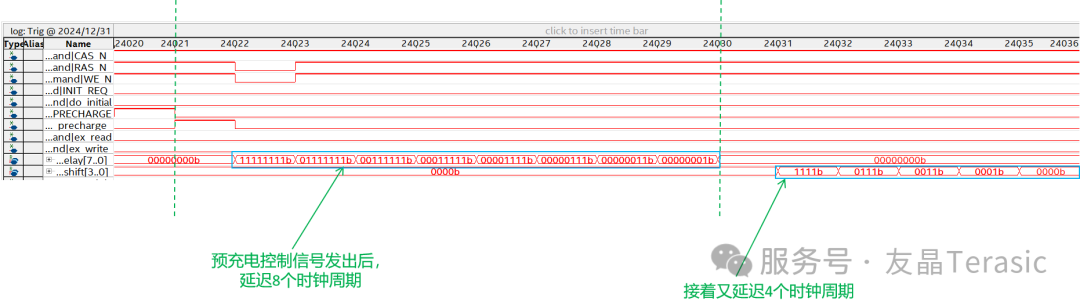

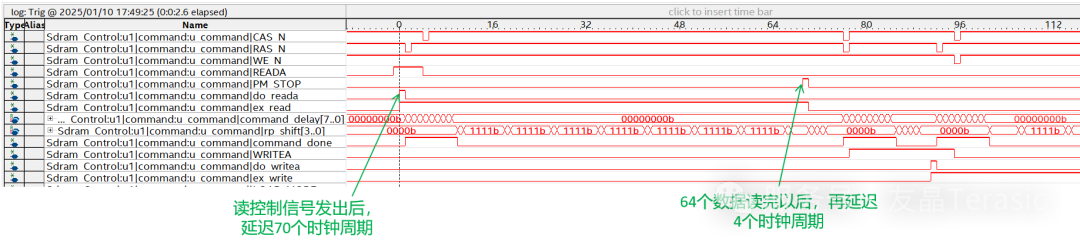

当产生自动刷新命令、读写命令、预充电命令和模式加载命令时,系统会通过command_delay来延迟指令的有效执行时间,确保指令能完整进行。除开突发读/写的情况,其他每个指令统一延迟8个时钟周期后再延迟4个周期。

拿预充电命令举例:

读写命令则是等待64个数据连续读/写完后,再延迟4个时钟周期。拿读命令举例:

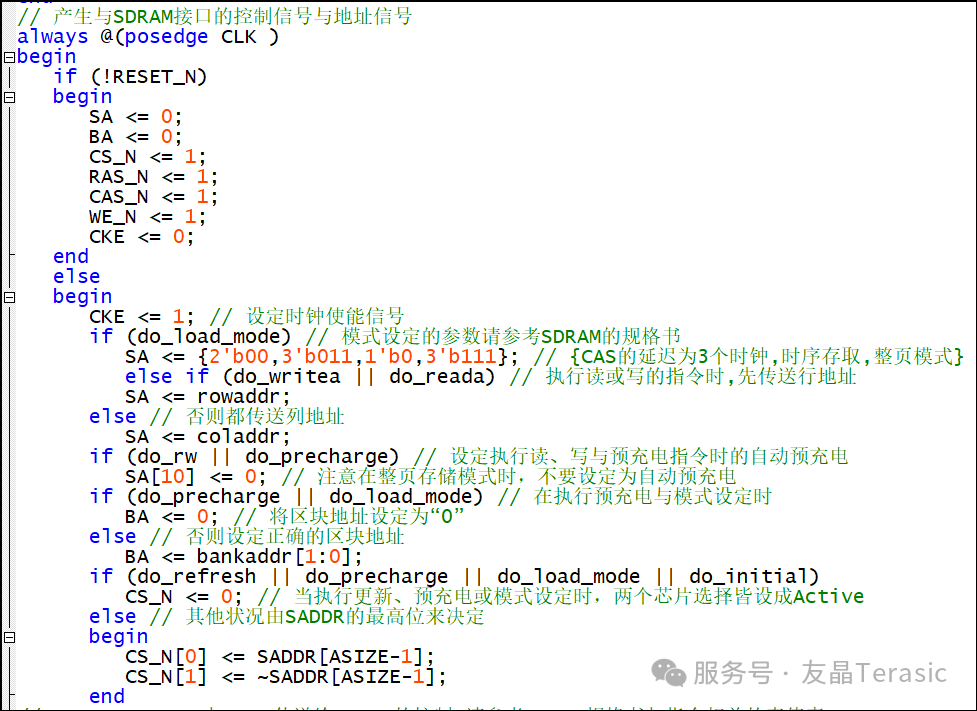

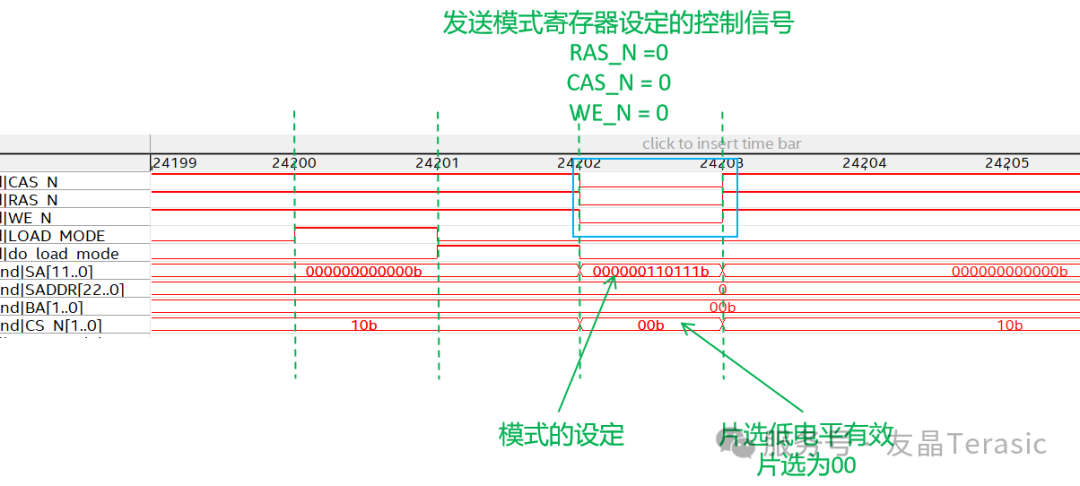

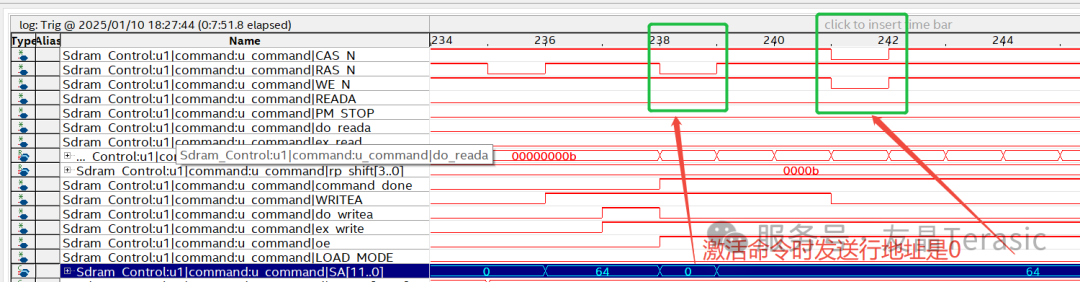

下面是地址端口、bank选择和片选信号的处理。在初始化状态,加载模式寄存器时是通过地址端口对寄存器进行赋值的。在激活操作时,地址端口发送行地址;在读或者写操作时,地址端口发送列地址。

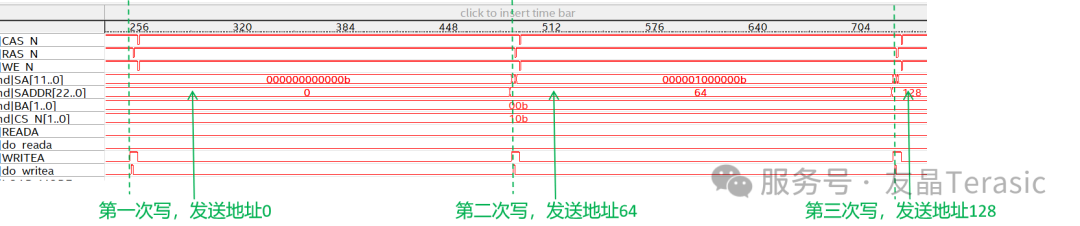

command.v 模块里面得到行地址rowaddr和列地址coladdr:

放大地址线SA波形可以看到,在行激活的时候发送的地址确实是0:

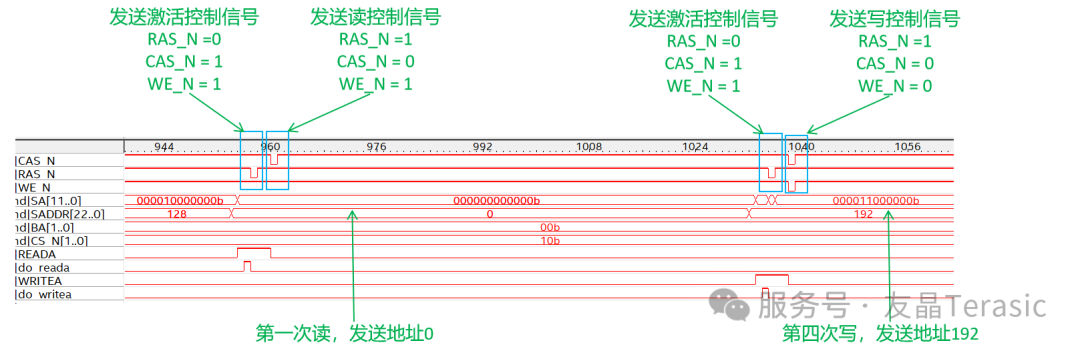

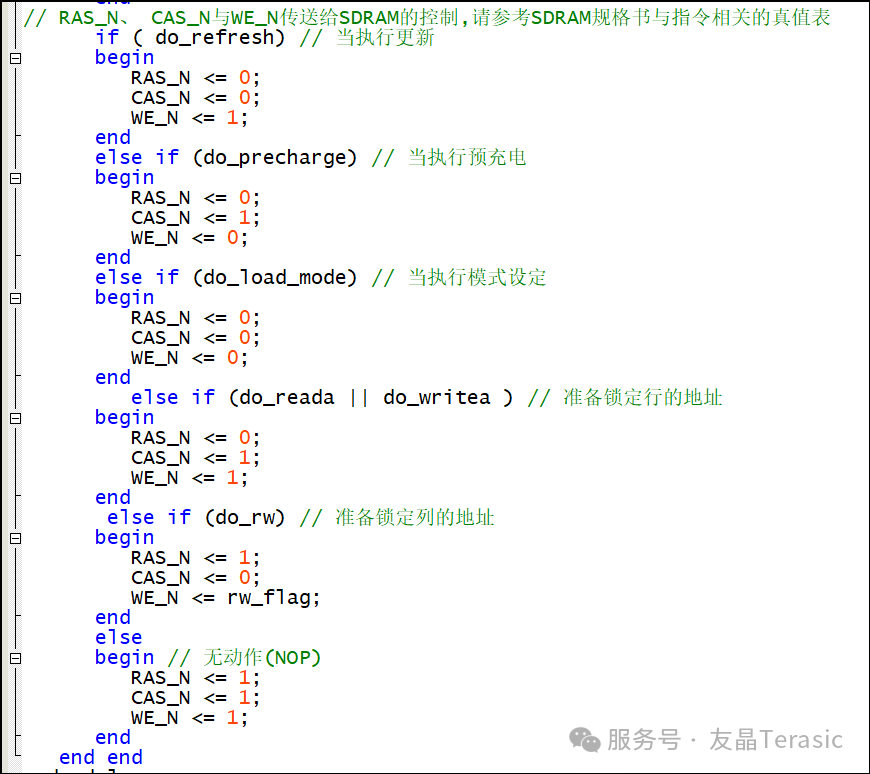

下面是RAS_N、CAS_N、WE_N信号的产生。

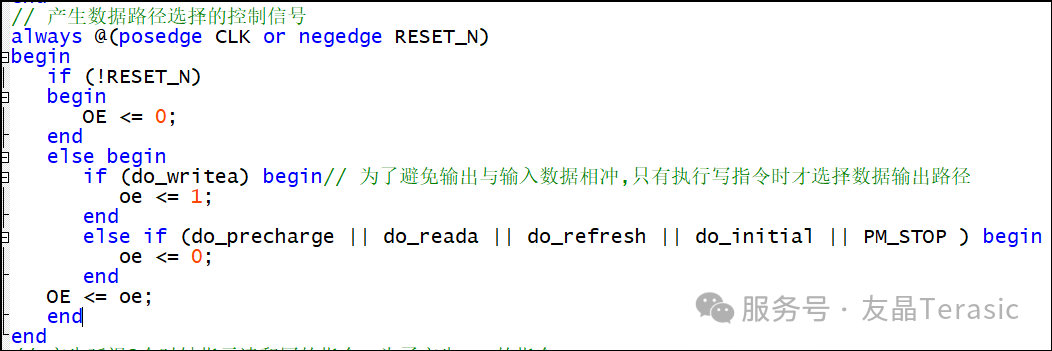

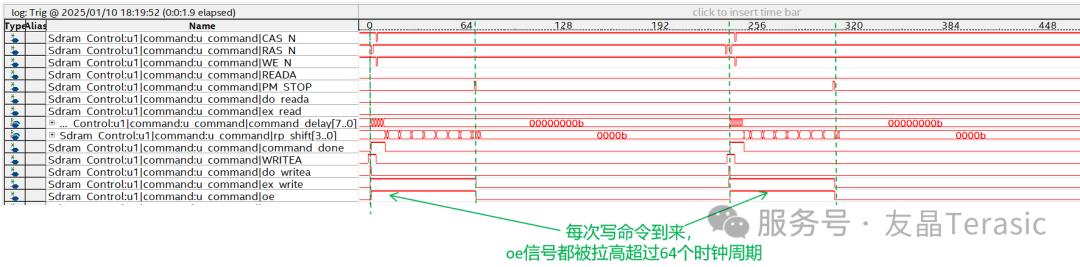

因为写入 SDRAM 的数据与从 SDRAM 读出的数据为共用传输引脚,为避免存取数据相冲,系统里设计了一个三态门电路(三态门电路的设计参考07-SDRAM控制器的设计——Sdram_Control.v代码解析(后续发布),通过oe信号控制SDRAM 数据接口的输入和输出。oe信号的设计如下:

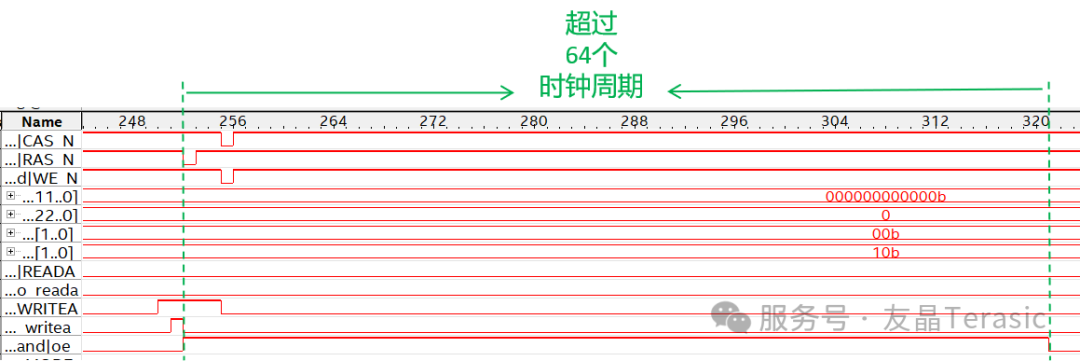

每次oe信号拉高超过64个时钟周期,确保数据被正确写入到SDRAM器件当中:

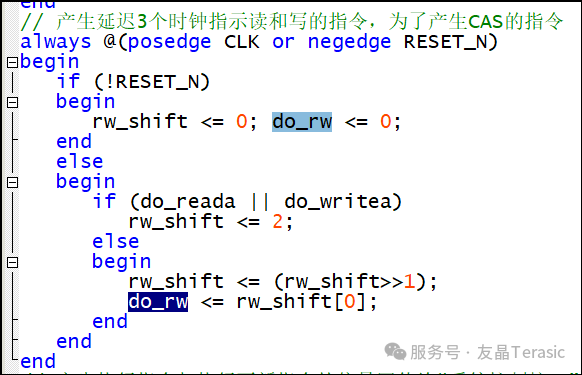

另外,读命令和写命令之前要先有激活命令,读写命令在激活命令的3个周期后发出,所以这里用个右移计数器计数3个周期:

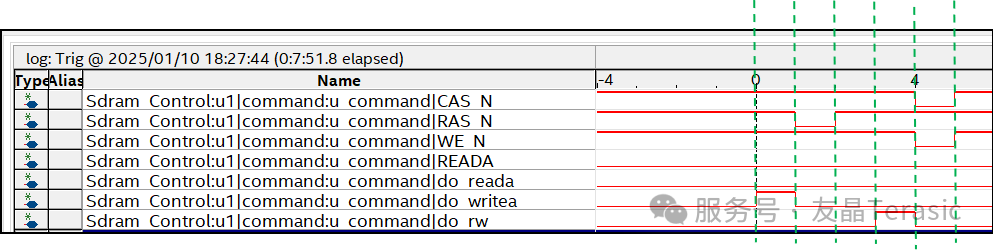

do_wr信号波形如下:

PS: 本文波形来自文件~\sdramcontrol\output_files\command.stp。

往期阅读:

01-SDRAM控制器的设计——案例总概述

02-SDRAM控制器的设计——SDRAM简介

03-SDRAM控制器的设计——解读IS42R16320D的数据手册

04-SDRAM控制器的设计——control_interface.v代码解析

06-SDRAM控制器的设计——异步FIFO的调用

07-SDRAM控制器的设计——Sdram_Control.v代码解析

08-SDRAM控制器的设计——top文件代码解析

09-SDRAM控制器的设计——按键的处理(边沿捕获电路、硬件消抖、Verilog消抖电路)

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?