module端口如下:

module trig_gen

(

input clk,

input rst,

//

input [31:0] cfg_trg_time_high,

input [31:0] cfg_trg_time_low,

//

input trig_en,

//

output reg trig_out,

output trig_done,

output reg trig_rdy

);

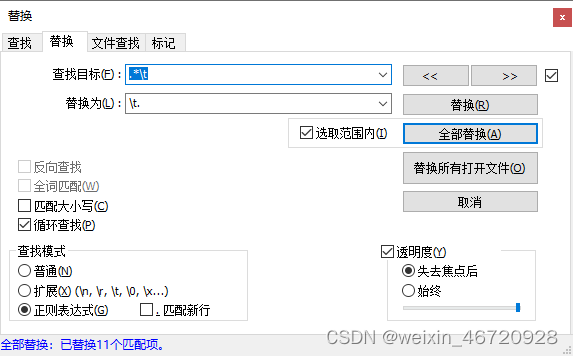

使用正则表达式搜索替换

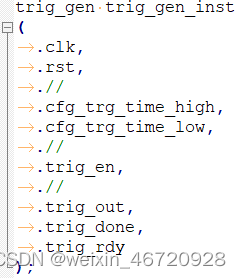

替换后,变为端口例化形式:

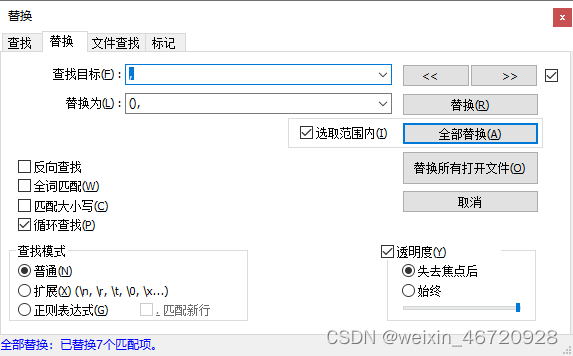

再使用普通查找模式,搜索替换把行尾的,替换为(),

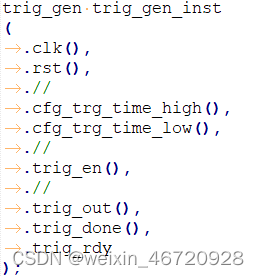

替换后:

本文介绍了如何将模块`moduletrig_gen`的端口进行处理,包括使用正则表达式将其转换为例化形式,并在行尾添加括号。主要关注输入和输出信号以及转换过程。

本文介绍了如何将模块`moduletrig_gen`的端口进行处理,包括使用正则表达式将其转换为例化形式,并在行尾添加括号。主要关注输入和输出信号以及转换过程。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?