目录

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

参考资料:

TMS320F280025的时钟_tms320f280025开发资料-优快云博客

DSP28377s系统时钟配置注意事项 - 大风当歌 - 博客园 (cnblogs.com)

DSP28335 时钟、外设及寄存器配置_dsp寄存器配置-优快云博客

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

锁相环电路PLL

关于DSP系统时钟的一些理解_dsp cpu cal-优快云博客

“锁相环主要作用是通过软件实时地配置片上外设时钟,提高系统的灵活性和可靠性。

PLL电路,就是锁相环电路(Phase-Locked Loop)。 是一种控制晶振使其相对于参考信号保持恒定的电路,电路通过比较复杂的原理可以将低频信号进行倍频与分频处理。

F28335的工作最高频率为150MHz,而一般在电路设计中,一般采用的晶振频率为30MHz。之所以不直接采用150MHz晶振,一方面是价格高昂,另一方面还要对电路做EMI处理。因此,为了让DSP能够工作在最高频率,需要对晶振信号频率进行5倍频处理。通常采用的方案是通过PLL电路先进行10倍频处理,再2分频处理。”

时钟树

DSP28335 时钟、外设及寄存器配置_dsp寄存器配置-优快云博客

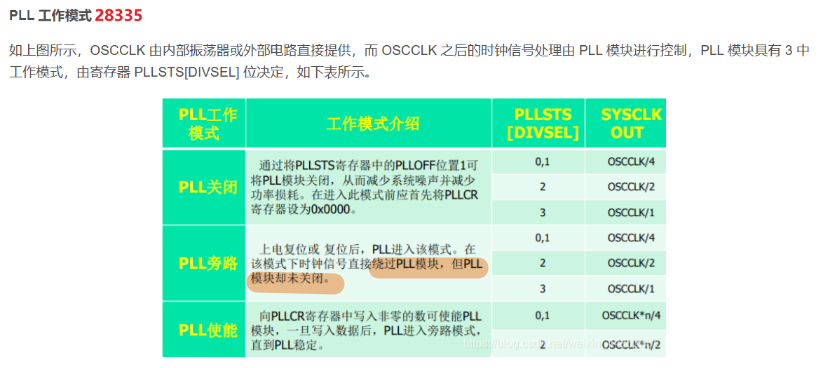

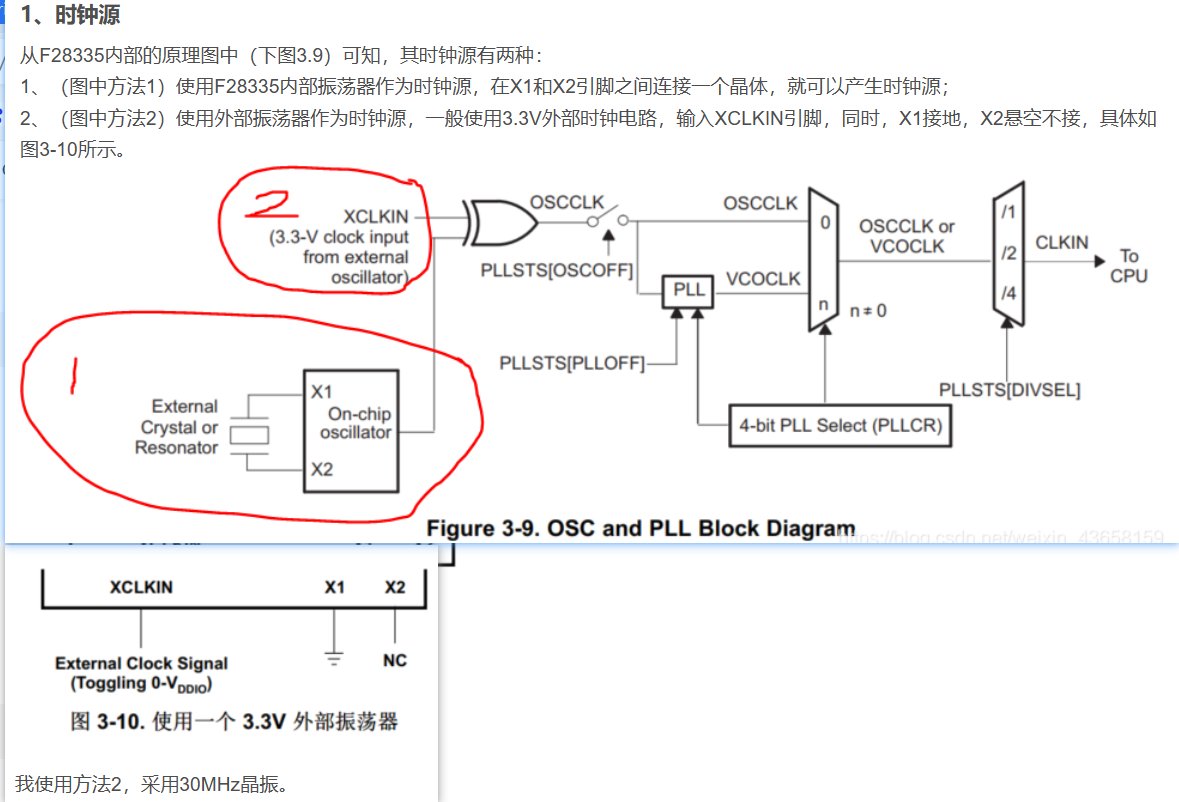

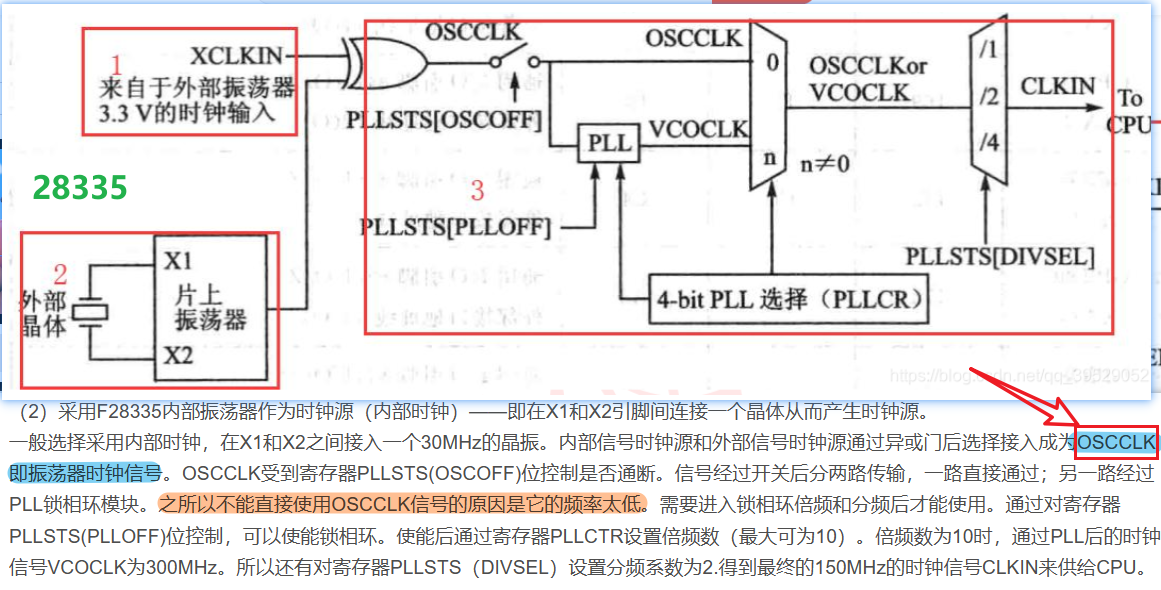

“28335时钟产生过程:外部时钟或者外部晶振给F28335提供时钟源OSCCLK,使能F28335片上PLL电路,PLL电路对时钟源信号进行倍频,产生时钟CLKIN,CLKIN通过CPU产生时钟SYSCLKOUT,SYSCLKOUT经过分频可以产生低速时钟LOSPCLK和高速时钟HISPCLK,最后OSCCLK、CLKIN、SYSCLKOUT、LOSPCLK和HISPCLK给各个模块提供时钟。”

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

TMS320F280025的时钟_tms320f280025开发资料-优快云博客

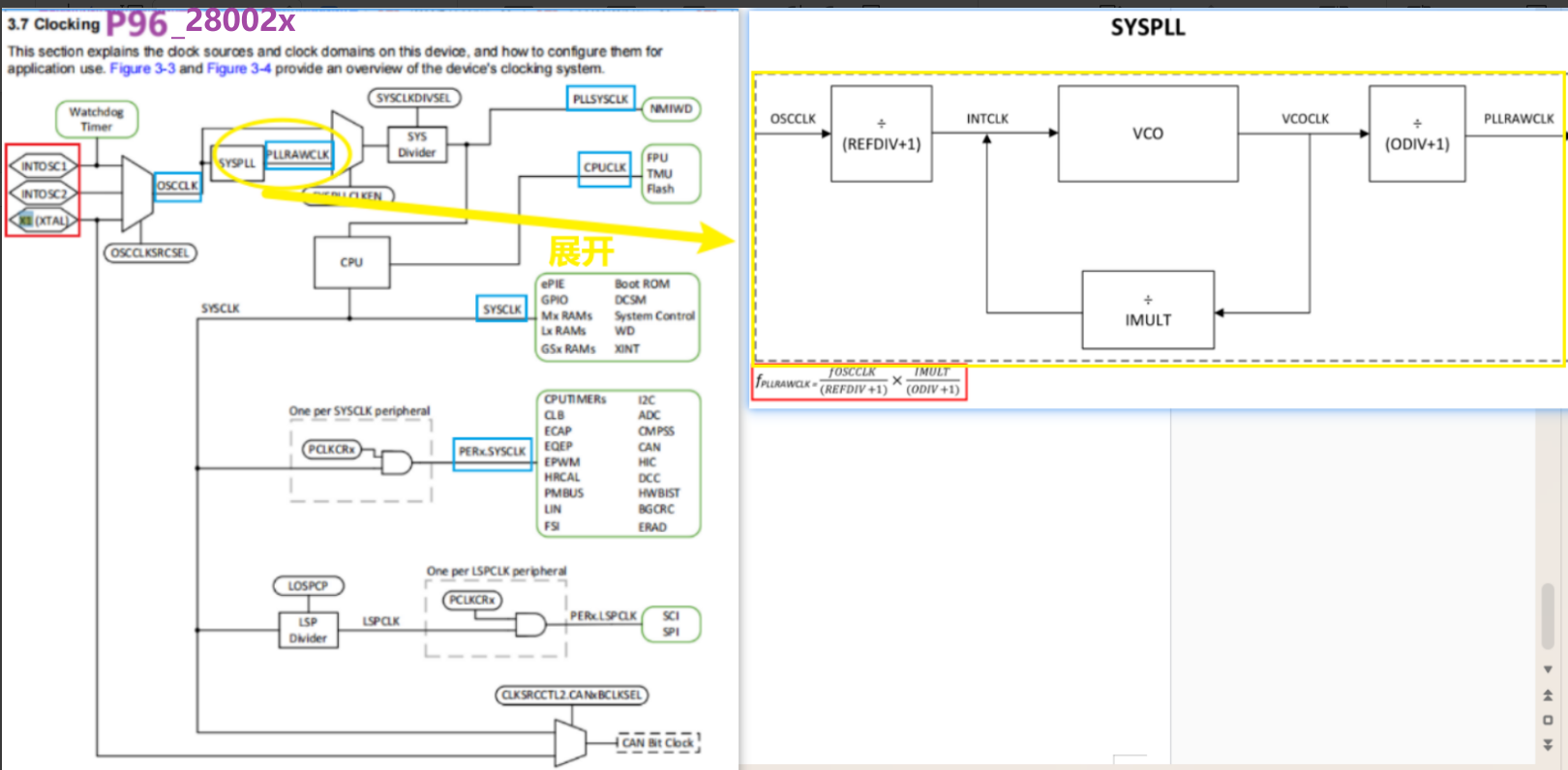

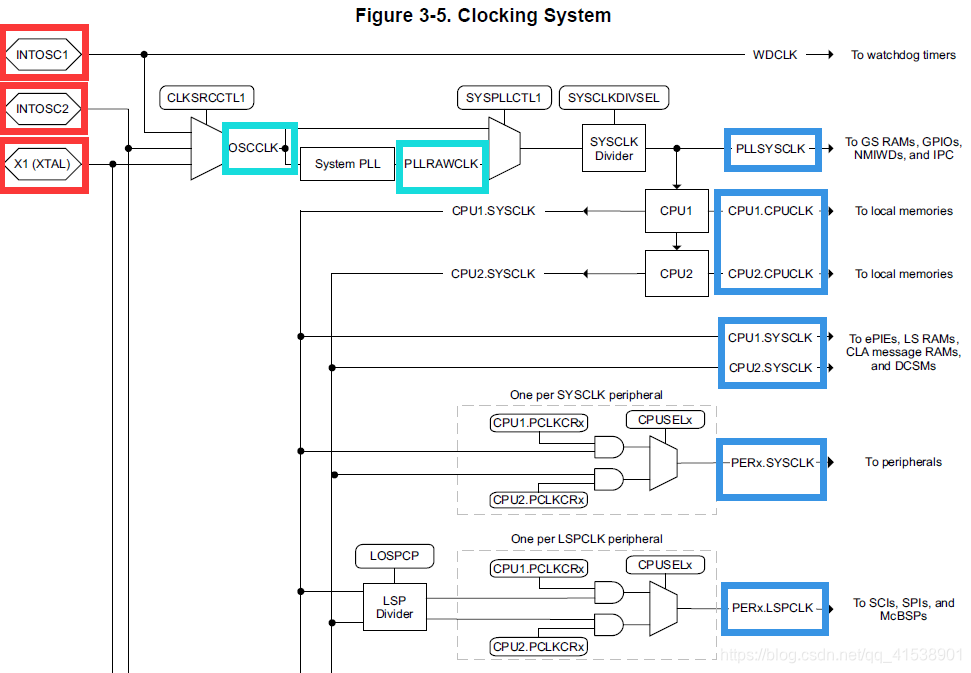

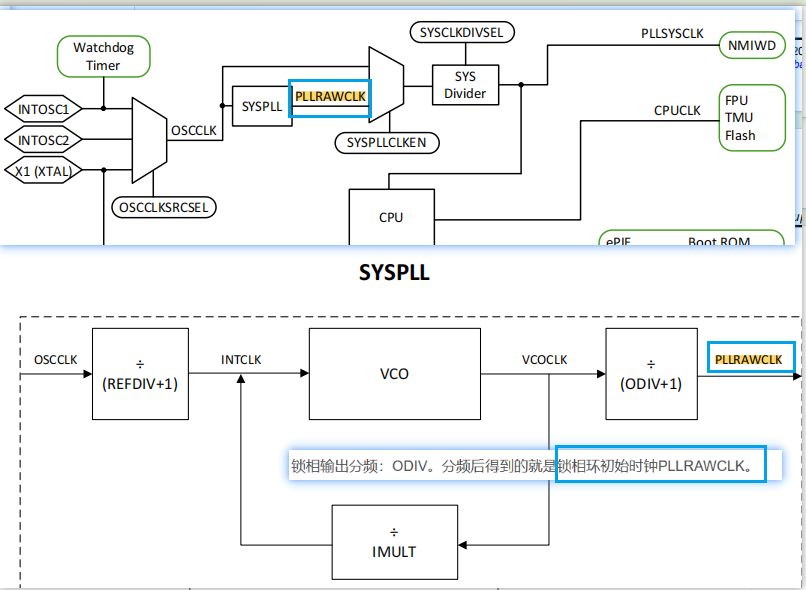

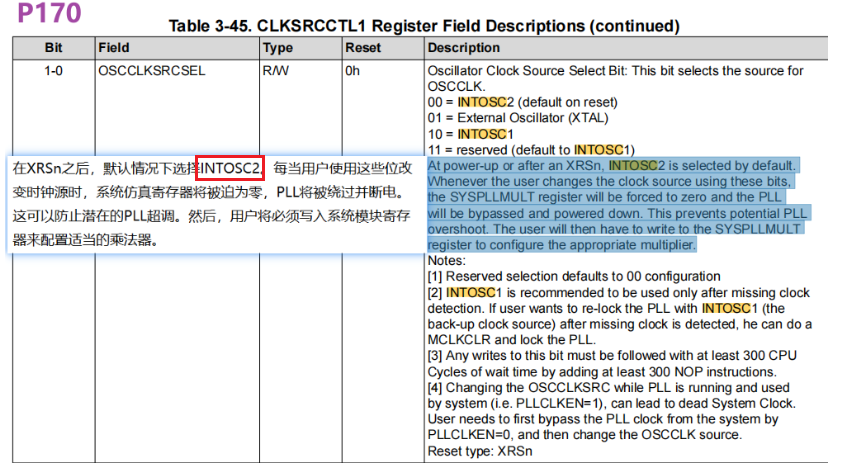

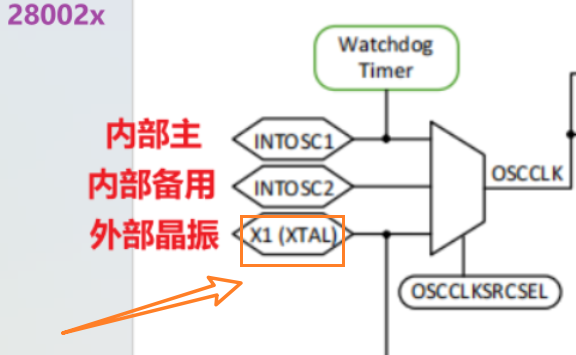

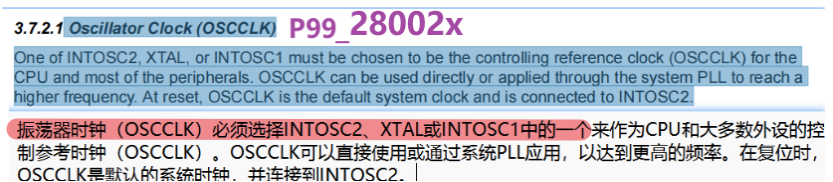

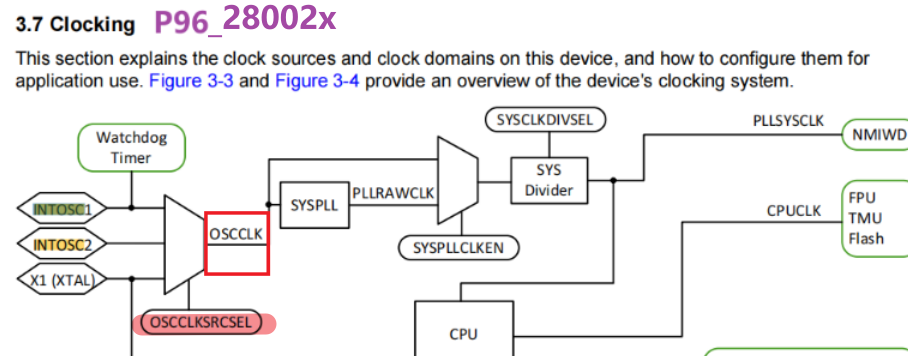

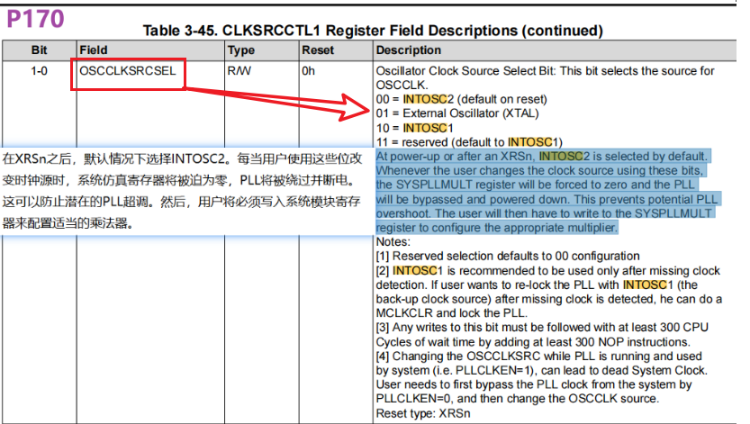

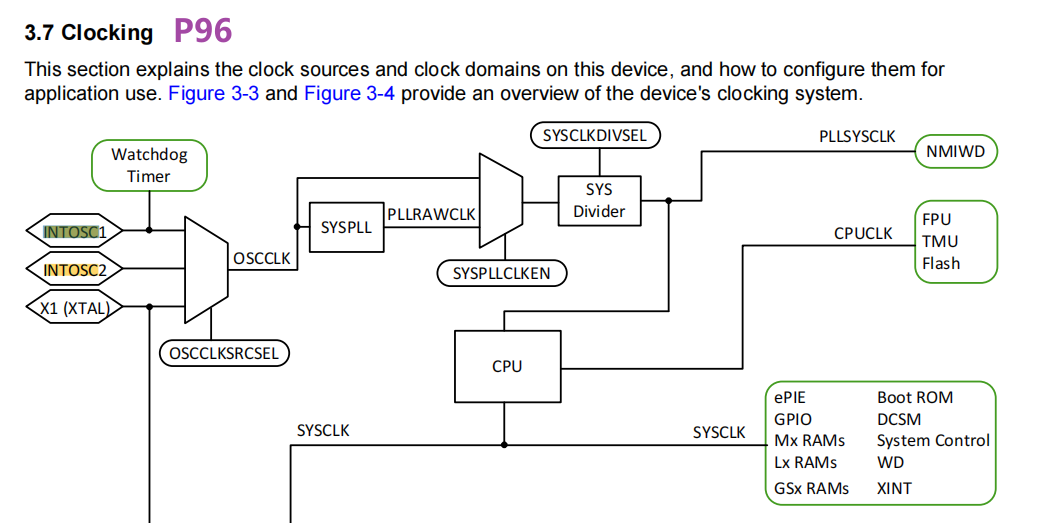

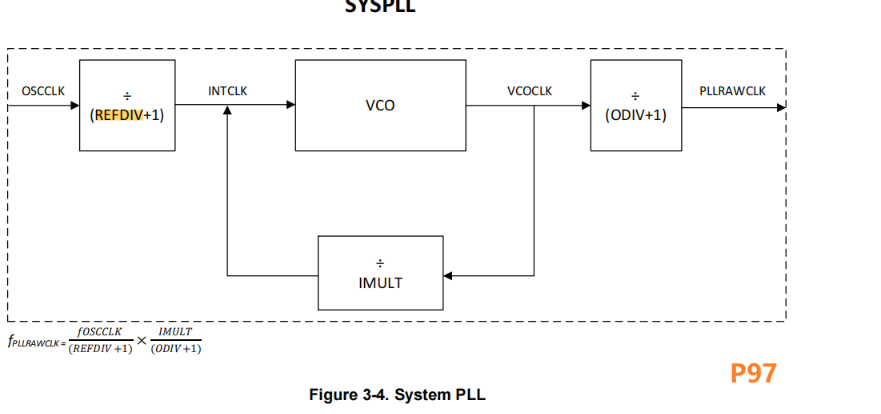

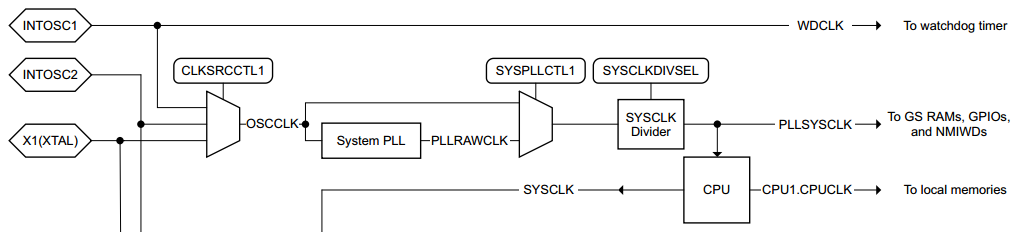

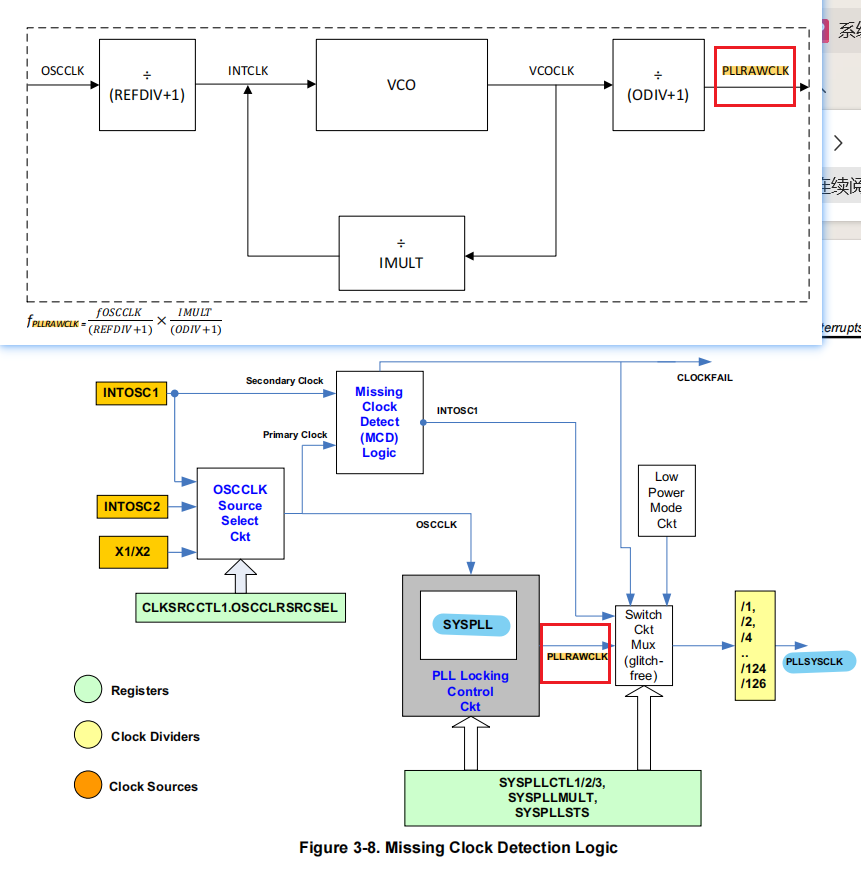

时钟源:参考时钟为OSCCLK。根据OSCCLKSRCSEL寄存器来从内部时钟源1(INTOSC1)、内部时钟源2(INTOSC2)、外部时钟(XTAL)中三选一。

参考时钟分频:REFDIV。分频后得到锁相环内部时钟(INTCLK)。

电压控制振荡器(VCO):得到VCOCLK。

VCO分频IMULT与反馈给INTCLK同步跟踪。稳定后,VCOCLK=INTCLK*IMULT。

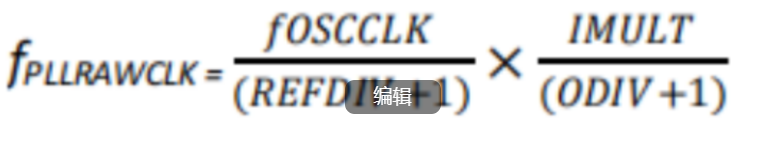

锁相输出分频:ODIV。分频后得到的就是锁相环初始时钟PLLRAWCLK。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

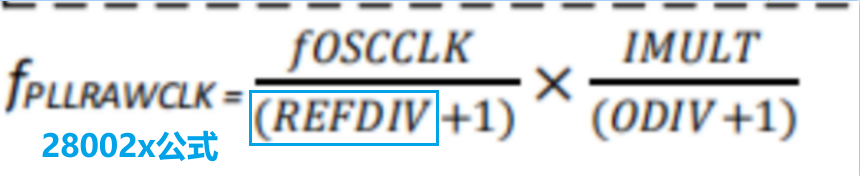

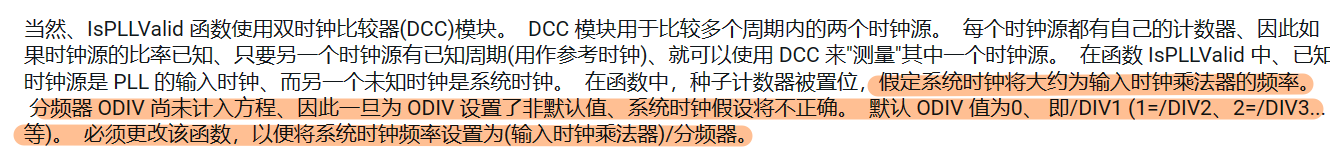

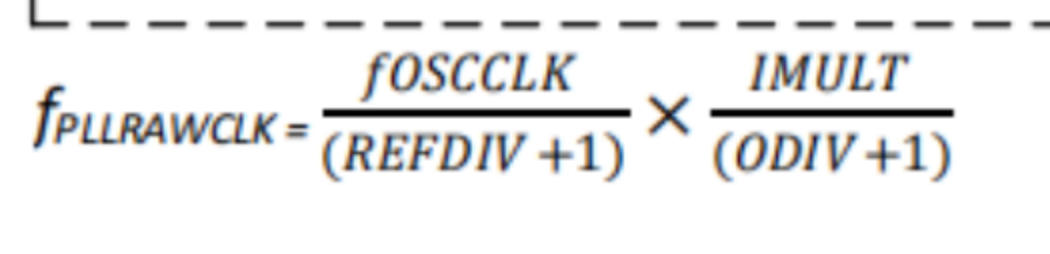

计算时钟公式

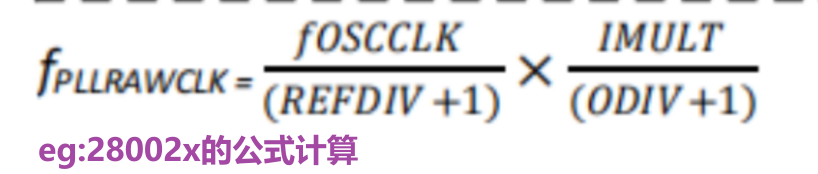

找到用户指南里的计算公式,不同芯片计算公式不一样。

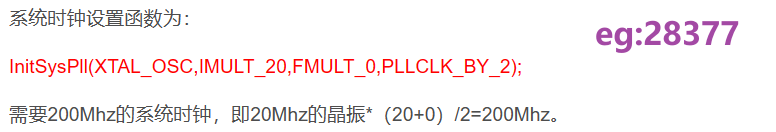

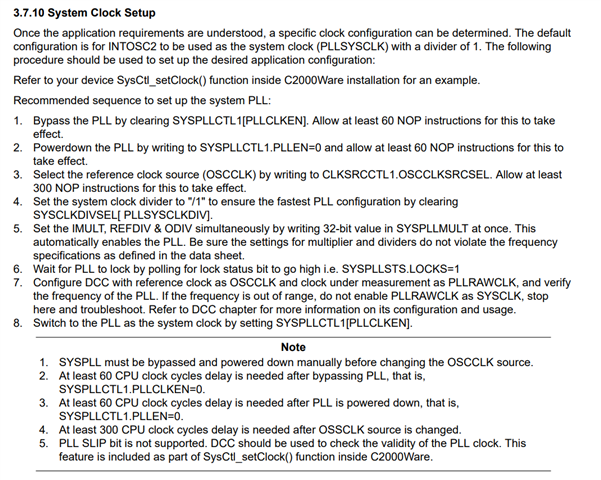

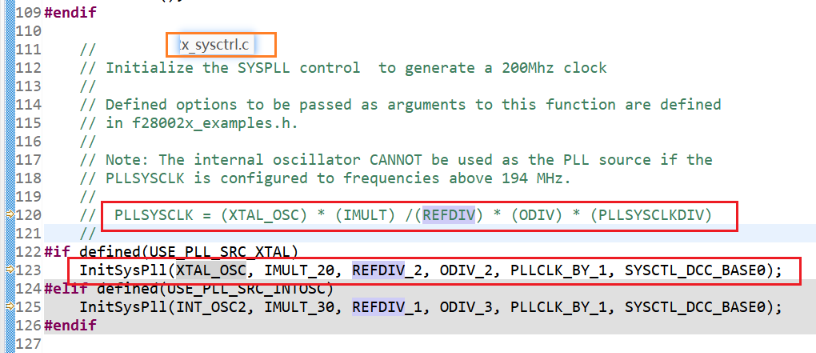

系统时钟设置函数

InitSysPll(XTAL_OSC,IMULT_20,FMULT_0,PLLCLK_BY_2);

此公式可在TI模板工程的Fxxxx_SysCtrl.C文件中找到。系统时钟可以用来LSPCLK、SPI、I2C、MCBSP 这些串口通信协议。

.......................................................................................................................................................

.......................................................................................................................................................

.......................................................................................................................................................

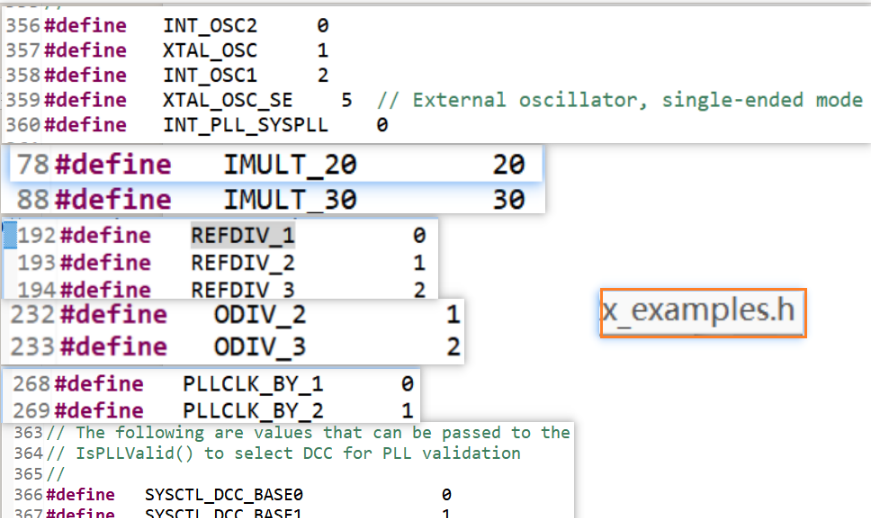

XTAL_OSC外部时钟源、 INT_OSC2内部时钟源

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

TMS320F280049C 学习笔记4 Led_ex1_blinky 初始化函数及系统时钟_device_delay_us 需关中断-优快云博客

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

- 。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

- 。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

分频PLLCLK_BY_x

eg: 28377

主控板用20MHz外部晶振,为取200MHz系统时钟,倍频设为20,分频设为2,这样sysclock = 20MHz * 20 / 2,正好200MHz。具体调用TI公司的库函数,实现代码是这样的:InitSysPll(XTAL_OSC,IMULT_20,FMULT_0,PLLCLK_BY_2);

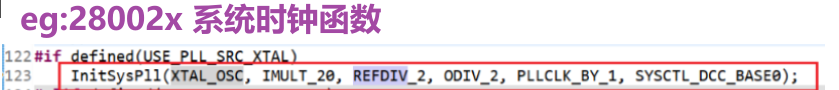

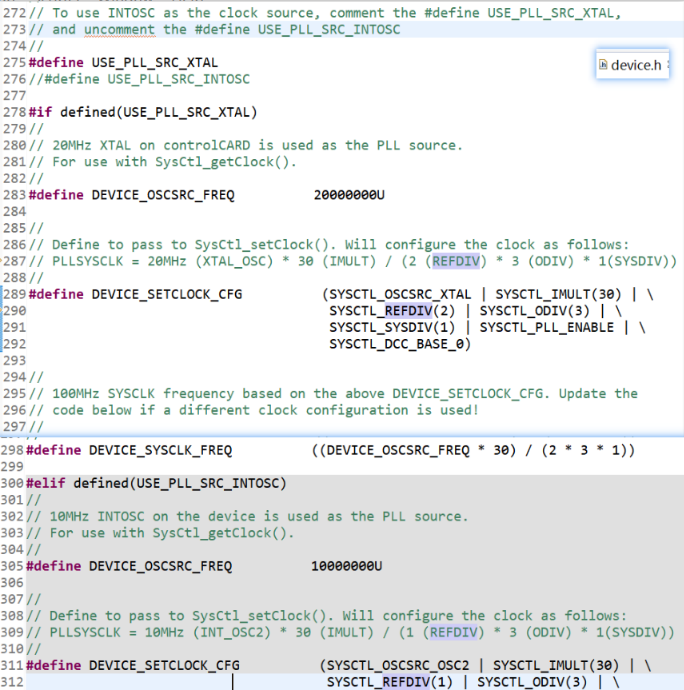

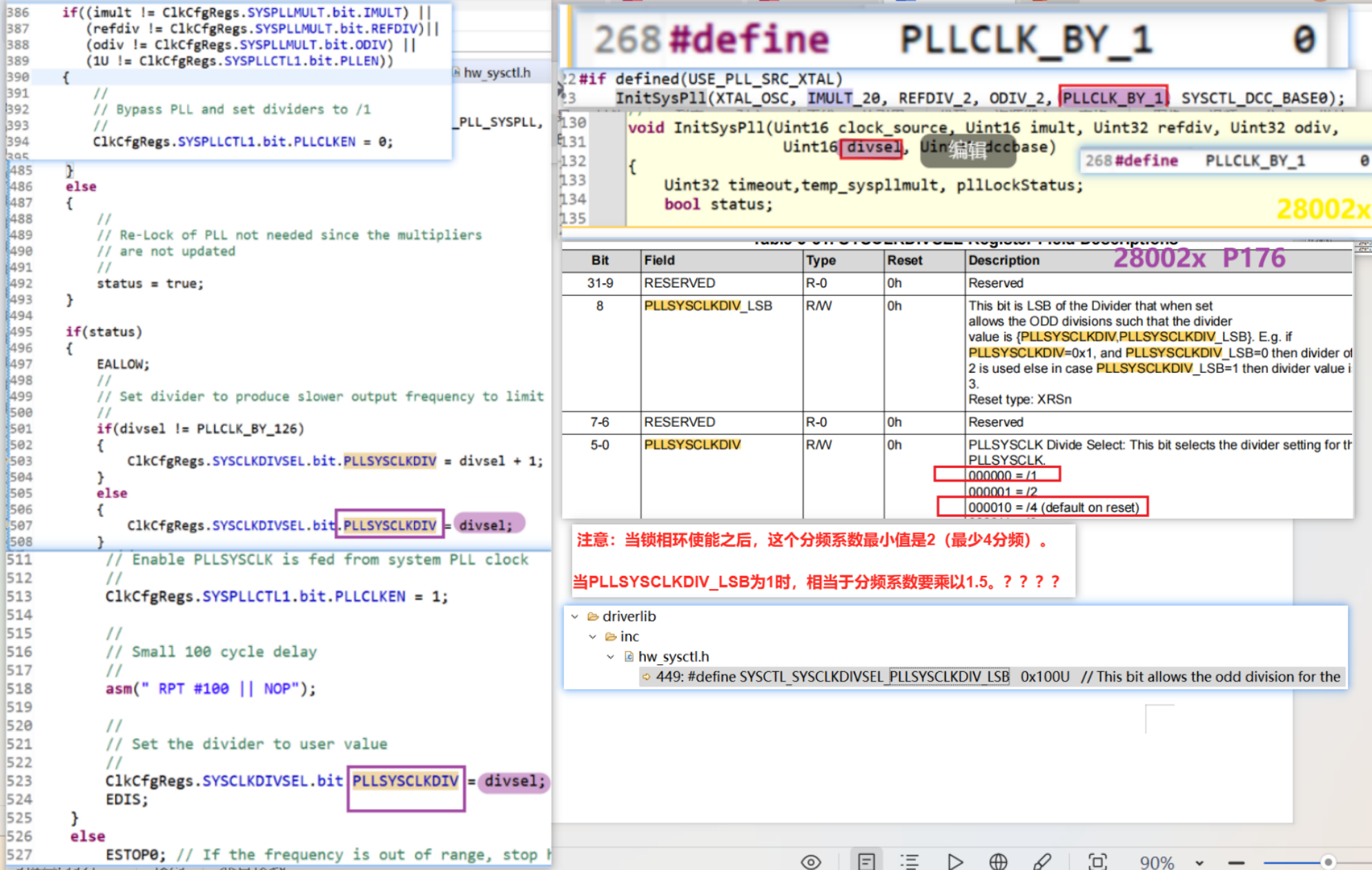

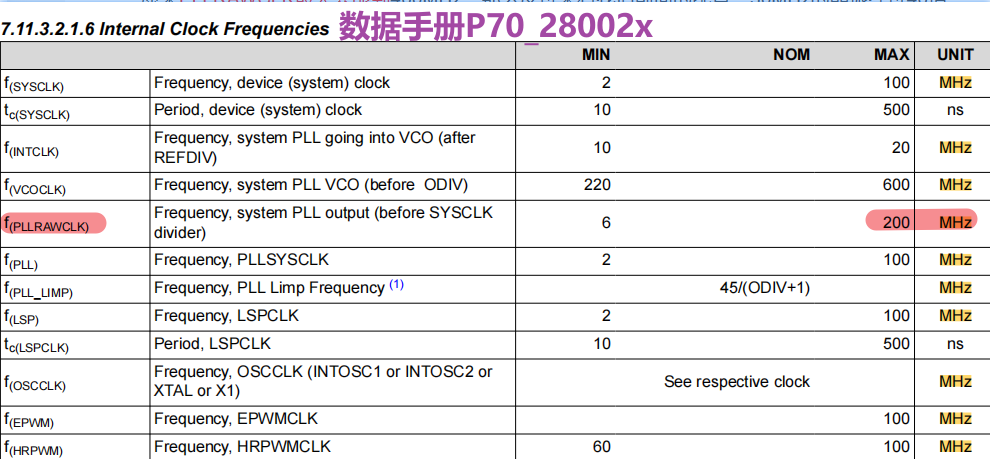

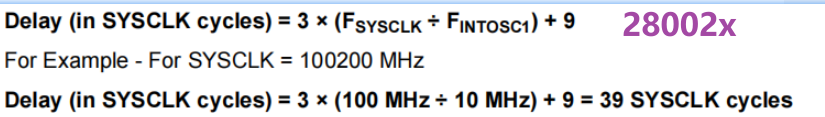

eg: 28002x

主控板用20MHz外部晶振,为取100MHz系统时钟,具体调用TI公司的库函数,实现代码是这样的:InitSysPll(XTAL_OSC,IMULT_20,REFDIV_2,PLLCLK_BY_1,SYSCTL_DCC_BASE_0);

(20Mhz*20)/[ (1+1)*(1+1)]=100Mhz. ( 详细计算见 “实例计算28002x”)

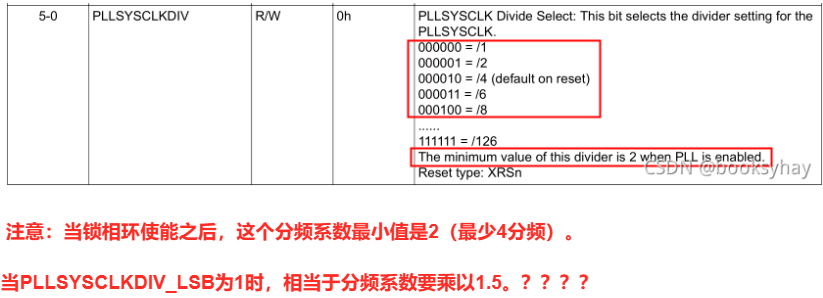

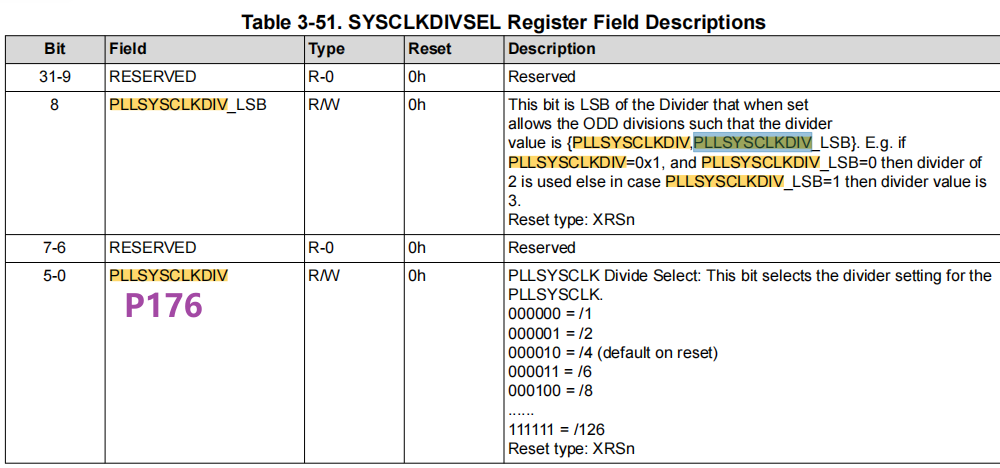

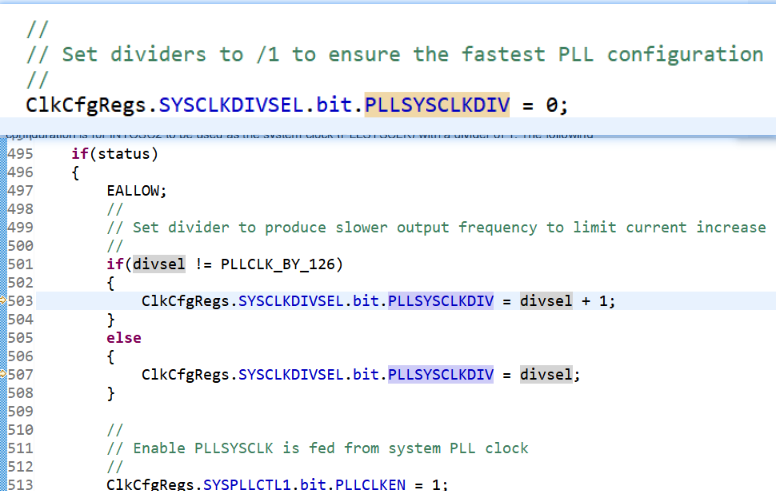

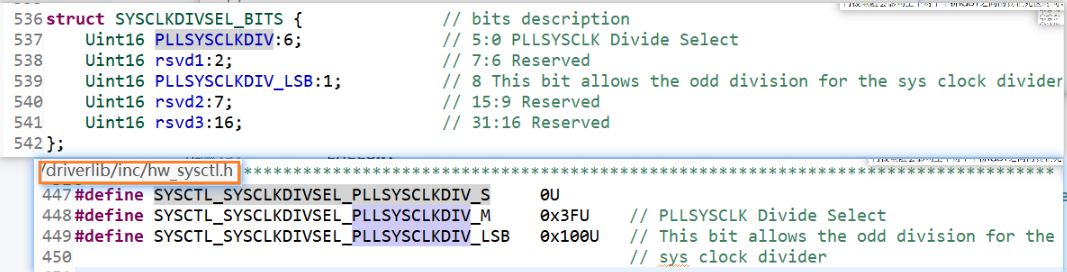

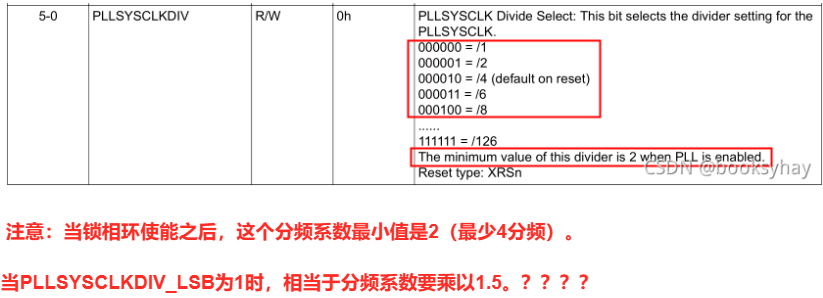

PLLSYSCLKDIV?

PLLSYSCLKDIV:锁相环分频系数

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

TMS320F280025的时钟_tms320f280025开发资料-优快云博客

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

PLLRAWCLK 、PLLSYSCLK

锁相输出分频,ODIV,分频后得到的就是锁相环初始时钟PLLRAWCLK。

28002x用户指南:

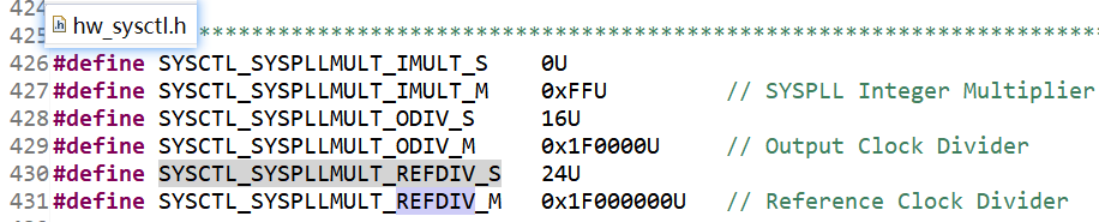

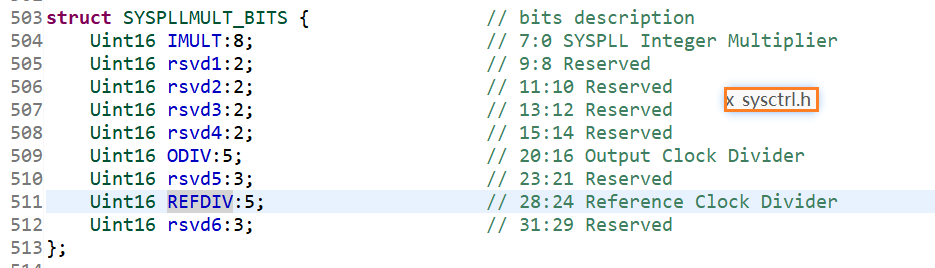

REFDIV

分频器系数用REFDIV表示。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

.............................................................................................................................................

#define SYSCTL_SYSPLLMULT_REFDIV_S 24U

这不是一个代码问题,而是一个预处理器指令,用于定义一个常数。在C语言中,#define指令用于创建宏常数,即命名一个常数值。

SYSCTL_SYSPLLMULT_REFDIV_S是被定义的宏名,24U是它代表的常数值。U表示这是一个无符号整型常数。

这个宏的意思是SYSCTL_SYSPLLMULT_REFDIV_S代表24,而且它是一个无符号整数。

.............................................................................................................................................

ODIV

锁相输出分频:ODIV。分频后得到的就是锁相环初始时钟PLLRAWCLK。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

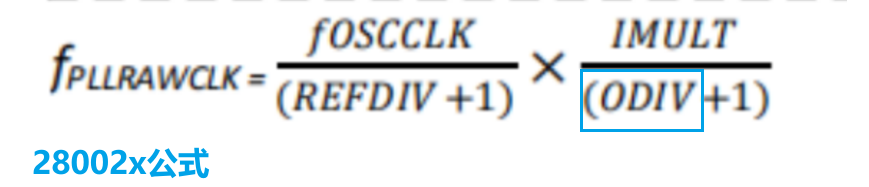

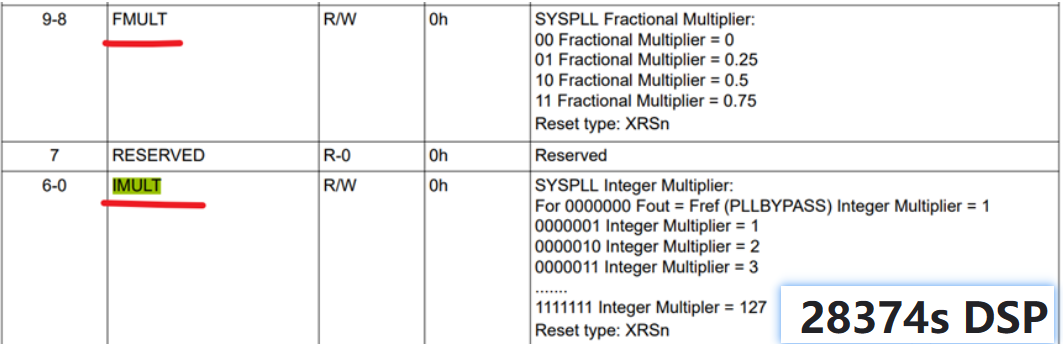

IMULT整数乘法器

FMULT:小数乘法器

!28002x手册里没有:

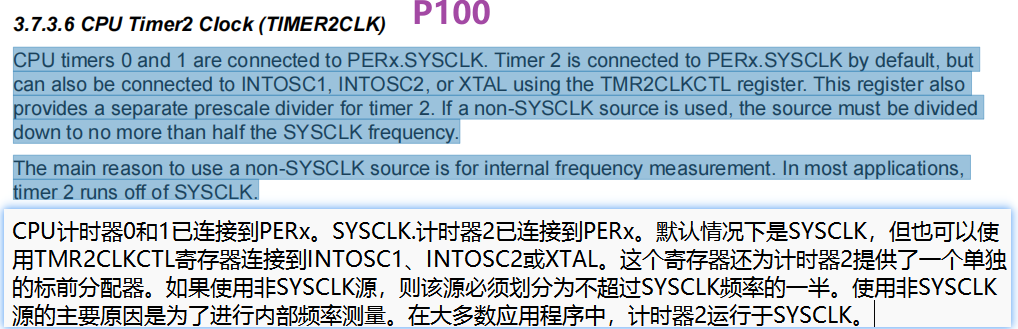

CPU工作时钟

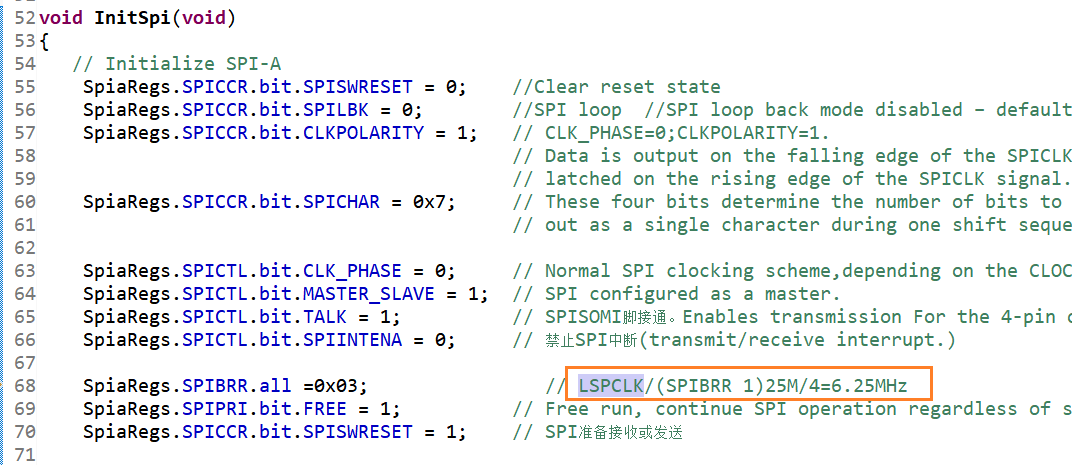

TMS320F280025的时钟_tms320f280025开发资料-优快云博客

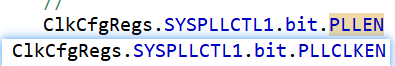

锁相环时钟使能、是否旁路

TMS320F280025的时钟_tms320f280025开发资料-优快云博客

PLLCLKEN:锁相环时钟使能。当为0时,旁路PLL。为1时,选择PLL初始输出PLLRAWCLK用于系统时钟。

PLLEN:锁相环使能。用于控制PLL模块是否工作。

相关寄存器:

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

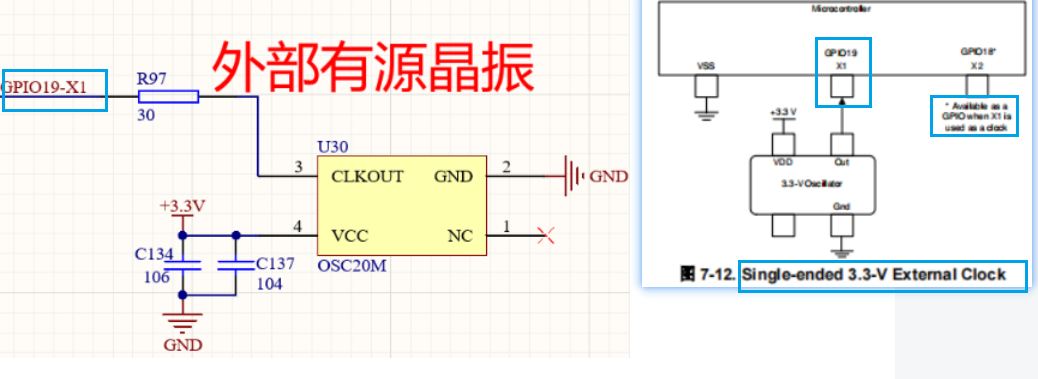

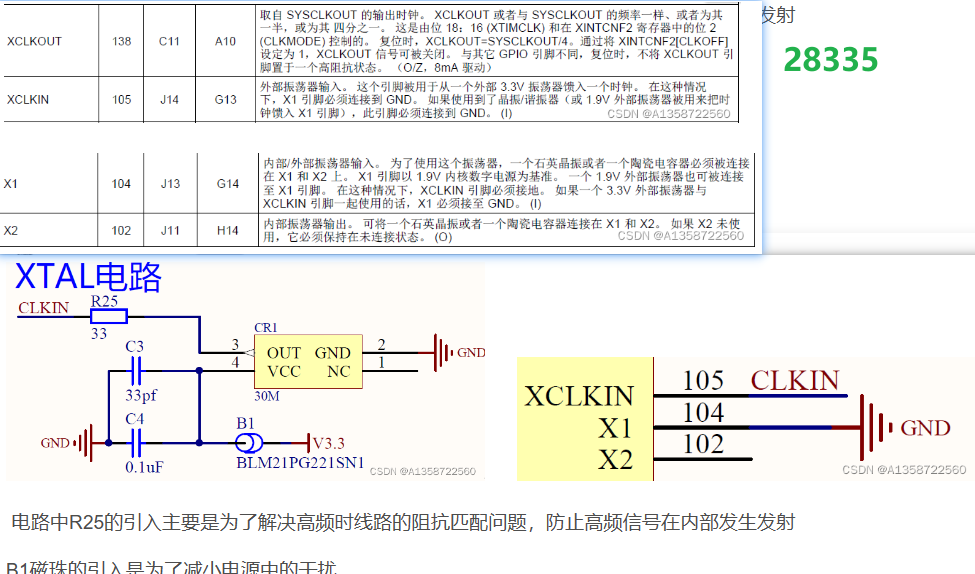

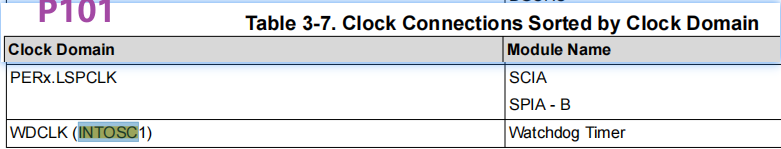

28335:“在使用有源晶振作为外部的时钟源时,DSP片内的晶体振荡电路会被旁路,外部的时钟信号有XCLKIN管脚输入DSP。看门狗定时器取OSCCLK信号作为其输入。”

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

DSP应用技术(第二章)_xintf xready-优快云博客

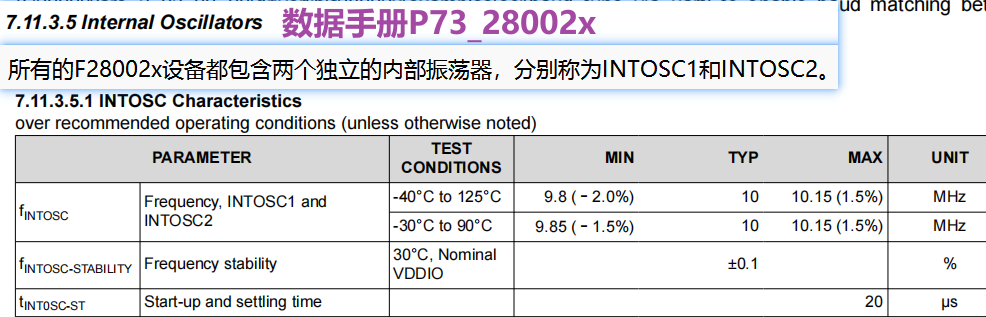

内部时钟INTOSC2、INTOSC1

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

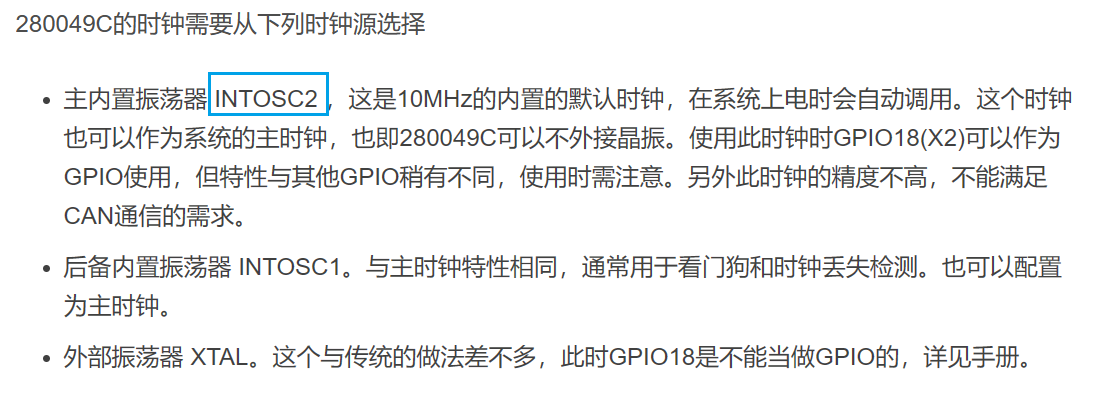

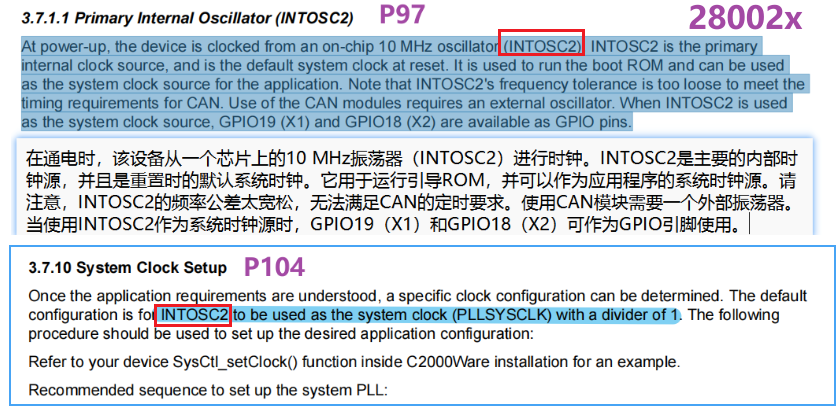

TMS320F280049C 学习笔记4 Led_ex1_blinky 初始化函数及系统时钟_device_delay_us 需关中断-优快云博客

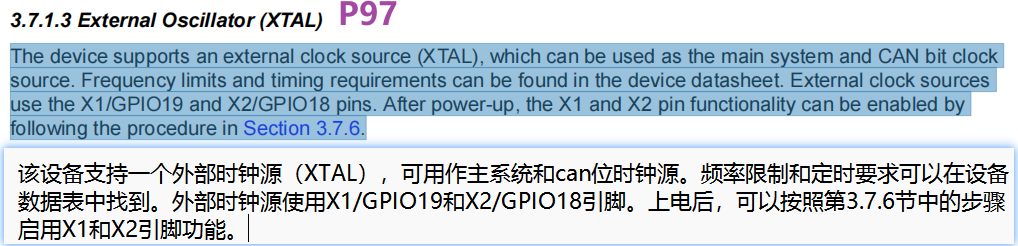

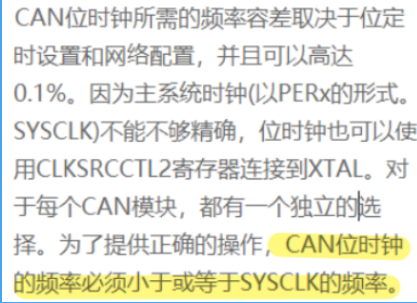

主内置振荡器 INTOSC2 ,这是10MHz的内置的默认时钟,在系统上电时会自动调用。这个时钟也可以作为系统的主时钟,也即280049C可以不外接晶振。使用此时钟时GPIO18(X2)可以作为GPIO使用,但特性与其他GPIO稍有不同,使用时需注意。另外此时钟的精度不高,不能满足CAN通信的需求。

后备内置振荡器 INTOSC1。与主时钟特性相同,通常用于看门狗和时钟丢失检测。也可以配置为主时钟。

...........................................................................................................................................................

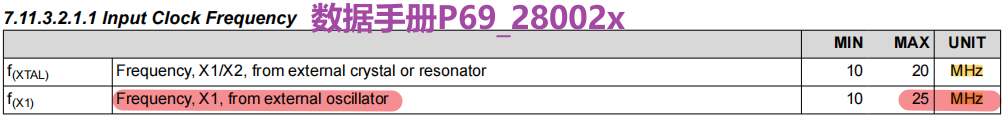

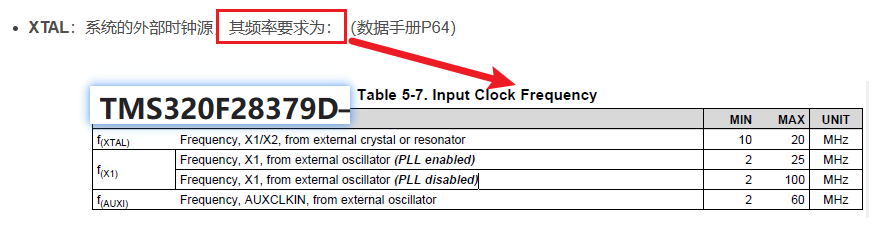

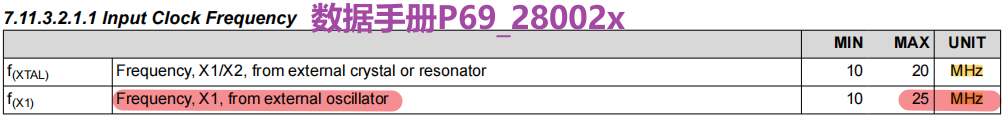

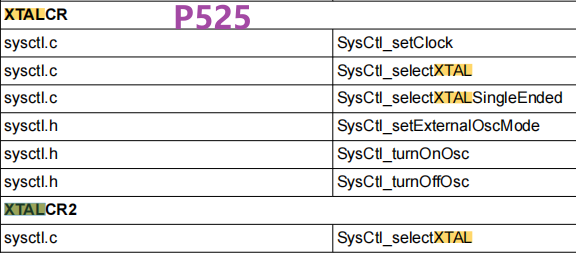

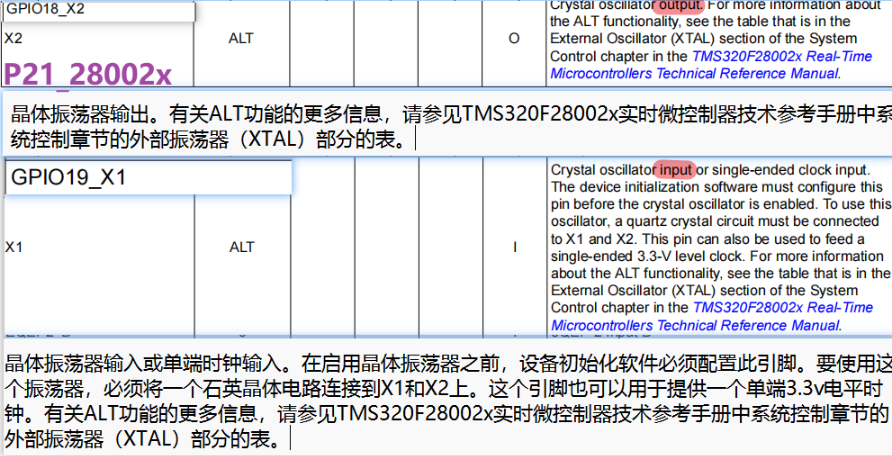

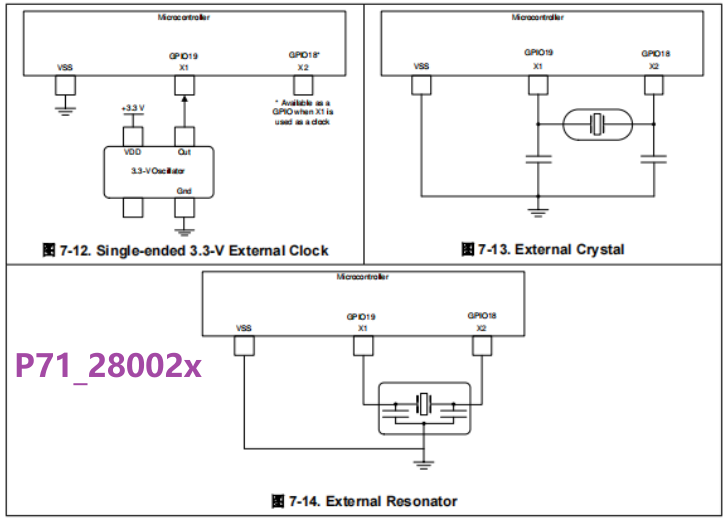

外部时钟XTAL

- 外部振荡器 XTAL。详见手册选择引脚。

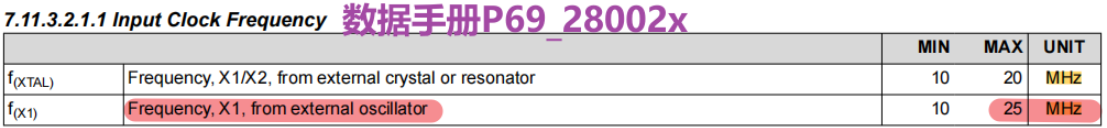

- 外部晶振频率范围:

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

TMS320F280039C: 使用外部无源晶振起振时序和复位信号关系 - C2000™︎ 微控制器论坛 - C2000 微控制器 - E2E™ 设计支持 (ti.com)

把时钟源从默认内部时钟改为外部无源晶振需要经过代码配置,这就需要时间。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

TMS320F280025C: 280025C的内部系统时钟如何配置 - C2000™︎ 微控制器论坛 - C2000 微控制器 - E2E™ 设计支持 (ti.com)

如何使用280025C的内部系统时钟代替外部晶振:

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

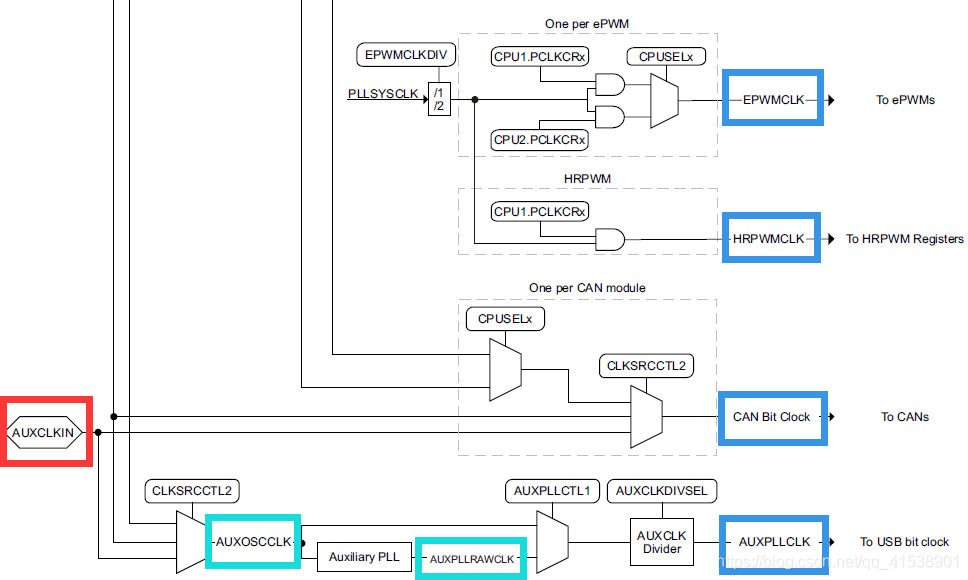

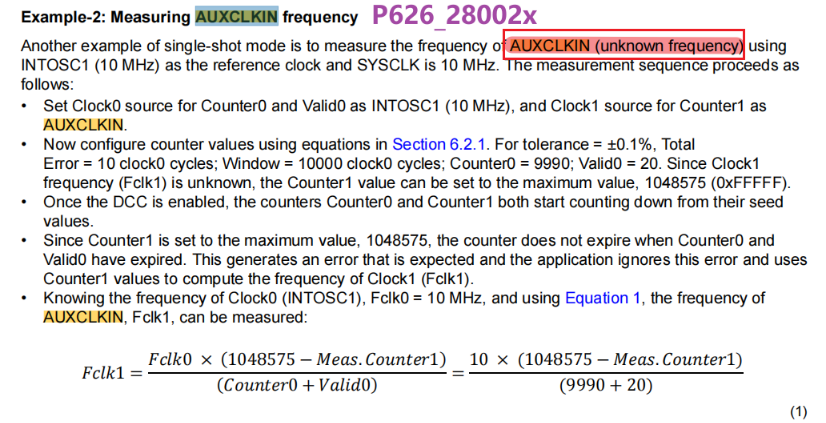

AUXCLKIN ?

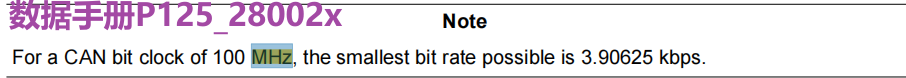

“AUXCLKIN:外部的辅助时钟源,一般用于CAN和USB的时钟源。”

OSCCLK振荡器时钟信号

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

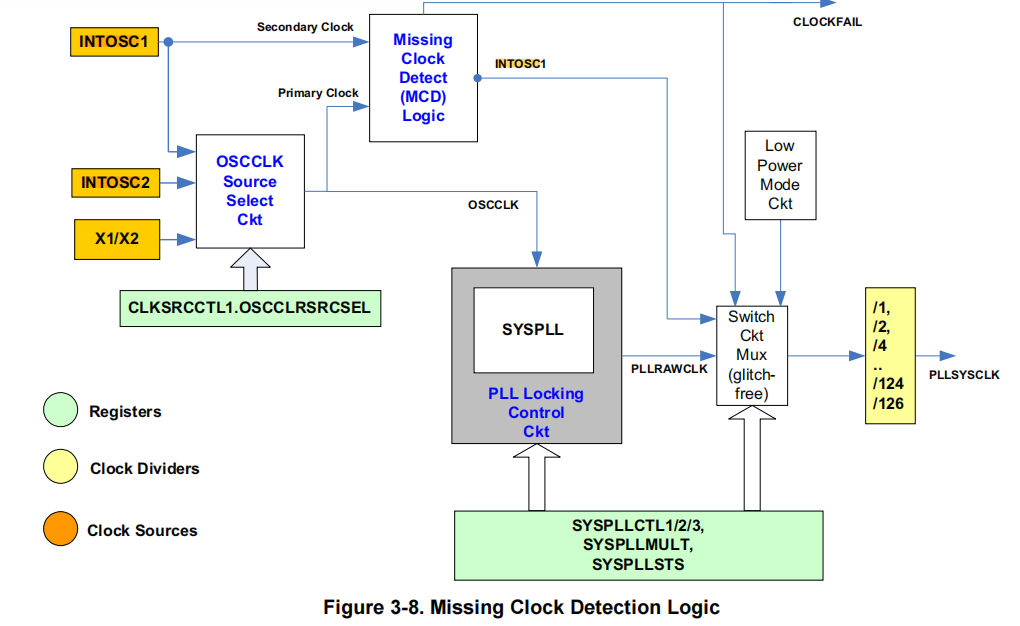

系统时钟分频

TMS320F280025的时钟_tms320f280025开发资料-优快云博客

锁相环的输出并不是直接送给系统时钟,还有一个分频的环节:

相关寄存器:![]()

“注意:当锁相环使能之后,这个分频系数最小值是2(最少4分频)。

当PLLSYSCLKDIV_LSB为1时,相当于分频系数要乘以1.5。”???

高低速时钟

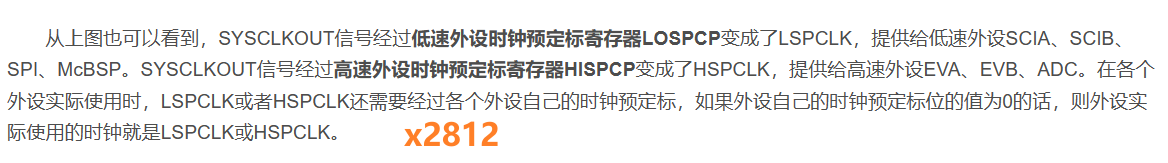

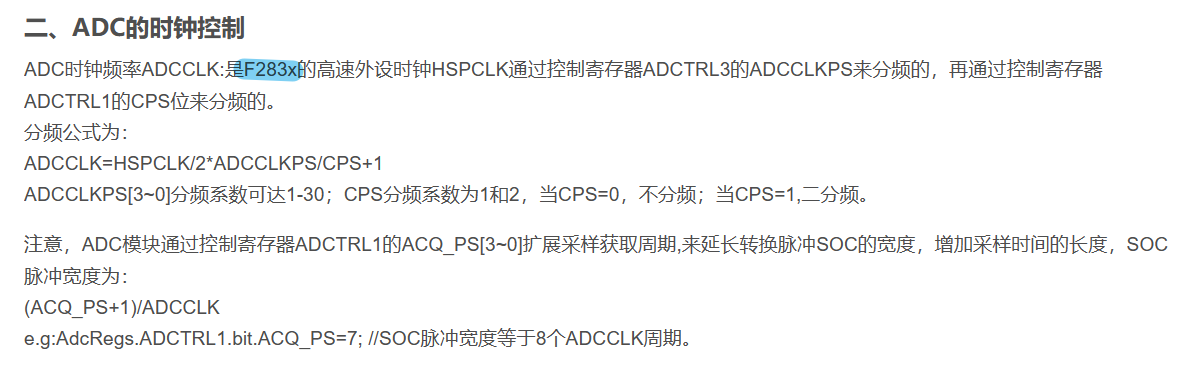

"283xx:这个部分主要是对高低速时钟进行设置,外设时钟的使能。外设时钟包括系统时钟,低速时钟,高速时钟。除了SPI、SCI、McBSP模块使用低速时钟,ADC使用高速时钟外,其他外设模块都是采用SYSCLKOUT时钟。"

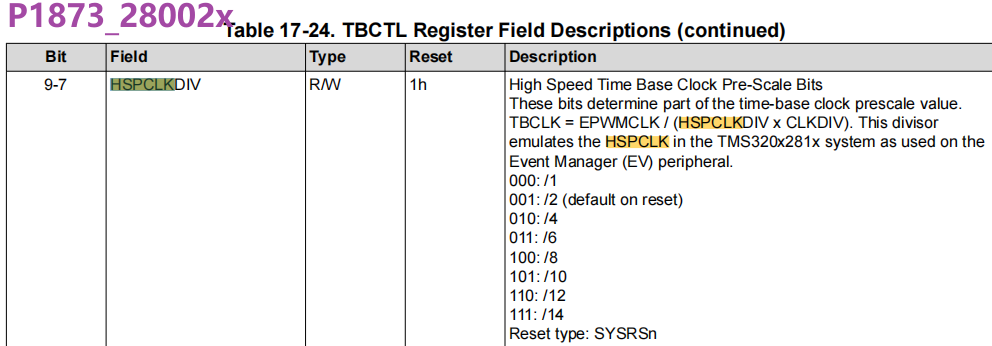

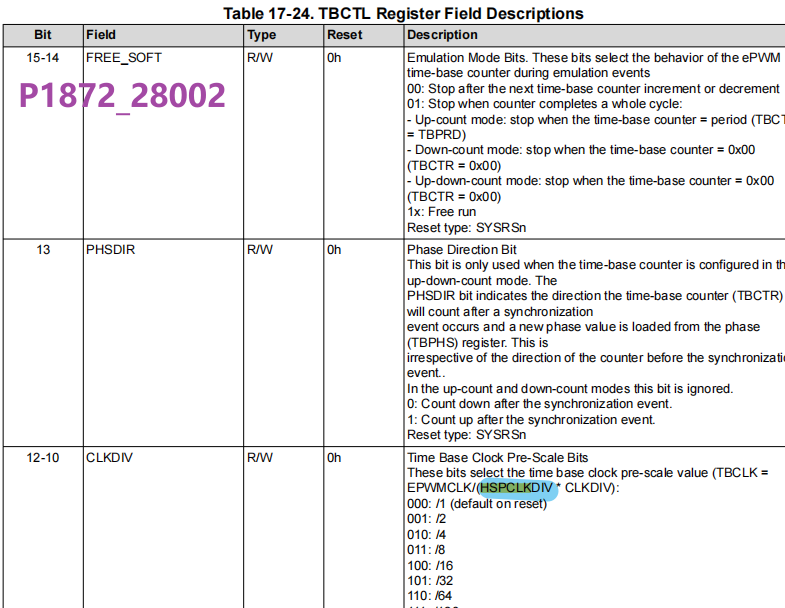

HSPCLKDIV

![]()

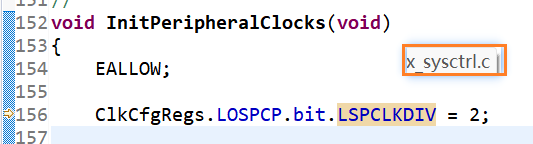

LSPCLKDIV

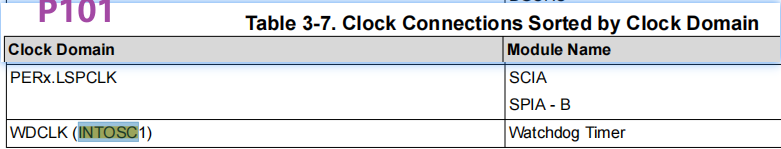

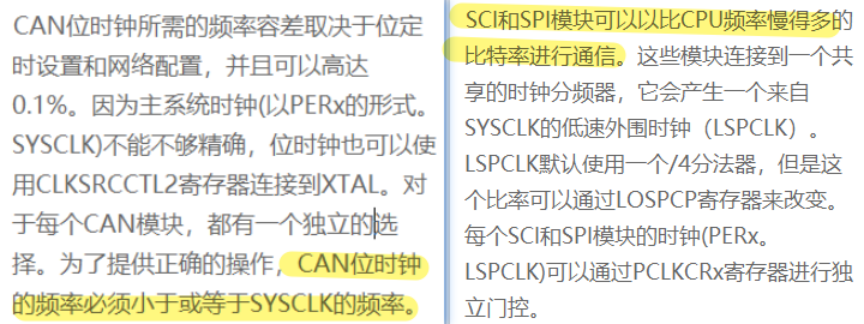

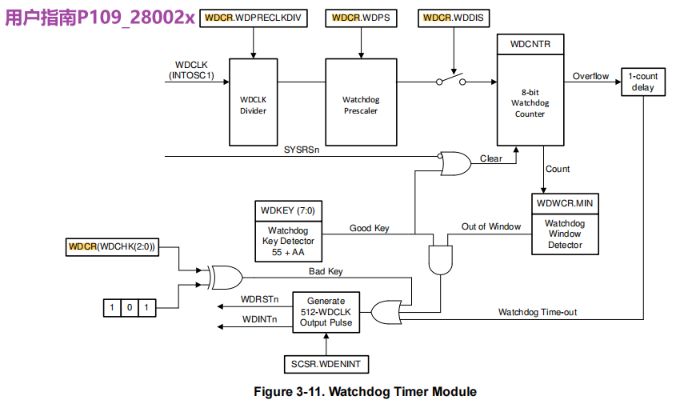

“SCl和SPI模块可以以比CPU频率慢得多的比特率进行通信。这些模块连接到一个共亨的时钟分频器,它会产生一个来自SYSCLK的低速外围时钟(LSPCLK)LSPCLK默认使用一个/4分法器,但是这个比率可以通过LOSPCP寄存器来改变每个SCl和SPI模块的时钟(PERX。LSPCLK)可以通过PCLKCRx寄存器进行独立门控。”_____cr:28002x用户指南

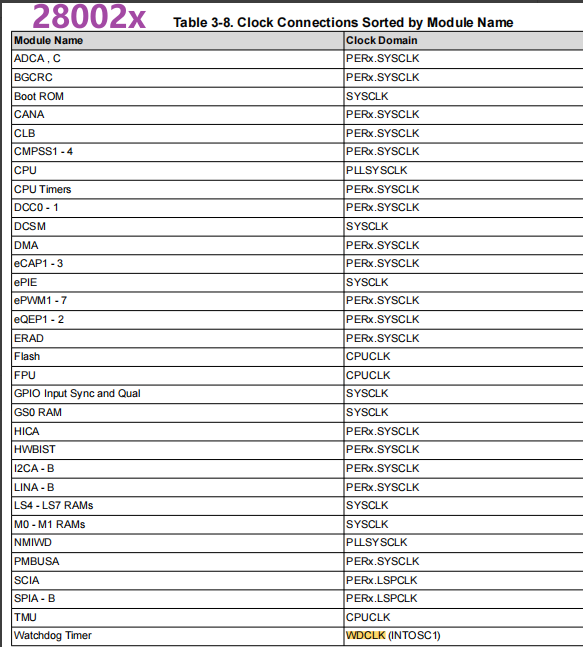

高速低速对应外设

【注意】:28002x的时钟图里没有标HSPCLK,程序里只在pwm时用HSPCLKDIV了。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

TMS320F280025的时钟_tms320f280025开发资料-优快云博客

分两大类。一类是直接使用系统时钟,另一类是使用分频后的低速时钟(SCI和SPI)。

每一路外设都有单独的时钟使能位来控制。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

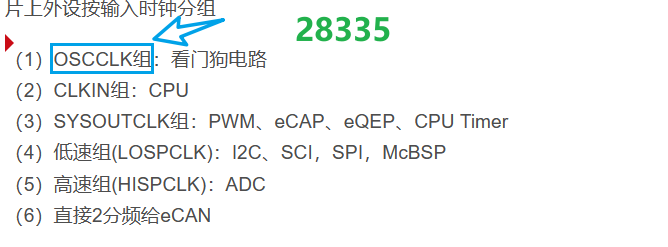

28335:

DSP28335学习记录(一)_dsp时钟必须打开-优快云博客

外设时钟分两种:高速外设时钟,低速外设时钟。

片上外设按输入时钟分组:

(1)OSCCLK组:看门狗电路

(2)CLKIN组:CPU

(3)SYSOUTCLK组:PWM、eCAP、eQEP、CPU Timer

(4)低速组(LOSPCLK):I2C、SCI,SPI,McBSP

(5)高速组(HISPCLK):ADC

(6)直接主频时钟的2分频给eCAN

I2C-A的基时钟来源是直接来源于主时钟。

GPIO的时钟不通过分频,直接为主频时钟。

EPWM1~6、HRPWM 16、ECAP16、EQEP1~2的基时钟,直接来源于主时钟。

DMA的基时钟来源是直接来源于主时钟。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

“HSPCLK的上电默认值是SYSCLKOUT / 2,即在SYSCLKOUT为150MHz的情况下,HSPCLK默认为75MHz,所以如果想让外设工作在最高频率下一定不能忘了设置这些位。此外,如果没有正确配置的话,那外设里面的定时器,如PWM定时器的周期都将与预想的产生倍数倍的错位。LSPCLK的默认值则为SYSCLKOUT / 4。

在SysCtrlRegs.PCLKCR0、SysCtrlRegs.PCLKCR1、SysCtrlRegs.PCLKCR3寄存器中,有对各个外设时钟信号的单独的使能控制。比如,我们禁止掉SysCtrlRegs.PCLKCR0里面的ECANBENCLK,则ECANB模块没有时钟信号输入,其消耗的功率就近乎为0了。(为什么?因为CMOS电路的功耗主要是动态功耗啊!)”

时钟输出(未用过)

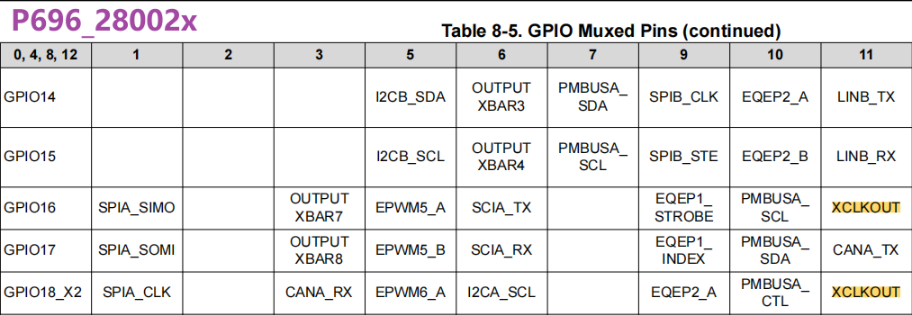

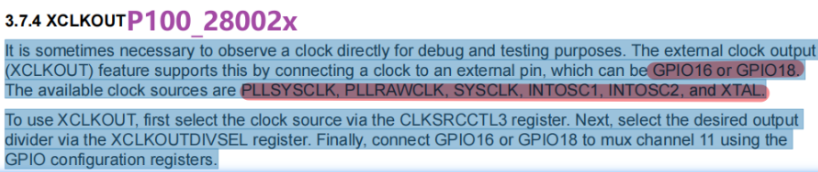

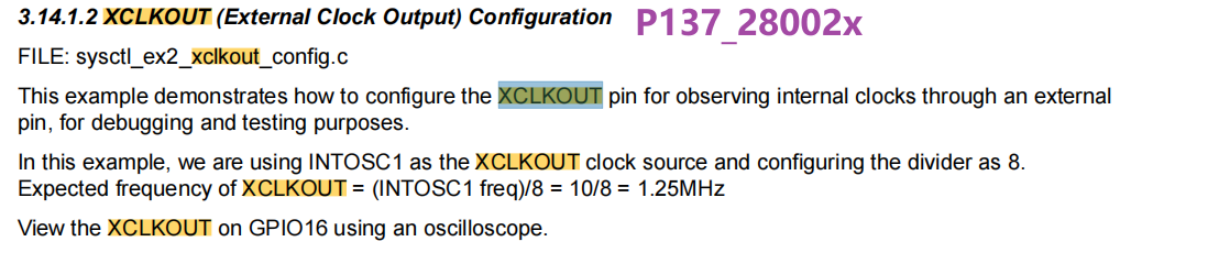

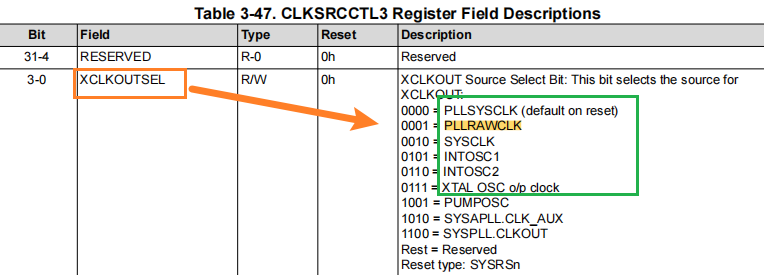

28002x手册P100:为了调试和测试的目的(把时钟输出到外部其他的芯片/想看MCU内部的时钟配置是否正确/直接观察一个时钟),外部时钟输出(XCLKOUT)功能通过将时钟连接到外部引脚来支持这个功能,它可以是GPIO16或GPIO18。可用的时钟源有:SYSCLK、INTOSC1、INTOSC2和XTAL。要使用XCLKOUT,首先通过CLKSRCCTL3寄存器选择时钟源。接下来,通过输出奇存器选择所需的输出分配器。最后,使用GPIO配置寄存器将GPIO16或GPIO18连接到mux通道11。

TMS320F280025的时钟_tms320f280025开发资料-优快云博客

首先,要将GPIO16或者GPIO18配置为XCLKOUT。

步骤二、选择时钟源 XCLKOUTSEL:

然后,选择输出哪一路时钟。![]()

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

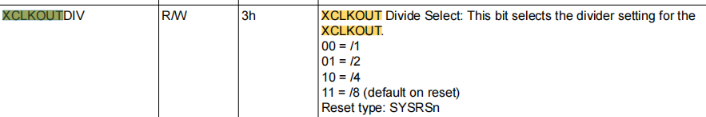

步骤三、设置分频系数 XCLKOUTDIV:

最后,在选择时钟后,还可以再分频。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

???????????????????

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

补充:用户指南关于时钟的截图

28002x用户指南手册截图

晶振电路硬件设计

(无源晶振需要借助时钟电路才能产生振荡,其自身无法振荡起来。有源晶振是一个完整的谐振振荡器。)

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

DSP28335学习之旅2-最小系统_dsp最小系统-优快云博客

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

【晶振】有源/无源晶振匹配电容电阻&PCB布局走线_有源晶振需要匹配电容吗-优快云博客

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

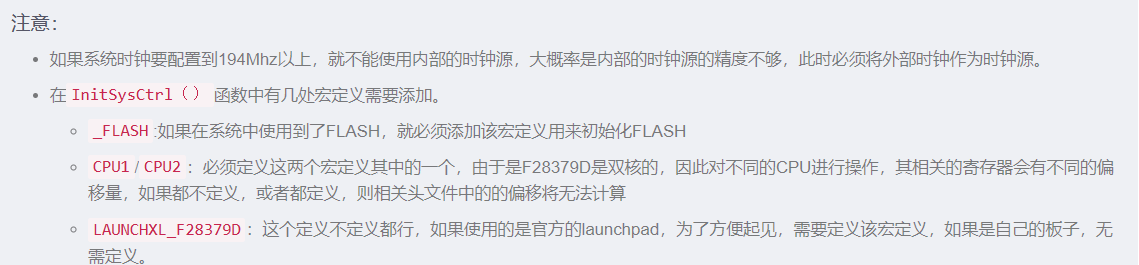

注意

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

TMS320F280025的时钟_tms320f280025开发资料-优快云博客

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

???????????????????????

//倍频时一定要分频,不倍频时才允许不分频,如果需要切换分频到1/1, 首先从默认1/4分频切换到1/2分频,让电源稳定,稳定所需要的时间依赖于系统运行速度,此处延时50us只是作为一个特例,稳定后,再切换到1/1

。 。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

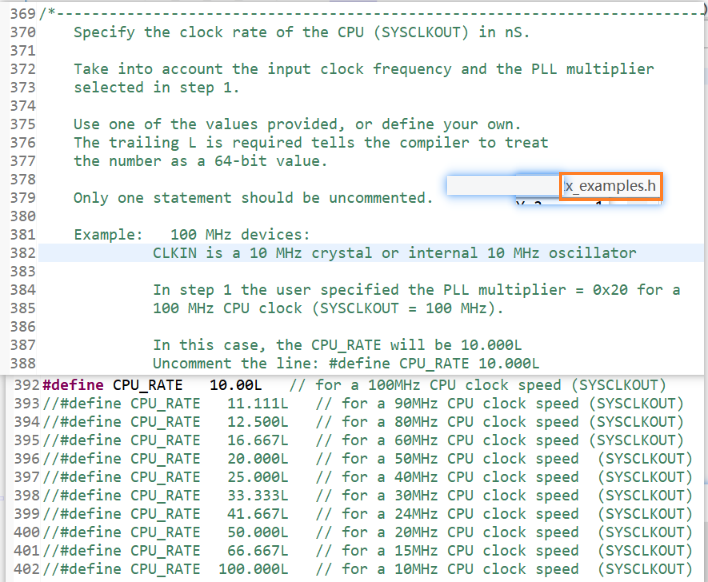

有关代码

DSP F28335时钟及控制系统_dsp在什么文件中设定晶振频率-优快云博客

//---------------------------------------------------------------------------

// InitSysCtrl:

//---------------------------------------------------------------------------

// 这段函数的功能就是将系统控制寄存器初始化到想要的状态;

//具体步骤可以分成四部分:

// - 禁止看门狗电路

// - 给PLLCR寄存器赋值以获得想要的系统时钟频率

// - 给高、低速外设时钟预定标寄存器赋值以获得想要的高、低速外设时钟频率

// - 对需要使用的外设时钟进行使能

void InitSysCtrl(void)

{

// Disable the watchdog

DisableDog();

// Initialize the PLL control: PLLCR and DIVSEL

// DSP28_PLLCR and DSP28_DIVSEL are defined in DSP2833x_Examples.h

InitPll(DSP28_PLLCR,DSP28_DIVSEL);

// Initialize the peripheral clocks

InitPeripheralClocks();

}*实例计算倍频分频28002x的时钟

| fOSCCLK=20Mhz | fPLLRAWCLK | REFDIV+1 | IMULT | ODIV+1 | |||

| 整数 | |||||||

| USE_PLL_ SRC_XTAL | XTAL_ OSC | (20Mhz*20)/[ (1+1)*(1+1)]=100Mhz | REFDIV _2 【值为1】 | IMULT _20【值为20】 | ODIV _2【值为1】 | PLLCLK _BY_1【值为0】 | SYSCTL _DCC_BASE0 【值为0】 |

| USE_PLL_ SRC_INTOSC | INT_ OSC2 | (20Mhz*30)/[ (0+1)*(2+1)]=200Mhz | REFDIV _1【值为0】 | IMULT _30【值为30】 | ODIV _3【值为2】 | PLLCLK _BY_1【值为1】 | SYSCTL _DCC_BASE0 【值为0】 |

(在CCS6中编程遇到代码背景是阴影,不知如何去掉 - 其它模拟产品 (Read-Only) - 存档论坛 - E2E™ 设计支持 (ti.com))

【在使用C语言的CCS(Code Composer Studio)集成开发环境中,代码背景出现灰色阴影通常表示这段代码处于注释或者被禁用的状态。这意味着这部分代码不会被编译器执行,可以被用于注释掉一些暂时不需要的代码或者进行调试时的代码排除。通过将代码注释或禁用,可以方便地进行代码的调试和排查问题。】

疑问点?

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

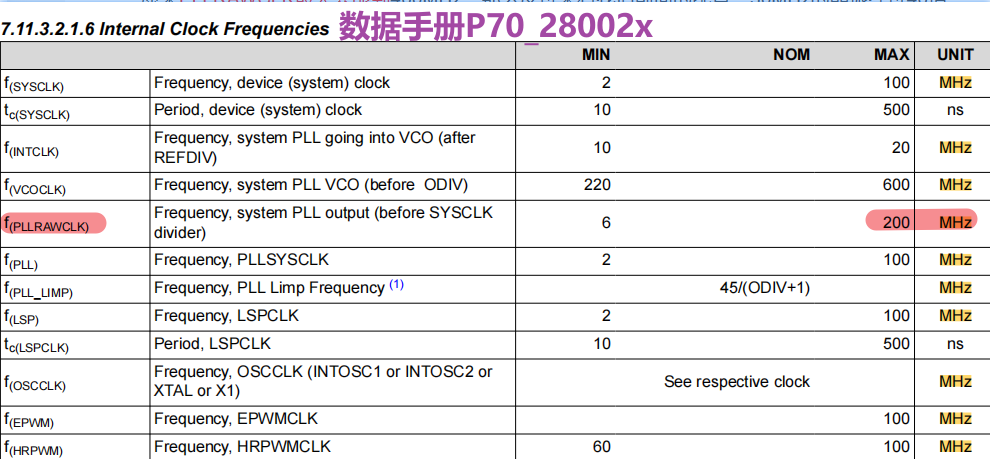

28002x的PLLRAWCLK最大只能到200MHz:但是倍频20就会超呀?

(20Mhz*20)/[ (1+1)*(1+1)]=100Mhz

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

看divsel值不是2呀?

TMS320F280025的时钟_tms320f280025开发资料-优快云博客

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

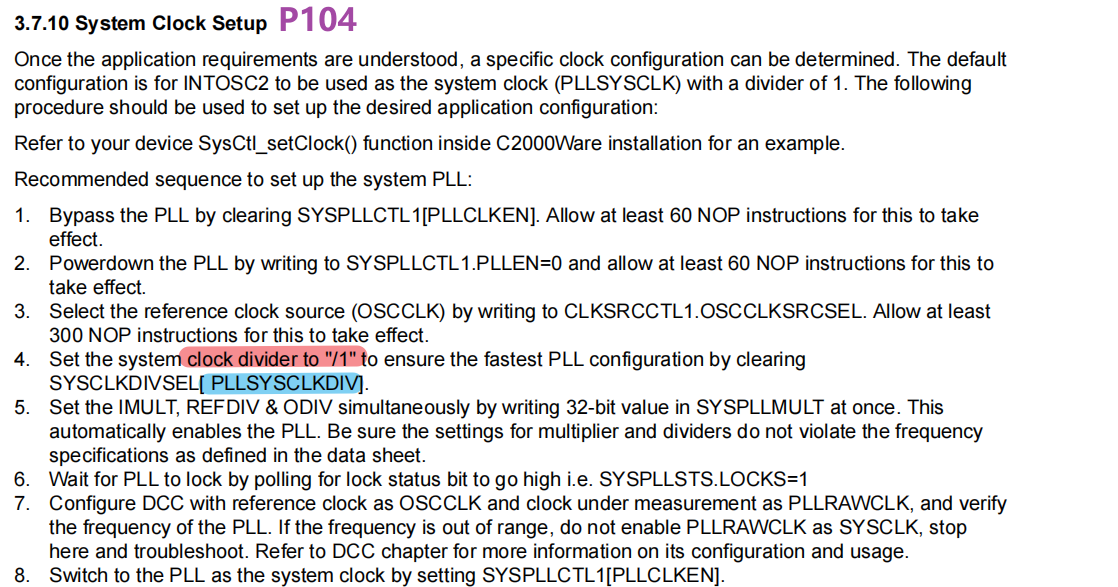

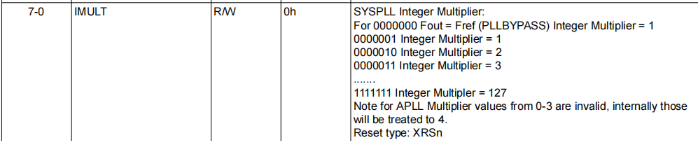

**DSP28377s系统时钟配置注意事项

DSP28377s系统时钟配置注意事项 - 大风当歌 - 博客园 (cnblogs.com)

问题:配置基于28377s芯片的主控系统时钟时,原来的主控板使用的是20MHz外部晶振,为取200MHz系统时钟,倍频设为20,分频设为2,这样sysclock = 20MHz * 20 / 2,正好200MHz。具体调用TI公司的库函数,实现代码是这样的:

InitSysPll(XTAL_OSC,IMULT_20,FMULT_0,PLLCLK_BY_2);

但新的控制板上面使用了30MHz外部晶振,为配置200MHz系统时钟,将倍频设为40,分频设为6,代码如下:

InitSysPll(XTAL_OSC,IMULT_40,FMULT_0,PLLCLK_BY_6);

计算下来,系统时钟也应该是200MHz,不过,按此配置后,程序运行就卡死在定时器1、2溢出while循环里了。

系统时钟产生模式:

内外部时钟,可通过CLKSRCCTL1来选择哪个作为时钟源,之后所选的时钟源可由SYSPLLCTL1选择是否经PLL倍频后使用,一般为了DSP能够高速运算,都会选择使用PLL的。那么经过PLL之后,会得到PLLRAWCLK,然后再通过SYSCLKDIVSEL进行分频,最终就会得到我们想要的系统时钟了。结合上面的代码,倍频过程就是通过IMULT_xx(整数),FMULT_x(小数)两个参数实现的,分频就是由PLLCLK_BY_x这个参数实现的。

PLLRAWCLK有一个可接受范围,看TI公司的28377s的规格文档,在里面表5-12有清晰的说明,如下:

原来PLLRAWCLK最大只能到400MHz,那么反过来看前面的配置,30MHz的晶振经过40倍频,已经达到了1200MHz,远远超出了允许范围。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

28002x的PLLRAWCLK最大只能到200MHz:

。。。。。。。。。。

【解决方案】:

法一:简单的降低倍频,比如30MHz做10倍频,然后2分频,得到150MHz的系统时钟。不过28377s的最大系统时钟可以到200MHz,缺点:牺牲了点芯片性能。

分析:400除以30得13.3333。。。。,它可以无限循环下去,那么比它小的可以配置的最大数是多少?13.25(小数只能有0,0.25,0.5,0.75四个选择),这样可以得到397.5MHz的倍频输出,再作2分频,系统时钟198.75MHz,应该是最大限度的利用了。

按照上面的配置,代码如下:

InitSysPll(XTAL_OSC,IMULT_13,FMULT_0pt25,PLLCLK_BY_2);

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

时钟开启顺序?(待)

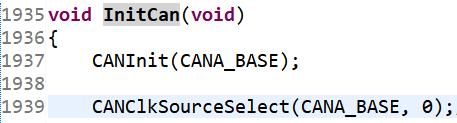

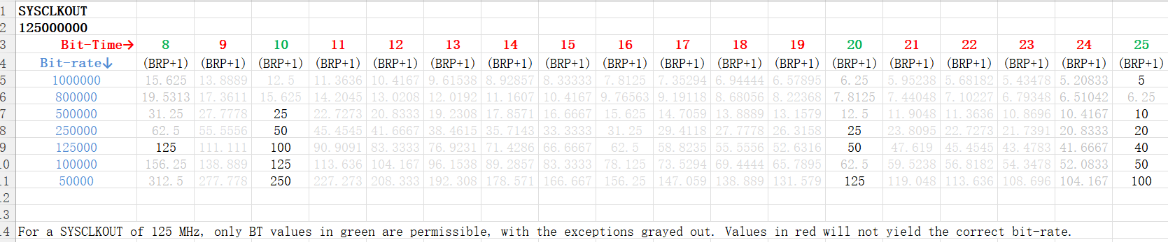

CAN频率

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

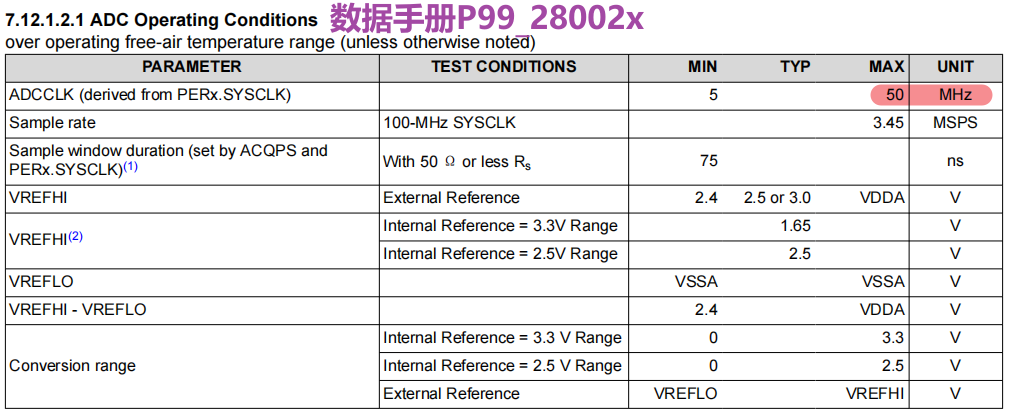

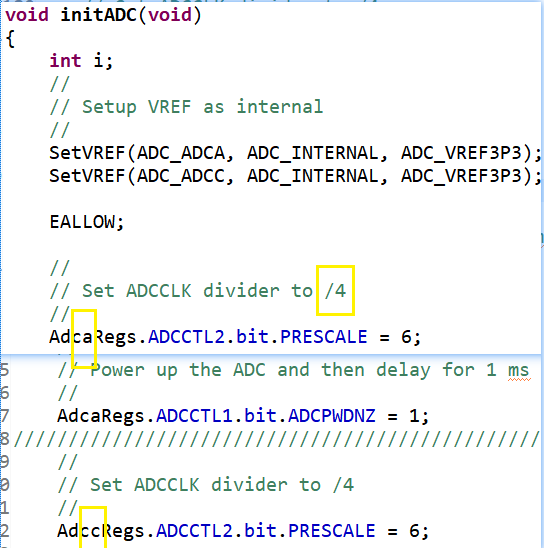

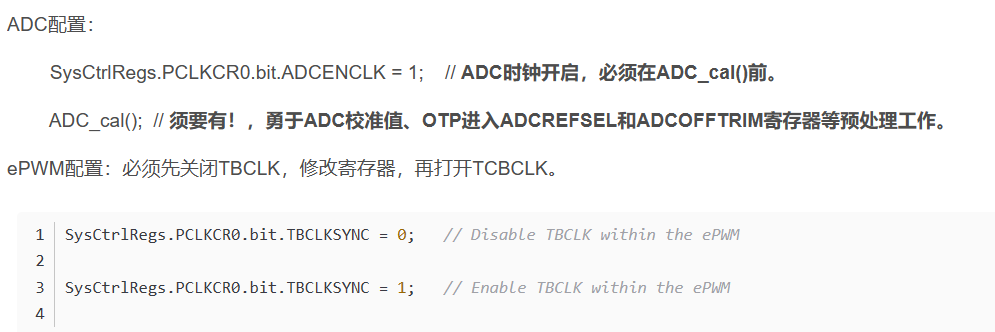

ADC时钟配置(待)

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

DSP28335学习记录(一)_dsp时钟必须打开-优快云博客

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

PWM分频(待)

...........................................................................................................................................................

TMS320F280041: EPWM时钟分频设计 - C2000™︎ 微控制器论坛 - C2000 微控制器 - E2E™ 设计支持 (ti.com)

问:EPWM为什么要设计CLKDIV和HSPCLKDIV(两个时钟分频系数相乘)吗?相对一个时钟分频有什么优势?

答:1. 配置更灵活;2. 实现更高的分频数。

...........................................................................................................................................................

看门狗

定时器0 1

Delay函数

![]()

待看

1,TMS320F28069 学习--------InitSysCtrl();_tms320f280049c 使用外部晶振-优快云博客

645

645

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?