具体参考Xilinx文档,pg109-xfft Version9.1。

一、Fast Fourier Transform有什么用?

Fast Fourier Transform是Vivado中的IP核,即快速傅里叶变换(FFT)。IP核内部使用的Cooley-Tukey FFT算法,是一种计算效率高的离散傅立叶变换 (DFT)方法。

可实现正向和反向复数FFT(即IFFT),运行时间可配置。

• 变换大小N = 2 m 2^m 2m,m = 3-16。

• 数据采样精度bx = 8 - 34。

• 相位因数精度bw = 8 - 34。

二、Fast Fourier Transform怎么用?

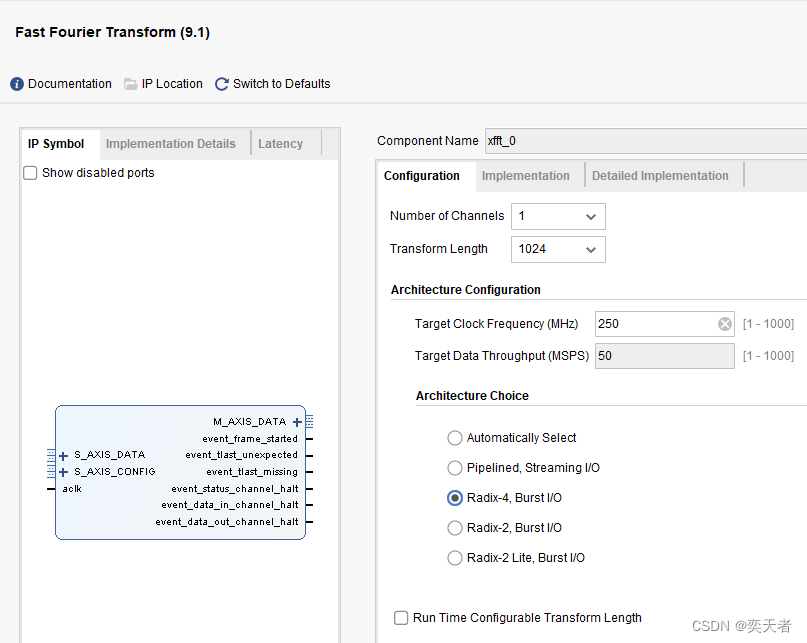

配置参数设置

Number of Channels:通道数。可选通道数范围为1-12。多通道操作可用于三个突发I/O体系结构(即Radix-2 Burst I/O、Radix-2 Lite Burst I/O、Radix-4 Burst I/O结构)。

Transform Length:变换长度。选择所需的点大小。从8到65536范围内的所有2的幂是可用的。

Architecture Configuration:结构配置。

Target Clock Frequency(MHz):目标时钟频率(1-1000)。仅用于自动选择结构和计算延迟,但不保证IP核以指定的目标时钟频率运行。

Target Data Throughput(MSPS):目标数据吞吐量(1-1000)。仅用于自动选择结构和计算延迟,但不保证IP核以指定的目标数据吞吐量运行。

Architecture Choice:结构选项。有以下五种结构可选:

- Automatically Select:自动选择结构。以选择满足指定目标数据吞吐量的最小实现,前提是在FPGA上实现FFT内核时达到指定的目标时钟频率。

- Pipelined Streaming I/O:流水线I/O结构。支持点大小为8到65536。

- Radix-2 Burst I/O:Radix-2突发I/O结构。支持点大小为8到65536。

- Radix-2 Lite Burst I/O:Radix-2 Lite突发I/O结构。支持点大小为8到65536。

- Radix-4 Burst I/O:Radix-4突发I/O结构。支持点大小64到65536。

Run Time Configurable Transform Length:运行时间可配置变换长度,选中则表示选中s_axis_config_tdata中的NFFT字段,此时的Transform Length数值只是最大FFT点数,不代表实际运行时的FFT点数;反之,当转换长度不是运行时间可配置的时,FFT内核使用较少的逻辑资源并且具有更快的最大时钟速度。

实现参数设置

Data Format:数据格式。有两种数据格式可选:

- Fixed Point: 选择输入和输出数据样本是定点格式。

- Floating Point: 选择输入和输出数据样本是IEEE-754单精度 (32位) 的浮点格式。当FFT IP核处于多通道配置时,浮点格式不可用。

Scaling Options:缩放选项。对于所有体系结构,有三个选项可用:

- Block Floating point:块浮点。由核心决定需要多大的缩放才能充分利用可用动态范围,并将缩放因子报告为块指数。

- Scaled:缩放。用户定义的缩放计划决定如何在FFT级之间缩放数据。

- Unscaled:未缩放。所有整数位增长都被传递到输出。这样会使用更多的FPGA资源。

Rounding Modes:舍入模式。在蝶形的输出处,需要削减数据路径中的LSBs。

- Convergent rounding:收敛舍入。收敛舍入是一种无偏舍入方案,可以用避免DC偏差(直流偏差)。当一个数的小数部分正好等于二分之一时,如果该数是奇数,则收敛舍入向上舍入;如果该数是偶数,则向下舍入。由于额外的延迟,选择此选项会增加切片的使用。

- truncation:截断。在蝶形阶段之后截断,会引入DC偏差(直流偏差)。

Precision Options:精度选项。

Input Data Width:输入数据位宽。可独立配置为宽度从8到34位。当数据格式为浮点(Floating Point)格式时,输入数据宽度固定为32位。

Phase Factor Width:相位因子位宽。可独立配置为宽度从8到34位。当数据格式为浮点(Floating Point)格式时,相位因子宽度可以设置为24或25位,具体取决于所需的噪声性能和可用的资源。

Control Signals:控制信号。如果两者都被选中,同步清除优先于时钟启用。如果有一个未选中,则可以节省一些逻辑资源,并且获得更高的时钟频率。

ACLKEN:是否启用时钟使能。

ARESETn(active low):是否启用同步清除(低电平有效)。同步清除端,必须持续至少2个时钟周期才能生效。

Output Ordering Options:输出排序选项。

- Bit/Digit Reversed Order:位/数字逆序。基于Radix-2的体系结构 (流水线I/O,Radix-2突发I/O和Radix-2 Lite突发I/O) 提供位逆序排序,基于Radix-4的体系结构 (Radix-4突发I/O) 提供数字逆序排序。

- Natural Order:自然顺序。对于流水线I/O架构,选择自然顺序输出排序会导致内核使用的内存增加。对于突发(Burst)I/O体系结构,选择自然顺序输出会增加整体转换时间,因为需要单独的卸载阶段。

Cyclic Prefix Insertion:循环前缀插入。如果输出排序是自然顺序,则可以选择循环前缀插入。循环前缀插入适用于所有架构,通常用于OFDM无线通信系统。

Optional Output Fields:可选输出字段。

XK_INDEX:输出序列序号。数据输出通道中的可选字段。由m_axis_data_tuser端口输出。

OVFLO:溢出标志位。数据输出通道和状态通道中的可选字段。由m_axis_data_tuser端口或是m_axis_status_tdata端口输出。

Throttle Scheme:节流方案。选择性能和数据定时之间的权衡要求。

Real Time: 实时模式。通常给出更小和更快的设计,但对何时必须提供和使用数据有严格的约束。

Non Real Time: 非实时模式。没有实时模式那样的约束,但设计可能更大、更慢。

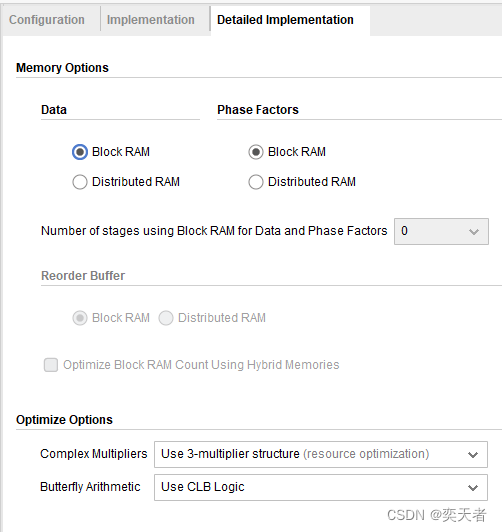

详细实现参数设置

Memory Options:存储器选项。

Data and Phase Factors:数据和相位因子。对于突发(Burst)I/O架构,块RAM和分布式RAM都可用于数据和相位因子存储。数据和相位因子存储可以在分布式RAM中,用于所有点的大小(包括1024点);在流水线I/O结构中,数据可以部分存储在块RAM中

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

911

911

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?