1、MIO/EMIO简介

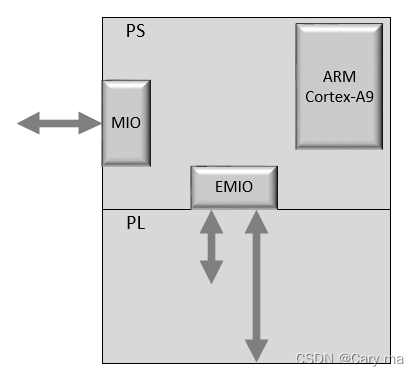

ZYNQ 分为 PS 和 PL 两部分,那么器件的引脚(Pin)资源同样也分成了两部分。ZYNQ PS 中的外设可以通过 MIO(Multiuse I/O,多用输入/输出)模块连接到 PS 端的引脚上,也可以通过 EMIO 连接到 PL 端的引脚。Zynq-7000 系列芯片一般有 54 个 MIO、64个EMIO。

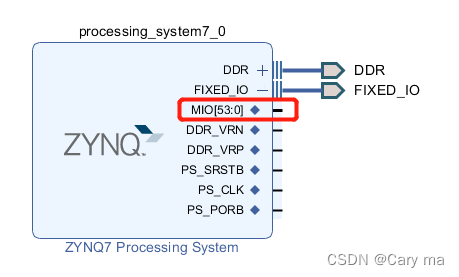

2、MIO管脚约束

如上图,MIO包含在PS的FIXED_IO中,在生成输出文件的时候,Vivado工具会自动创建PS端的管脚约束,所生成的约束文件的具体位置在“E:/../hello_world.srcs/sources_1/bd/system/ip/system_processing_system7_0_0/system_processing_system7_0_0.xdc”。因此MIO不需要用户手动进行管脚约束。

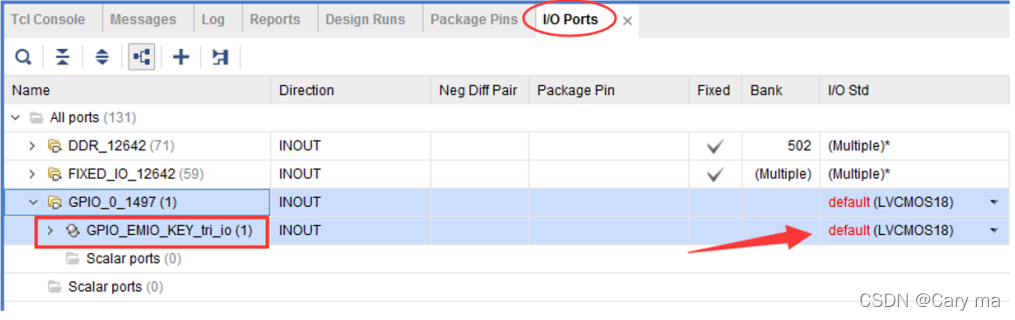

3、EMIO管脚约束

当PS使用EMIO与PL进行连接,并调用PL的IO资源进行输入输出时,需要用户进行手动管脚约束。

ZYNQ FPGA的PS部分包含54个MIO和64个EMIO引脚资源。MIO用于连接PS端的外设,其管脚约束在Vivado生成的.xdc文件中自动完成。而EMIO则需要用户手动设置管脚约束,用于PS与PL之间的通信和利用PL的IO资源。理解并正确配置这些接口对于Zynq-7000系列芯片的系统级设计至关重要。

ZYNQ FPGA的PS部分包含54个MIO和64个EMIO引脚资源。MIO用于连接PS端的外设,其管脚约束在Vivado生成的.xdc文件中自动完成。而EMIO则需要用户手动设置管脚约束,用于PS与PL之间的通信和利用PL的IO资源。理解并正确配置这些接口对于Zynq-7000系列芯片的系统级设计至关重要。

2737

2737

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?