本文首发于个人博客

1.AXI总线结构

AXI总线由5个通道构成:

| 通道名称 | 通道功能 | 数据流向 |

|---|---|---|

| read address | 读地址通道 | 主机->从机 |

| read data | 读数据通道(包括数据通道和读响应通道) | 从机->主机 |

| write address | 写地址通道 | 主机->从机 |

| write data | 写数据通道(包括数据通道和每8bit一个byte的写数据有效信号) | 主机->从机 |

| write response | 写响应通道 | 从机->主机 |

1.1.AXI通道

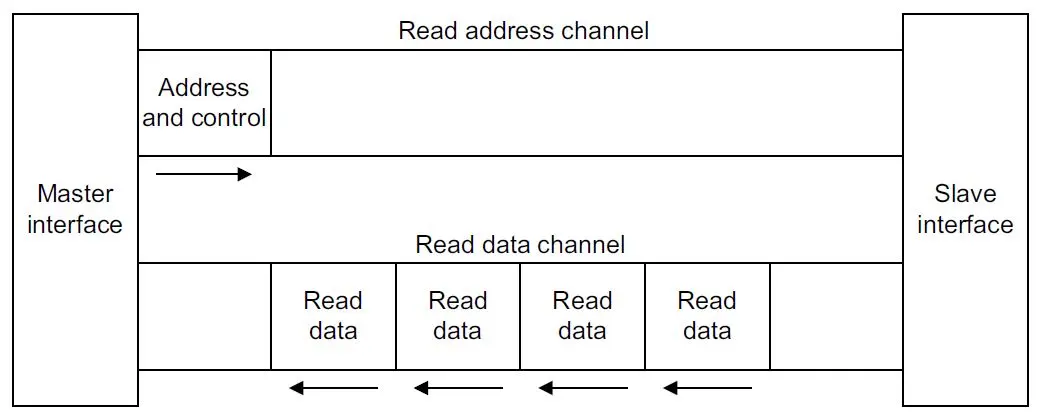

读操作的通道如下图所示

axi_read_channel.JPG

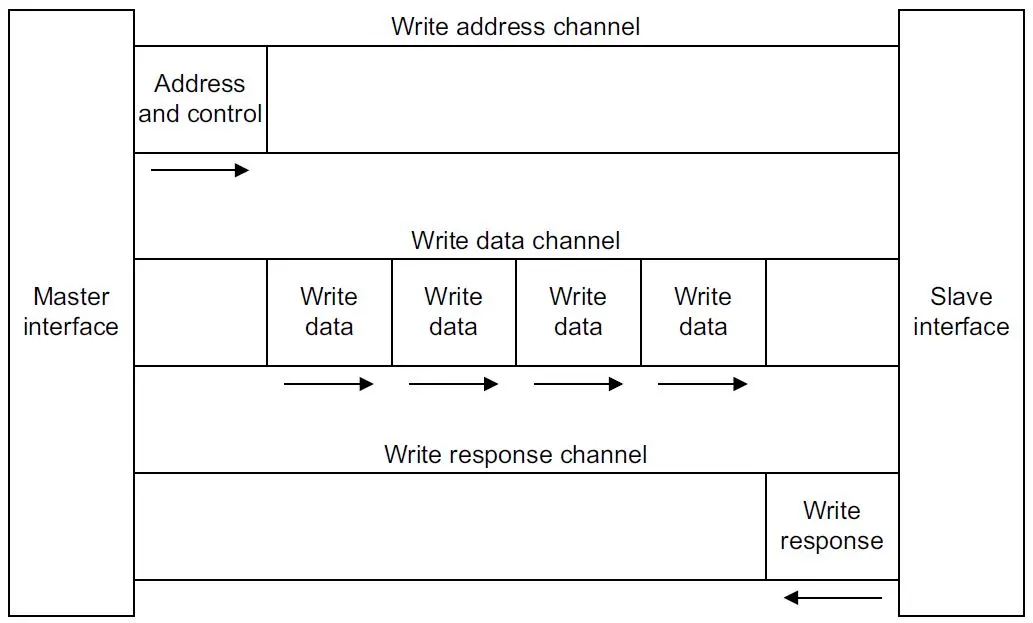

写操作的通道如下图所示

axi_write_channel.JPG

1.2.AXI系统

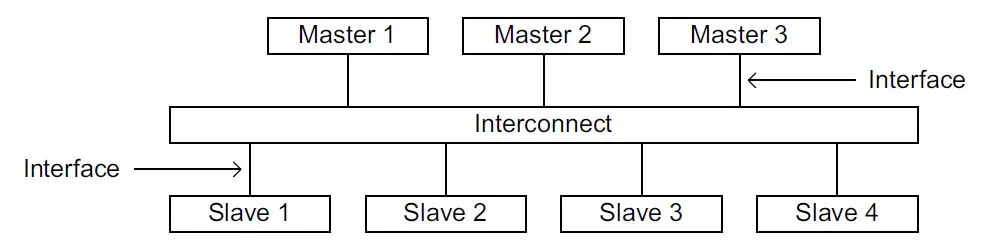

常见的标准AXI系统如下图所示,通常包括:

- AXI master:AXI通信主机

- AXI slave:AXI通信从机

- AXI interconnect:AXI通信通路

axi_typical_system.JPG

AXI接口协议可用于:

- AXI master - AXI interconnect的连接

- AXI slave - AXI interconnect的连接

- AXI master - AXI slave的连接

1.3.AXI接口

1.3.1.全局信号

| 信号名 | 来源 | 描述 |

|---|---|---|

| ACLK | system clock | 全局时钟信号 |

| ARESTn | system reset | 全局复位信号,低有效 |

1.3.2.写地址通道

| 信号名 | 来源 | 描述 |

|---|---|---|

| AWID | master | 写地址ID(用于区分该地址属于哪个写地址组) |

| AWADDR | master | 写地址 |

| AWLEN | master | 突发长度 |

| AWSIZE | master | 突发尺寸(每次突发传输的最长byte数) |

| AWBURST | master | 突发方式(FIXED,INCR,WRAP) |

| AWCACHE | master | 存储类型(标记系统需要的传输类型) |

| AWPROT | master |

本文详细介绍了AXI(Advanced eXtensible Interface)总线的结构,包括AXI通道、AXI系统和AXI接口。内容涵盖了AXI接口的五个通道、时序规范,如复位、基本传输握手信号和通道顺序,以及数据结构的各个组成部分,如地址通道数据结构、数据通道数据结构和应答通道数据结构。AXI总线的传输特性、存储器特性和存储器类型也在文中有所阐述。

本文详细介绍了AXI(Advanced eXtensible Interface)总线的结构,包括AXI通道、AXI系统和AXI接口。内容涵盖了AXI接口的五个通道、时序规范,如复位、基本传输握手信号和通道顺序,以及数据结构的各个组成部分,如地址通道数据结构、数据通道数据结构和应答通道数据结构。AXI总线的传输特性、存储器特性和存储器类型也在文中有所阐述。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6426

6426

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?