第28章 GPIO

1. 概述(Overview)

GPIO通用输入/输出外设提供专用通用引脚,可配置为输入或输出。

当配置为输出时,可以写入内部寄存器以控制输出引脚上驱动的状态。当配置为输入时,可以通过读取内部寄存器的状态来检测输入的状态。此外,GPIO外设可以产生CORE中断。

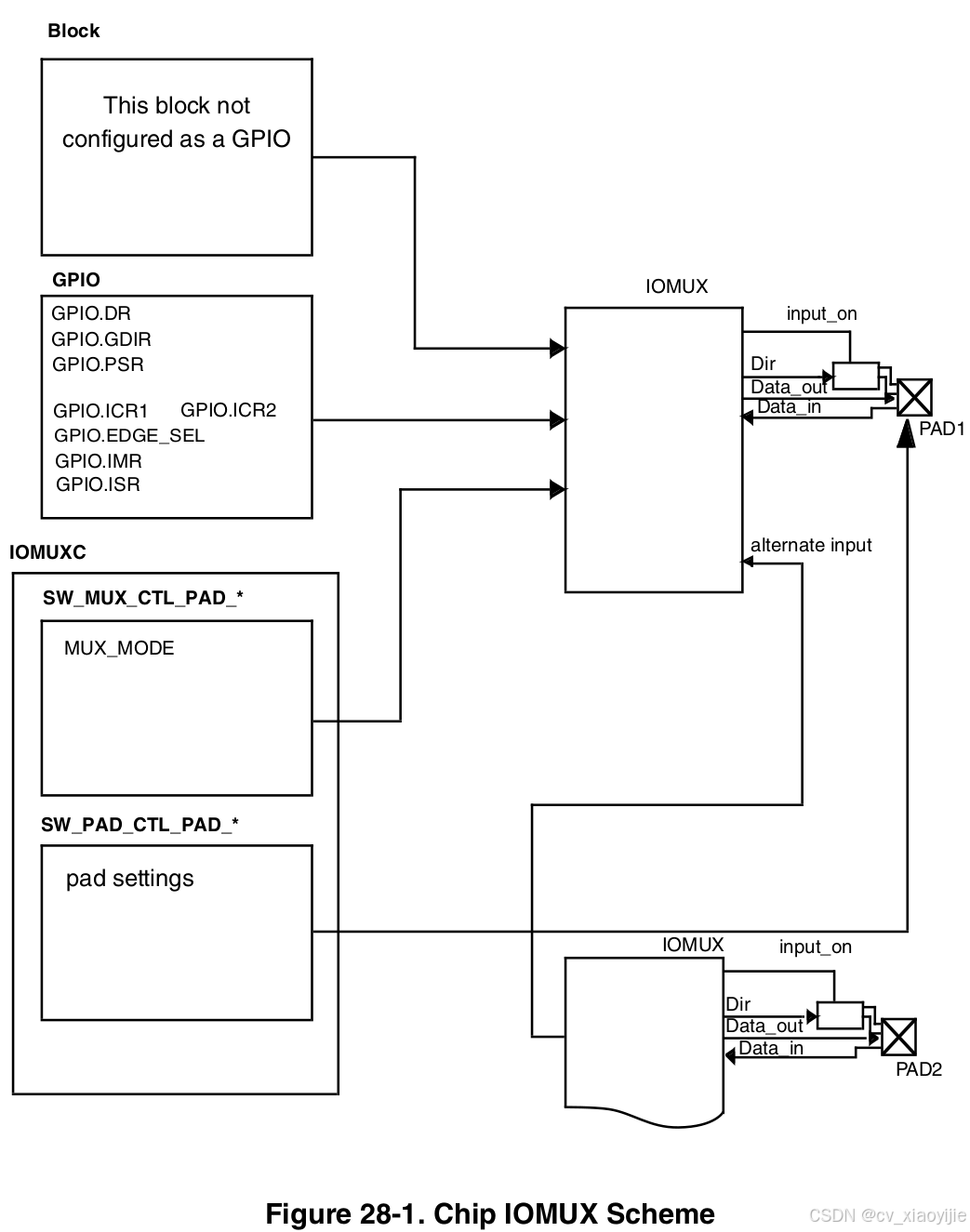

GPIO是控制芯片IOMUX的模块之一。

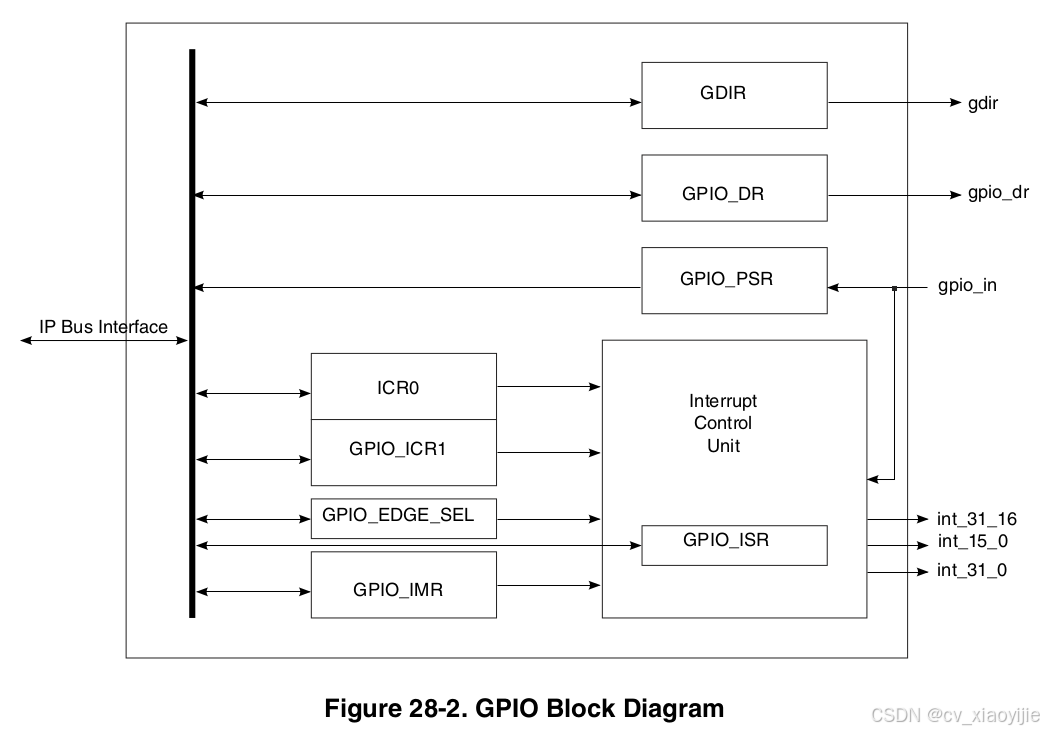

GPIO功能通过八个寄存器、一个边缘检测电路和中断生成逻辑提供。这八个寄存器是:

- 数据寄存器(GPIO_DR)

- GPIO方向寄存器(GPIO_GDIR)

- PAD采样寄存器(GPIO_PSR)

- 中断控制寄存器(GPIO_ICR0、GPIO_ICR1)

- 边缘选择寄存器(GPIO_Edge_SEL)

- 中断掩码寄存器(GPIO_IMR)

- 中断状态寄存器(GPIO_IRS)

这些寄存器细节描述在 5. GPIO内存映射/寄存器定义(GPIO内存映射/寄存器定义)

每个GPIO输入都有一个专用的边缘检测电路,可以通过软件配置,以检测输入信号上的上升沿、下降沿、逻辑低电平或逻辑高电平。通过在中断屏蔽寄存器(GPIO_IMM)中设置相应的位,可以选择性地屏蔽边缘检测电路的输出。这些合格的输出被加在一起,生成两条1位中断线: - GPIOx信号0-15的组合中断指示

- GPIOx信号的组合中断指示16-31

此外,GPIO1为其8个低位中断源中的每一个提供可见性(即GPIO1中断n,n=0-7)。但是,来自其他GPIOx的单个中断指示不可用。

GPIO边缘检测在中断控制单元中进一步描述。

1.1 框图(Block Diagram)

GPIO子系统包含多个GPIO块,可以生成和控制多达32个通用信号。GPIO的框图如所示。

1.2 功能(Features)

GPIO包括以下功能:

- 通用输入/输出逻辑功能:

- 使用数据寄存器(GPIO_DR)驱动特定数据输出

- 使用GPIO方向寄存器控制信号的方向(GPIO_GDIR)

- 通过读取数据,使核心能够对相应输入的状态进行采样焊盘采样寄存器(GPIO_PSR)。

- GPIO中断功能:

- 最多支持32个中断

- 识别中断边缘

- 向SoC中断控制器生成三个活动高中断

2. 外部信号(External Signals)

参见《IMX6ULL参考手册.pdf》。

3. 时钟(Clocks)

这里的表格描述了GPIO的时钟源。

请参阅时钟控制器模块了解时钟设置、配置和门控信息。

| Clock name | Clock Root | Description |

|---|---|---|

| ipg_clk_s | ipg_clk_root | Peripheral access clock |

4. GPIO功能描述(GPIO Functional Description)

4.1 GPIO功能(GPIO Function)

当IOMUX设置为GPIO模式时,GPIO信号可以作为通用输入/输出。每个GPIO信号可以使用GPIO方向寄存器(GPIO_GDIR)独立地配置为输入或输出。

当配置为输出(GPIO_GDIR位=1)时,GPIO数据寄存器(GPIO_DR)中的数据位中的值在相应的GPIO线上被驱动。当信号被配置为输入(GPIO_GDIR位=0)时,可以从相应的GPIO_PSR位读取输入的状态。

4.2 GPIO PAD 架构 (GPIO pad structure)

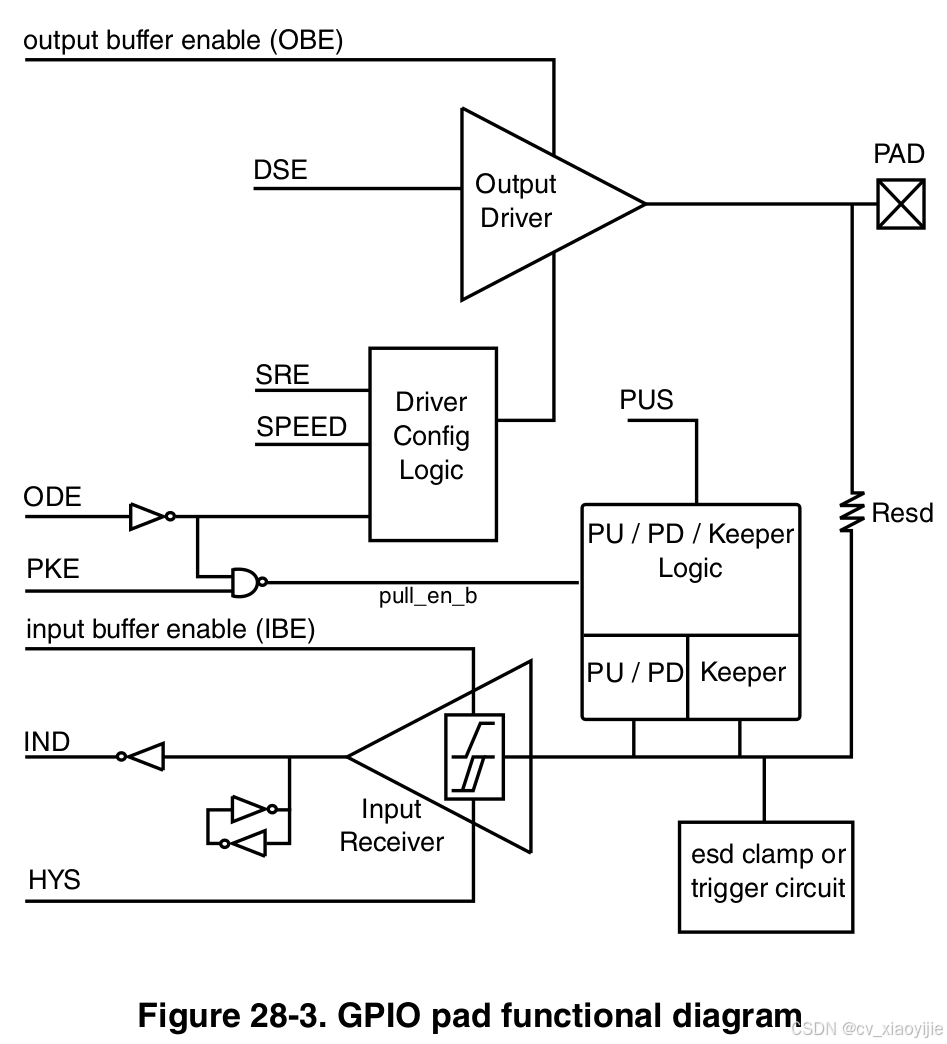

4.2.1 输入驱动器(Input Driver)

输入驱动器特性:

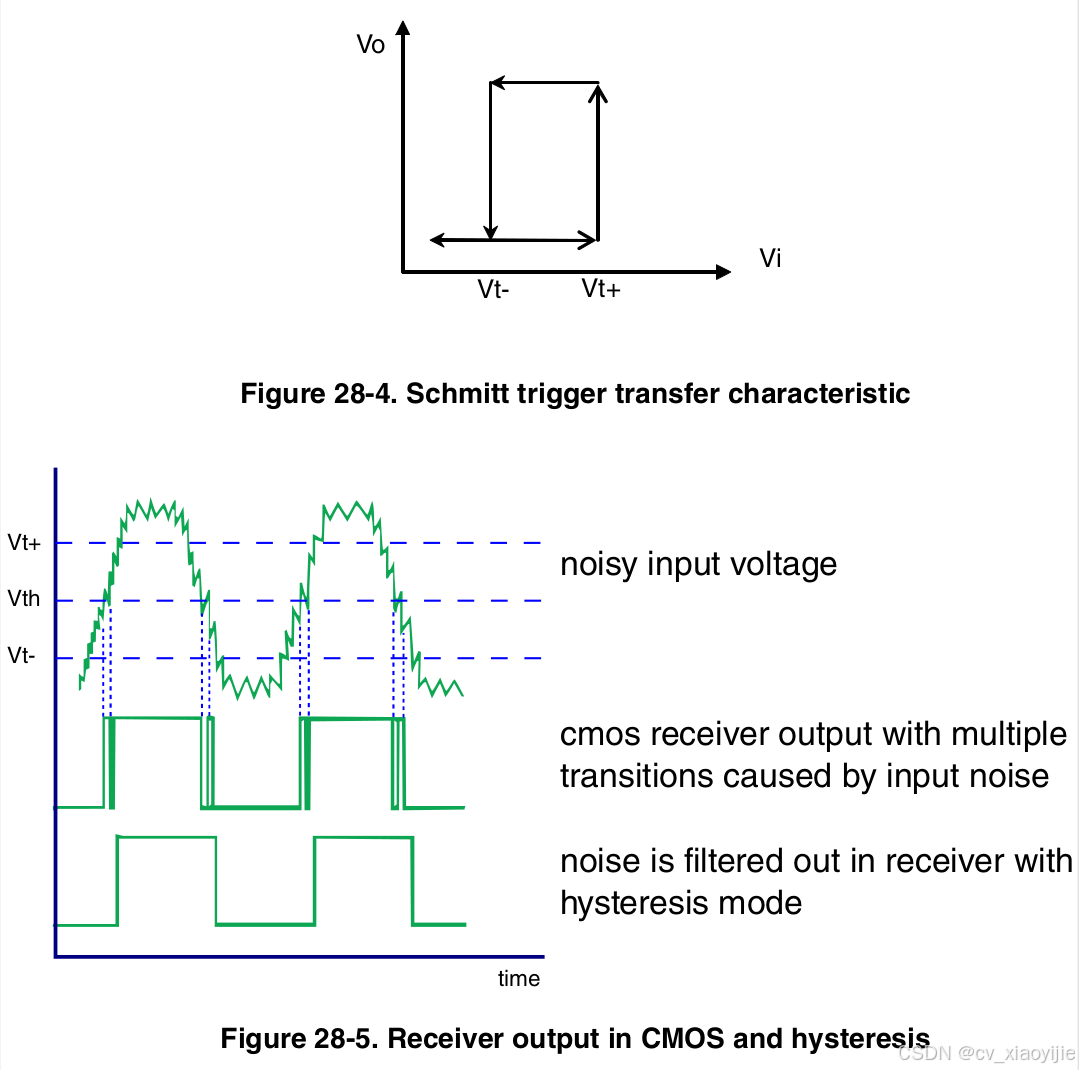

- 可选施密特触发器或CMOS输入模式

- Keeper结构,在Core的输入接收器输出端有缓冲区

- 当I/O电源(OVDD)断电时,接收器处于三态。(接收器输出端的Keeper保持其先前状态)。

4.2.1.1 施密特触发器(Schmitt trigger)

施密特触发器的抗干扰功能如下所示。

4.2.1.2 输入保持器(Input keeper)

一个简单的锁存器,用于在OVDD断电或第一个反相器为三态时保持输入值。所有焊盘的输入缓冲区保持器始终启用。

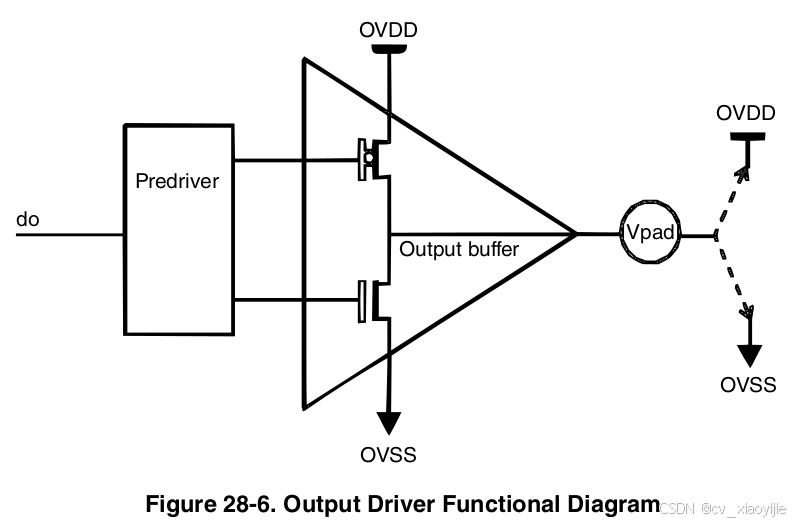

4.2.2 输出驱动器(Output Driver)

输出驱动器特性:

- 可选

CMOS或开漏输出类型 - 可选择的pull-keeper启用信号,以启用/禁用上拉/下拉和输出保持器

- 可选择22K、47K、100K的上拉电阻和100KOhm的下拉电阻。无硅P+多晶硅电阻器用于将电阻变化限制在+/-20%以内。

- 输出模式下禁用上拉、下拉和焊盘保持器。

- 每种操作模式下有七种驱动强度

- 额外的2位转换速率控制,可在50、100和200 MHz IO单元操作范围之间进行选择,同时降低开关噪声

4.2.2.1 驱动强度(Drive strength)

驱动强度选择可用于使阻抗匹配并获得更好的信号完整性。

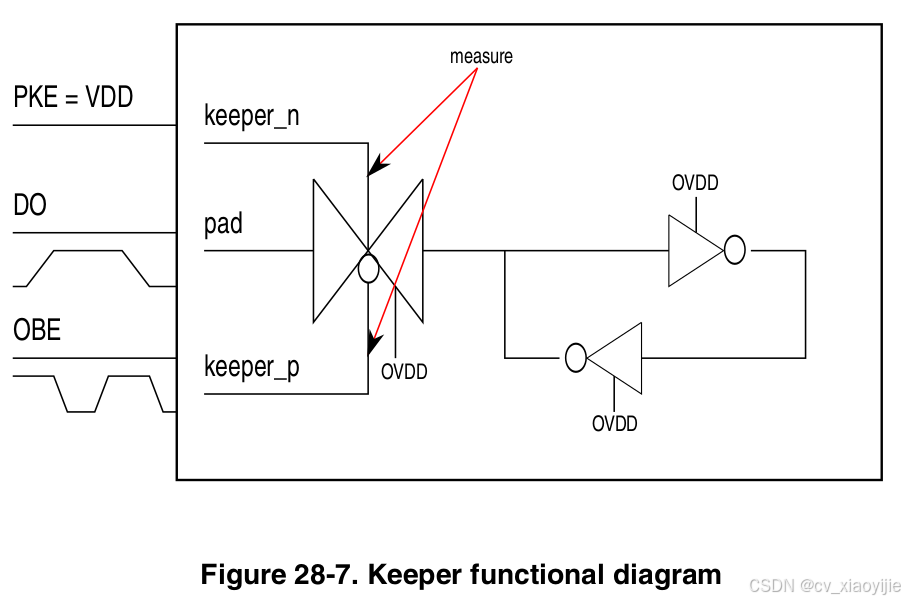

4.2.2.2 输出保持器(Output keeper)

4.2.2.3 上拉/下拉/保持器逻辑(PU / PD / Keeper Logic)

启用Keeper时,上拉和下拉被禁用,焊盘的输出值取决于Keeper。输出保持器由OVDD供电。当核心VDD断电或第一反相器处于三态时,可以保持PAD的状态。

Keeper和Pull不能同时启用。

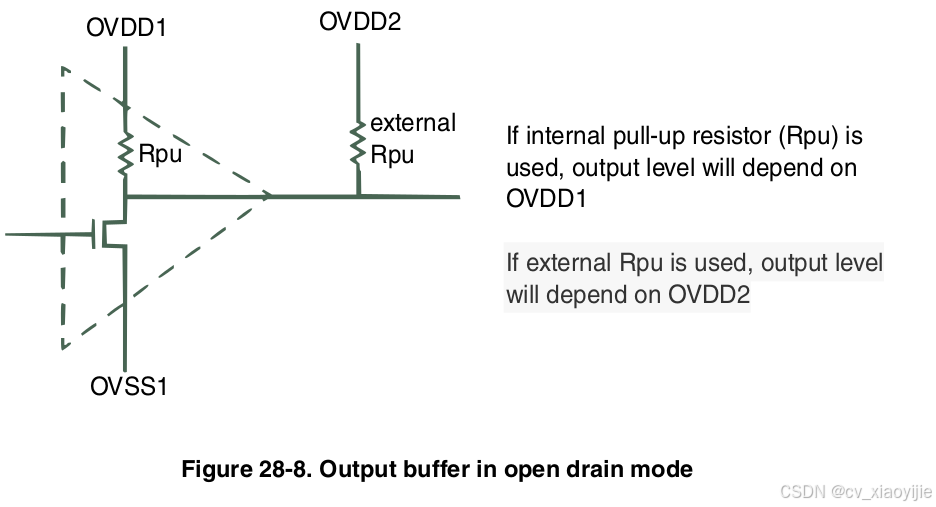

4.2.2.4 漏极开路(Open drain)

漏极开路是一种允许多个设备通过单线双向通信的电路技术。漏极开路驱动器通常与外部或内部上拉电阻器一起工作,该电阻器将信号线保持在高电平,直到设备吸收足够的电流将线路拉低,通常用于具有多个设备的总线。

4.3 GPIO编程(GPIO Programming)

4.3.1 GPIO读取模式(GPIO Read Mode)

读取输入信号的编程顺序应如下:

- 配置IOMUX以选择GPIO模式(通过IOMUX控制器(IOMUXC))。

- 将GPIO方向寄存器配置为输入(GPIO_GDIR[GDIR]设置为0b)。

- 从数据寄存器/焊盘状态寄存器读取值。

当GPIO方向设置为输入(GPIO_GDIR=0)时,对GPIO_DR的读取访问不会返回GPIO_DR数据。相反,它返回GPIO_PSR数据,这是相应的输入信号值。

4.3.2 GPIO写入模式(GPIO Write Mode)

驱动输出信号的编程顺序应如下:

- 配置IOMUX以选择GPIO模式(通过IOMUXC),如果需要通过PSR读取环回焊盘值,还可以启用SION

- 配置GPIO方向寄存器输出(GPIO_GDIR[GDIR]设置为1b)。

- 将值写入数据寄存器(GPIO_DR)。

4.4 中断控制单元(Interrupt Control Unit)

除了通用输入/输出功能外,GPIO外围设备中的边缘检测逻辑还反映了配置为输入(GDIR位=0)的给定GPIO信号是否发生了转换。中断控制寄存器(GPIO_ICR1和GPIO_ICR2)可用于独立配置每个输入信号的中断条件(低到高转换、高到低转换、低或高)。有关GPIO_ICR1和GPIO_ICR2设置的信息,请参阅GPIO内存映射/寄存器定义。

中断控制单元由32个中断控制子单元组成,每个子单元处理一条中断线。

5.GPIO内存映射/寄存器定义(GPIO Memory Map/Register Definition)

参见《IMX6ULL参考手册.pdf》。

946

946

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?