Enhancing Performance with Pipelining

- 重點一:Pipeline

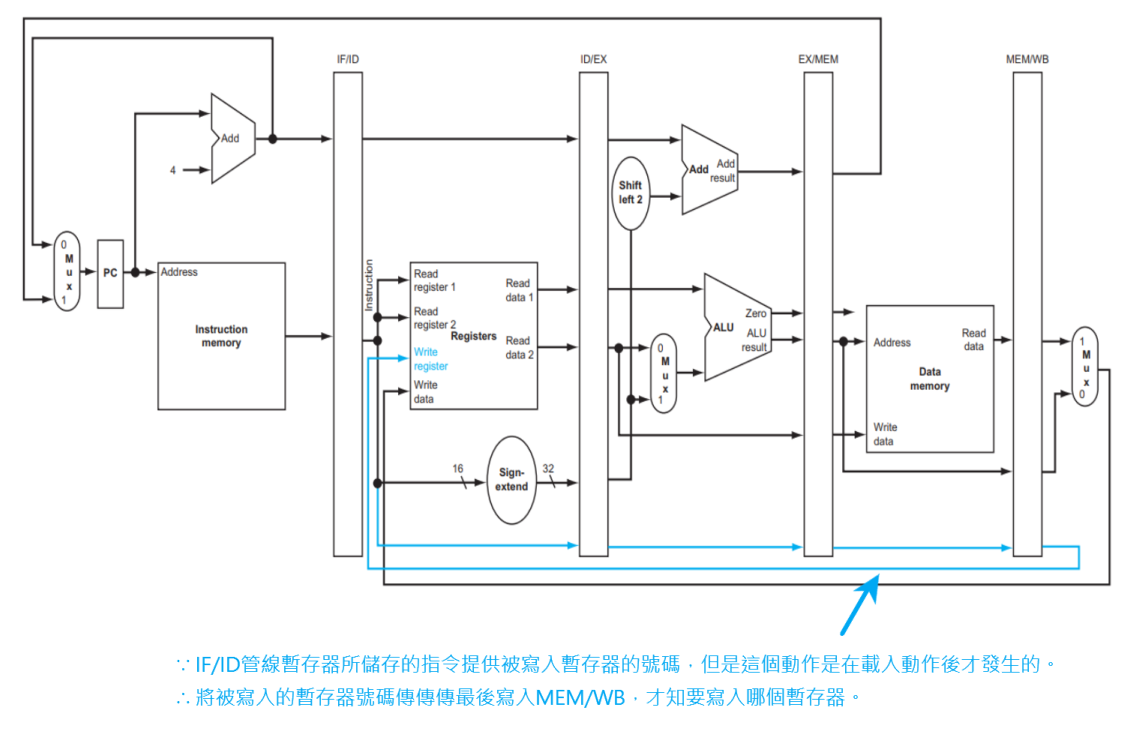

- 重點二:Pipeline datapath

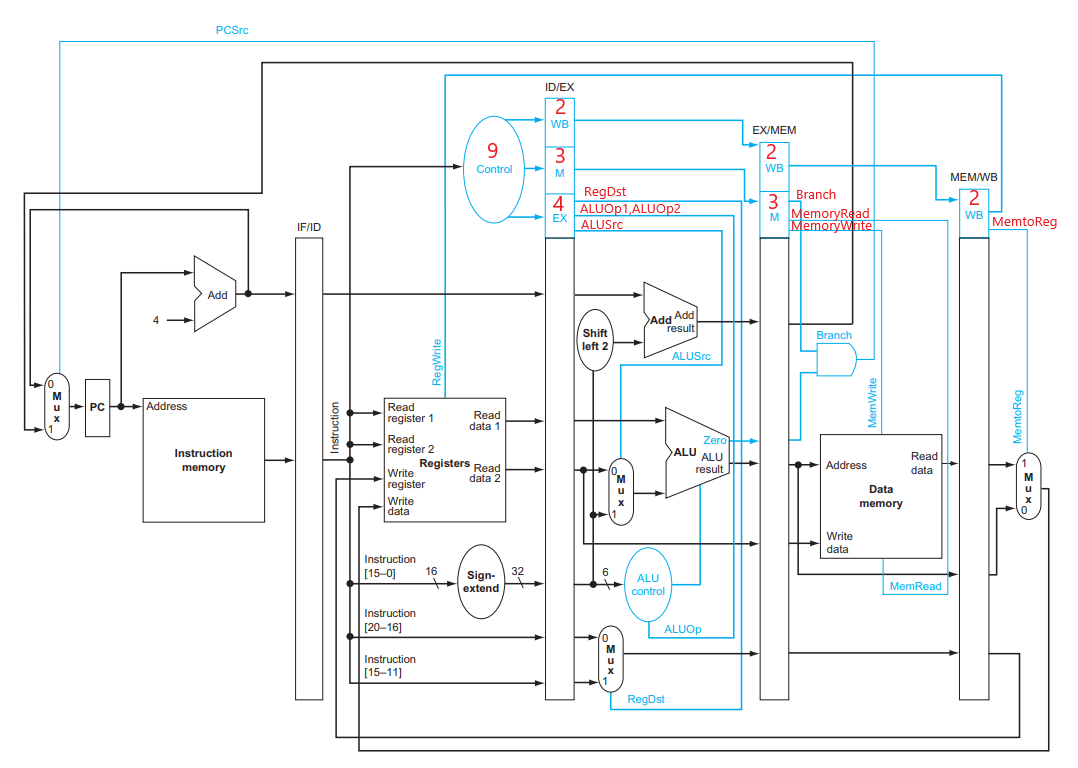

- 重點三:Pipeline Control Unit

- 重點四:Pipeline hazard

- 重點五:Hazard Solution

- 重點六:Data hazard

- 重點七:Data dependency

- 重點八:Control hazard (Branch hazard)

- 重點九:Advanced pipeline

- 重點十:Pipeline Exception Handling

重點一

Pipeline

- 管線化(Pipelining)

- 多個指令重疊執行(Overlap execution),同一時間平行處理不同Stage’s job → 硬體使用率 ↑,throughput ↑

- 將job的執行分成幾個Step,並將執行工作的硬體切割成幾個對應的Stage ( 1 stage execute 1 step )

- 特性

- 不會對個別指令的延遲時間(latency : job真正時間,not延遲時間)有所幫助,但整體指令執行的throughput ↑

- 多個指令同時使用不同資源 → 硬體使用率 ↑

- Potential Speedup = number of pipeline stages

- pipeline rate 受限於最慢pipeline stage的執行時間

- pipeline stage 分割不平衡 → pipeline Speed ↓

- fill & drain pipeline → pipeline Speed ↓

- MIPS

- 所有指令

相同長度( 32bits ) - 少數指令的指令格式中

來源暫存器欄位都在相同位置 - 只有Load & Store 會存取記憶體

運算元(operand)必須在記憶體中對齊(aligned)

- 所有指令

- 理想管線的執行及加速(Far ideal pipeline)

- Execution Time = [(S-1)+ N ] / T

- CPI = [(S-1) + N ] / N ,if N → ∞ , CPI = 1

- Speedup = S × N × T /{ [(S-1) + N ] × T’ } , if N → ∞ ,Speedup = S

- 1個指令花S-1個Clock通過管線,N個指令花(S-1) + N

重點二

Pipeline datapath

重點三

Pipeline Control Unit

本文详细探讨了CPU流水线技术,包括流水线的基本概念、数据通路、控制单元、潜在的危险及解决方案。重点强调了如何通过增加硬件资源、指令重排序和转发来解决结构、数据和控制危害,以提升处理器性能。此外,还介绍了高级流水线技术,如分支预测、超长指令集和异常处理,以实现指令级并行和提高系统效率。

本文详细探讨了CPU流水线技术,包括流水线的基本概念、数据通路、控制单元、潜在的危险及解决方案。重点强调了如何通过增加硬件资源、指令重排序和转发来解决结构、数据和控制危害,以提升处理器性能。此外,还介绍了高级流水线技术,如分支预测、超长指令集和异常处理,以实现指令级并行和提高系统效率。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

584

584

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?