// 1.Enable DMA Clock

RCC->AHBPCENR |= RCC_AHBPeriph_DMA1; // Enable the DMA Clock

//2.Set DMA registers used to default

DMA1_Channel4->CFGR &= (uint16_t)(~DMA_CFGR1_EN); // Disnable the DMA used, to set other registers

DMA1_Channel4->CFGR = 0;

DMA1_Channel4->CNTR = 0;

DMA1_Channel4->MADDR = 0;

DMA1_Channel4->PADDR = 0;

DMA1->INTFCR |= ((uint32_t)(DMA_GIF4 | DMA_TCIF4 | DMA_HTIF4 | DMA_TEIF4)); // Clear the DMA used IRQFlags

//3.Set DMA registers

DMA1_Channel4->PADDR = (uint32_t)(&USART1->DATAR); // Set peripheralADDR

DMA1_Channel4->MADDR = (uint32_t)TxBuffer; // Set memoryADDR

DMA1_Channel4->CFGR |= (uint16_t)DMA_CFGR1_DIR; // Set DIR : MEM -> Peripheral

DMA1_Channel4->CFGR &= (uint16_t)(~DMA_CFGR1_CIRC); // Set DMA execute single operation

DMA1_Channel4->CFGR &= (uint16_t)(~DMA_CFGR1_PINC); // Disable peripheralADDR increment

DMA1_Channel4->CFGR |= (uint16_t)(DMA_CFGR1_MINC); //Enable memoryADDR increment

DMA1_Channel4->CFGR &= (uint16_t)(~DMA_CFGR1_MEM2MEM); // Disable data M2M

DMA1_Channel4->CNTR = (sizeof(TxBuffer) / sizeof(*(TxBuffer)));// Set data lenghth

USART1->CTLR3 |= USART_CTLR3_DMAT;

while(1)

{

DMA1_Channel4->CFGR &= (uint16_t)(~DMA_CFGR1_EN);

DMA1_Channel4->CNTR = (sizeof(TxBuffer) / sizeof(*(TxBuffer)));

DMA1_Channel4->CFGR |= (uint16_t)DMA_CFGR1_EN;

Delay_Ms(1000);

}

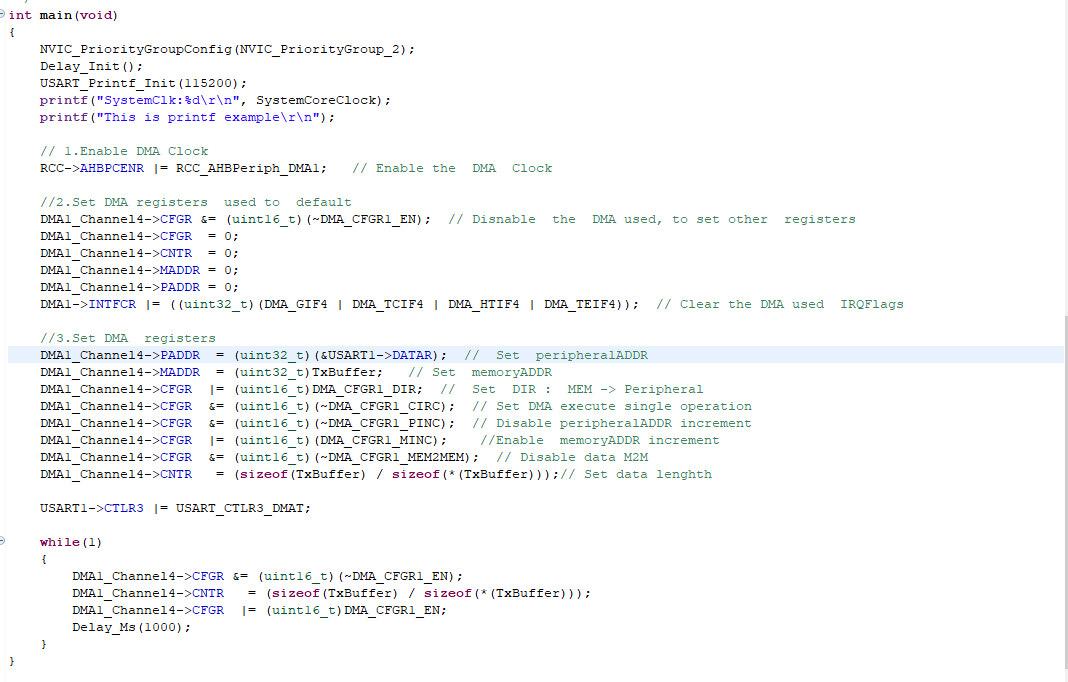

该代码段展示了如何在STM32中启用DMA时钟,配置DMA通道4用于从内存到外设的数据传输,特别是针对USART1的数据发送。设置包括DMA寄存器的初始化,设置传输方向、数据长度和中断标志清除。最后,通过开启和关闭DMA传输来实现定时发送。

该代码段展示了如何在STM32中启用DMA时钟,配置DMA通道4用于从内存到外设的数据传输,特别是针对USART1的数据发送。设置包括DMA寄存器的初始化,设置传输方向、数据长度和中断标志清除。最后,通过开启和关闭DMA传输来实现定时发送。

569

569

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?