文章目录

前言

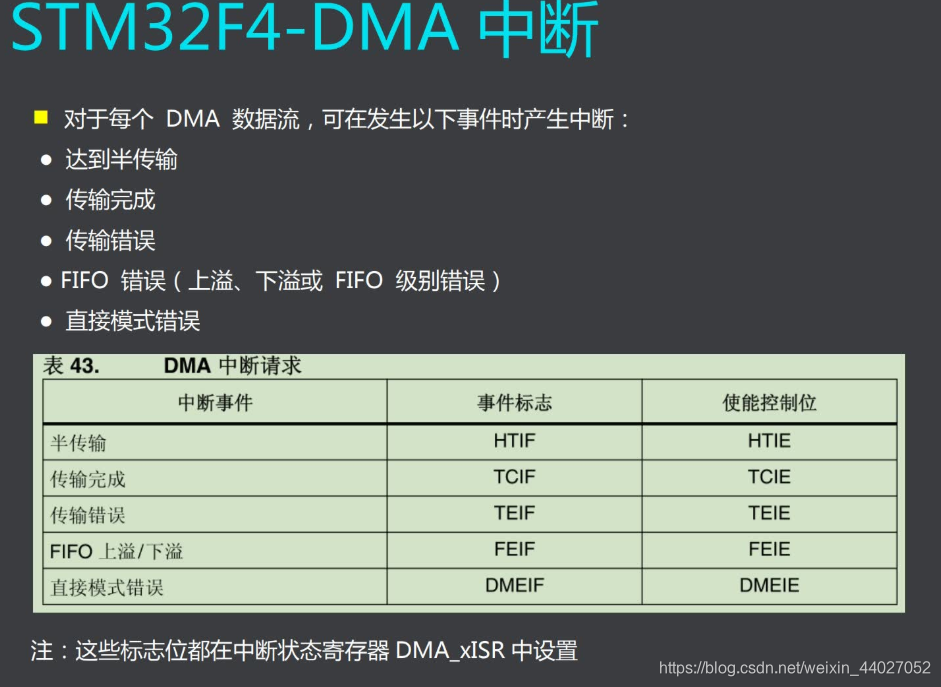

此篇为STM32F407 DMA的学习。

一、pandas是什么?

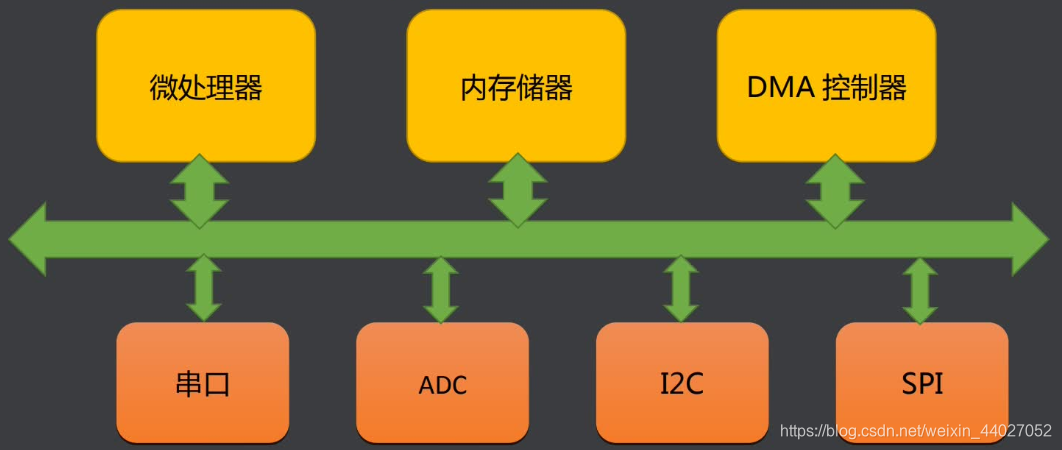

DMA:叫做直接存储器访问,DMA传输方式无需CPU直接控制传输,也没有中断处理方式那样保留现场和恢复现场的过程,通过硬件为RAM与I/O设备开辟一条直接传输数据的通道,从而大大提高CPU工作效率。

二、分布介绍

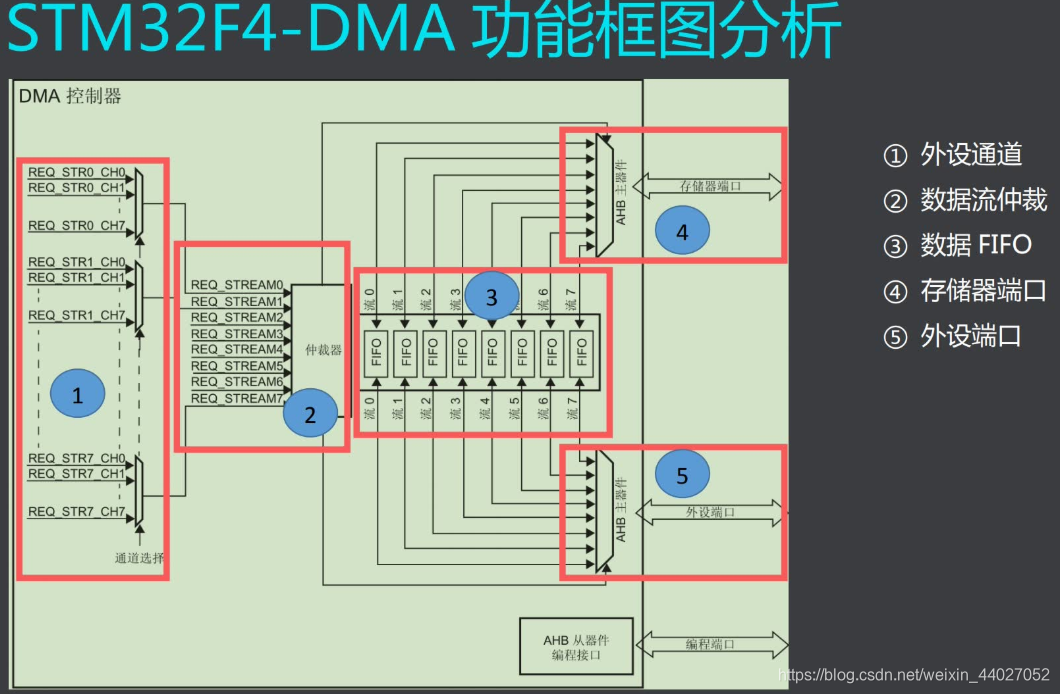

1,外设通道

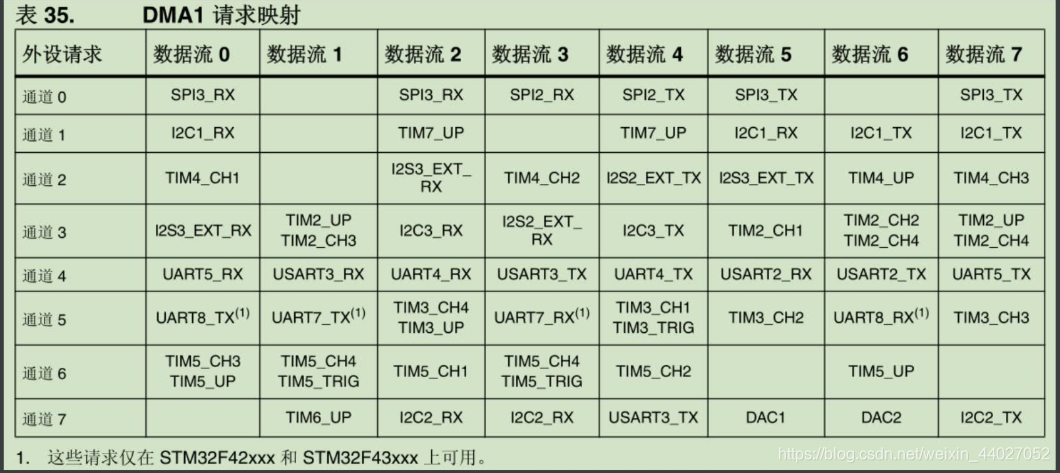

STM32F407系列志愿丰富,具有两个DMA控制器,同时外设繁多,为实现正常传输,DMA需要通道选择控制。每个DMA控制器具有8个数据流,每个数据流对应8个外设请求。

外设通道选择要解决的主要问题是决定哪一个外设作为该数据流的源地址或者目标地址。

注:DMA控制器会通过DMA数据流X配置寄存器DMA_SxCR的CHSEL[2:0]位选择对应的通道作为该数据流的目标外设。

2.数据流仲裁

DMA外设通道

一个DMA控制器对应8个数据流,数据流包含要传输数据的源地址,目标地址,数据长度等待信息,如果我们需要同时使用同一个DMA控制多个外设请求时,那必然需要同时使用多个数据流,那究竟哪一个数据流具有优先传输的权利呢?这就需要仲裁器来管理判断了。

数据流传输优先级配置

1,配置DMA_SxCR寄存器PL[1:0]位,可以设置位非常高,高,中,低四个等级。

2,如果两个或者以上数据流软件设置优先级一样,则他们优先级取决于数据流编号,编号越低越具有优先权。

3,数据FIFO

每一个数据流都有一个独立的4字节FIFO。DMA传输具有FIFO模式和直接模式。

1,直接模式:

每个DMA请求会立即启动对存储器的传输。当在直接模式(禁止FIFO)下,将DMA请求配置为存储器达到外设模式传输数据时,DMA仅会将一个数据从存储器预加载到内部FIFO,从而确保一旦外设触发DMA请求时则立即传输。

2,FIFO模式:

可通过控制寄存器DMA_SxFCR的FTH[1:0]位来设置FIFO阈值级别为FIFO大小的1/4,1/2,3/4.如果数据存储量达到阈值级别时,FIFO内容将传输到目标中。

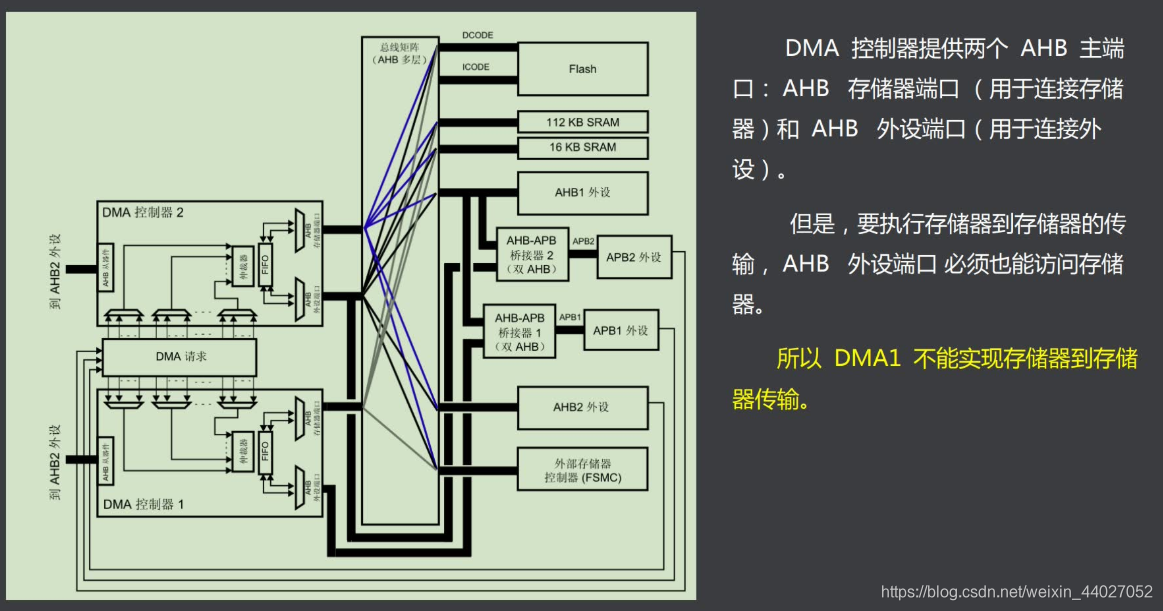

4、5存储器端口和外设端口

DMA传输模式:

DMA1只是外设到存储器和存储器到外设两种模式,DMA2除前面两种外还支持存储器到存储器的传输模式。模式选择可以通过DMA_SxCR寄存器的DIR[1:0]位控制。

DMA传输的源,目的,长度

1,DMA_SxPAR寄存器:设置外设寄存器地址

2,DMA_SxM0AR寄存器:设置存储器地址

3,DMA_SxCR寄存器:DIR[1:0]位配置数据的传输方向

4,DMA_CNDTRx寄存器:写入需要传输的数据量,(0-65535)

5,DMA_SxCR寄存器中的PSIZE和MSIZE位:设置源和目的的数据宽度,两边的位宽尽量保持一致。

DMA增量设置:

根据设置DMA_SxCR寄存器中的PINC和MINC位的状态,外设和存储器指针在每次传输后递增或保持常量。

当设置位增量模式时,下一个传输的地址将是前一个地址的增量值,增量值取决于所选的数据宽度1、2、4。

DMA循环模式:

循环模式用于处理循环缓冲区和连续的数据传输 ( 如 ADC 的扫描模式 ) 。可以使用 DMA_SxCR 寄存器中的 CIRC 位使能此特性。

当启动了循环模式,一组的数据传输完成时,计数寄存器将会自动地被恢复成配置该通道时设置的初值,DMA操作将会继续进行。

DMA单次传输和突发传输

1,DMA传输类型有单次(Single)传输和突发(Burst)传输。DMA 控制器可以产生单次传输或 4 个、8 个和 16个节拍的增量突发传输。

2,突发大小通过软件针对两个 AHB端口独立配置,配置时使用DMA_SxCR 寄存器中的MBURST[1:0] PB

URST[1:0] 位。

3,为确保数据一致性,形成突发的每一组传输都不可分割:在突发传输序列期间,AHB传输会锁定,并且AHB总线矩阵的仲裁器不解除对 DMA 主总线的授权。

1264

1264

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?