在以太网通信中,设备之间的物理层链路均由 PHY 芯片(物理层芯片,本文指 YT8531C/H) 建立。

PHY 芯片有一个配置接口,即 MDIO 接口,可以配置 PHY 芯片的工作模式以及获取 PHY 芯片的若干状态信息。

一、简介

以太网概述

以太网的分类有标准以太网( 10Mbit/s),快速以太网( 100Mbit/s)和千兆以太网( 1000Mbit/s)。

也出现了万兆以太网( 10Gbit/s),它扩展了 IEEE802.3 协议和 MAC 规范,使其技术支持 10Gbit/s 的传输速率。

在实际应用中, 千兆以太网理论上最高通信速率为 1000Mbit/s,可以胜任大部分的使用场景。

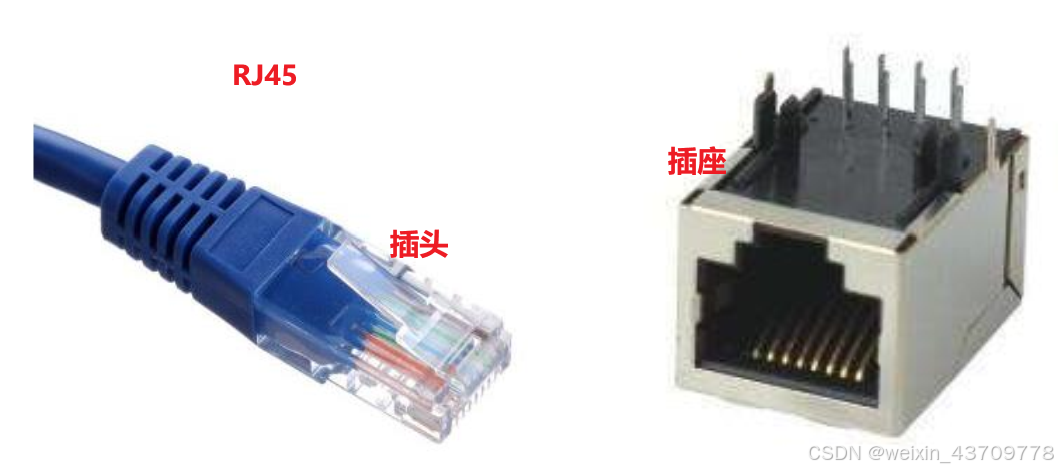

以太网接口类型有 RJ45接口, RJ11 接口(电话线接口), SC 光纤接口等。

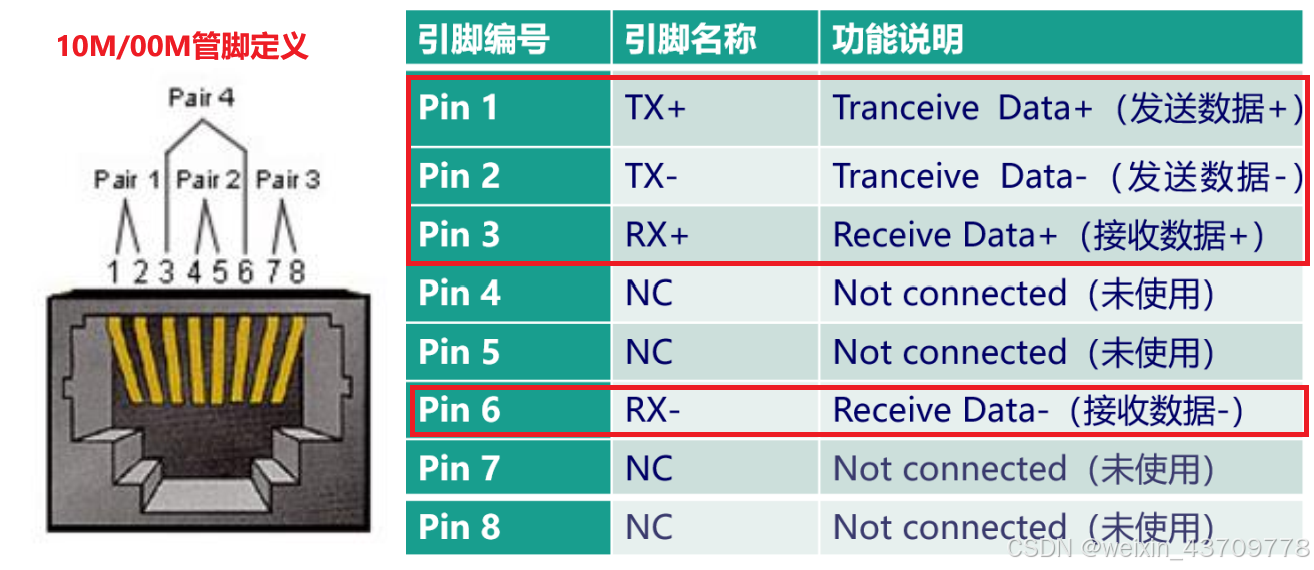

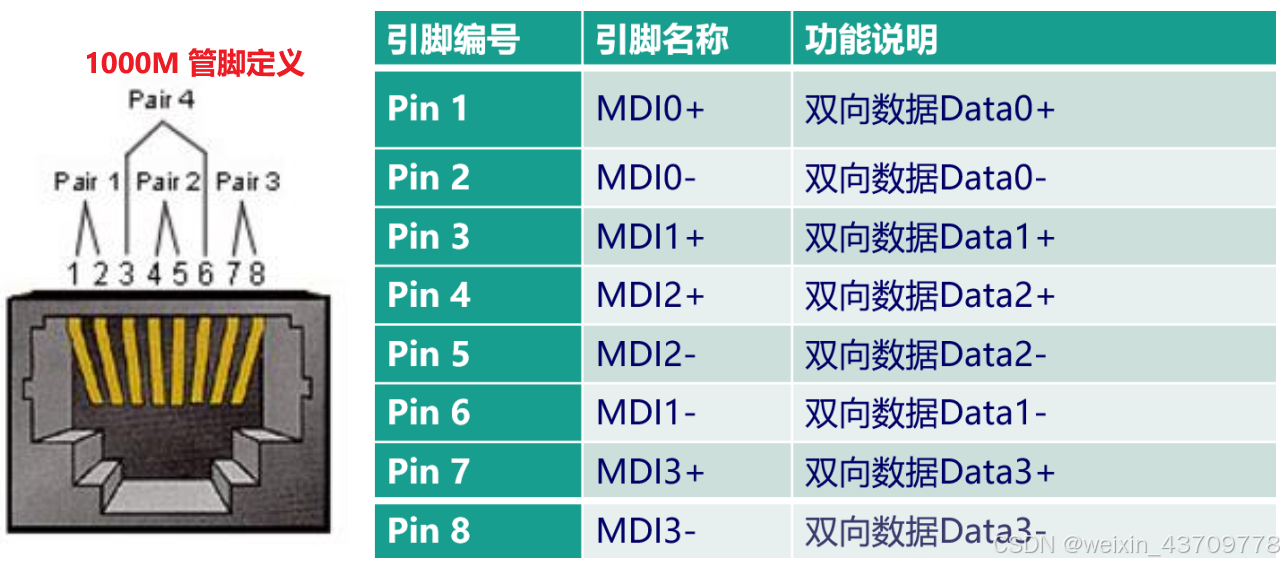

RJ45 接口定义以及各引脚功能在不同通信速率下的定义有区别,

在 10M/100M 通信速率下的定义, RJ45 插座只使用了 1、 2、 3、 6 这四根线,

其中 1、 2 这组负责传输数据( TX+、 TX-),而 3、 6 这组负责接收数据( RX+、 RX-),

另外四根线是备用的。

从硬件的角度来说, 以太网接口电路主要由 MAC( Media Access Control)控制器和物理层接口 PHY ( Physical Layer, PHY)两大部分构成。

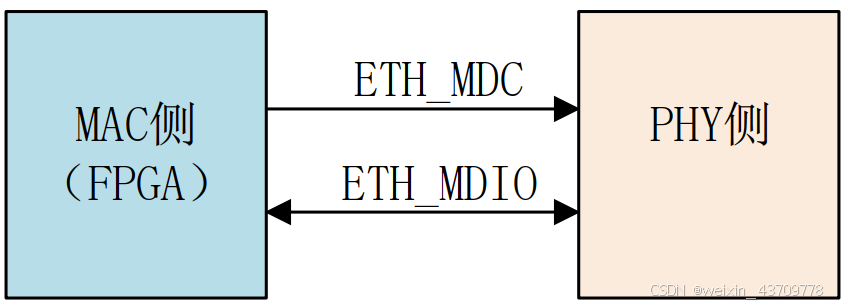

MAC 指媒体访问控制子层协议,它和 PHY 接口既可以整合到单颗芯片内,也可以独立分开,对于本次设计来说, MAC 控制器由 FPGA 实现, PHY 芯片指开发板板载的以太网芯片。

MDIO 接口

MAC 和 PHY 芯片有一个配置接口,即 MDIO 接口,可以配置 PHY 芯片的工作模式以及获取 PHY 芯片的若干状态信息。

PHY 芯片内部包含一系列寄存器,用户通过这些寄存器来配置 PHY 芯片的工作模式以及获取 PHY 芯片的若干状态信息,如连接速率、双工模式、自协商状态等。

FPGA 通过 MDIO 接口对PHY 芯片内部的寄存器进行配置。

通常情况下, PHY 芯片在默认状态下也可以正常工作,在做以太网通信时,对 MDIO 接口的配置不是必须的,本章旨在向大家介绍 MDIO 接口以及如何对 MDIO 接口进行读写操作。

MDIO 接口也称为 SMI 接口( Serial Management Interface, 串行管理接口),包括 ETH_MDC(数据管理时钟)和 ETH_MDIO(数据管理输入输出)两条信号线。

ETH_MDC 为 ETH_MDIO 提供时钟, ETH_MDC 的最大时钟不能超过 12.5Mhz。

ETH_MDIO 为双向数据引脚,既用于发送数据,也用于接收数据。

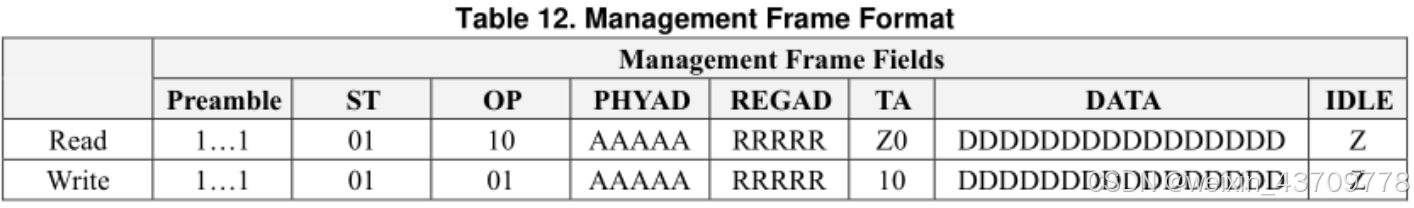

Preamble: 32 位前导码,由 MAC 端发送 32 位逻辑“ 1”,用于同步 PHY 芯片。

ST( Start of Frame): 2 位帧开始信号,用 01 表示。

OP( Operation Code): 2 位操作码,读: 10 写: 01。

PHYAD( PHY Address): 5 位 PHY 地址,用于表示与哪个 PHY 芯片通信,因此一个 MAC 上可以连接多个 PHY 芯片。

REGAD( Register Address): 5 位寄存器地址,可以表示共 32 位寄存器。

TA( Turnaround): 2 位转向,在读命令中, MDIO 在此时由 MAC 驱动改为 PHY 驱动, 在第一个 TA位, MDIO 引脚为高阻状态,第二个 TA 位, PHY 将 MDIO 引脚拉低, 准备发送数据; 在写命令中,不需要 MDIO 方向发生变化, MAC 固定输出 2’b10,随后开始写入数据。

DATA: 16 位数据,在读命令中, PHY 芯片将读到的对应 PHYAD 的 REGAD 寄存器的数据写到DATA 中; 在写命令中, MAC 将要写入对应 PHYAD 的 REGAD 寄存器的值写入 DATA 中。

IDLE:空闲状态,此时 MDIO 为无源驱动,处于高阻状态,但一般用上拉电阻使其上拉至高电平。

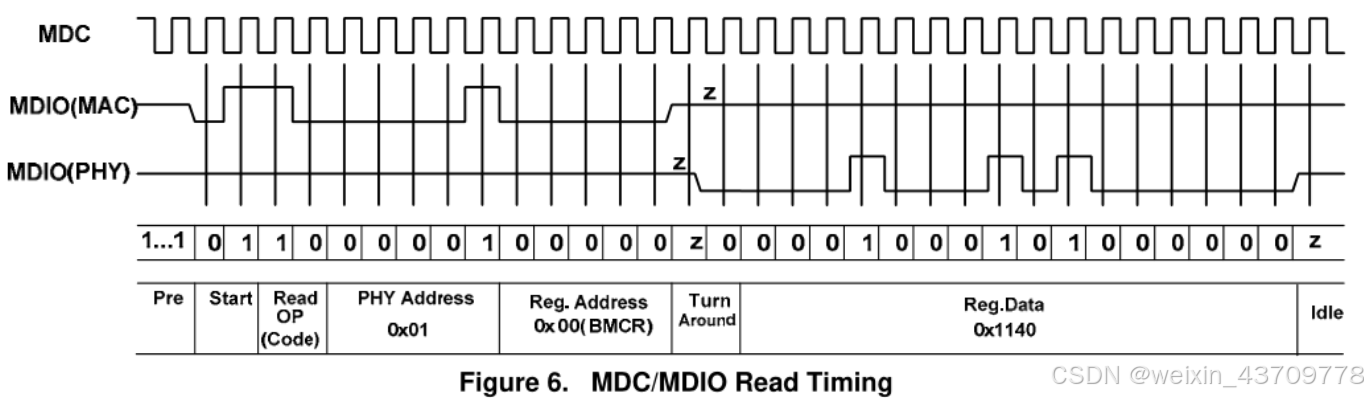

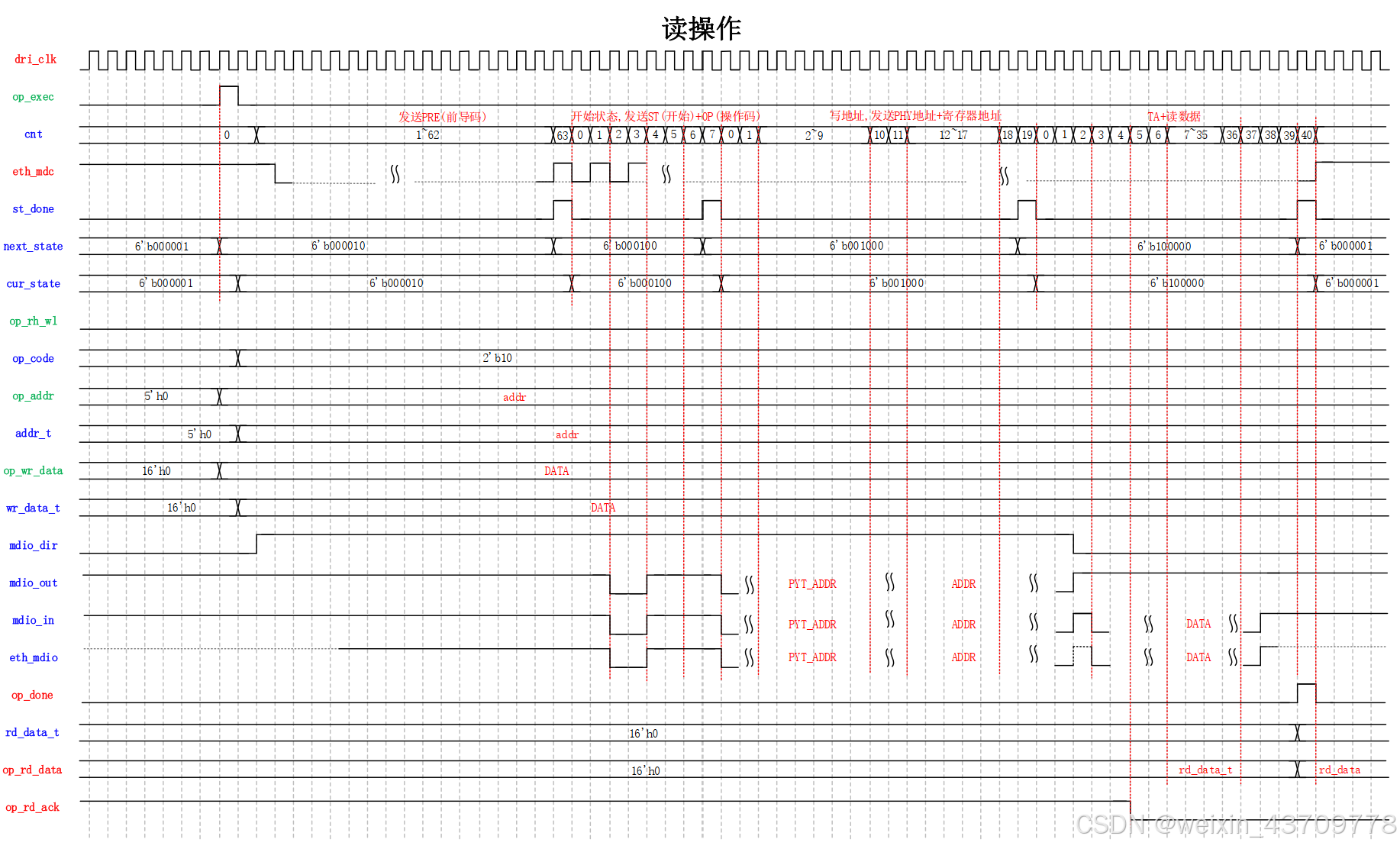

上图是以 PHY 地址为 0x01,从寄存器地址 0x00 读出数据为例。

整个读操作过程的 MDC 时钟由 MAC驱动,同时 MAC 驱动 MDIO 引脚输出前导码+帧开始+操作码+PHY 地址+寄存器地址,随后 MDIO 引脚切换至 PHY 驱动。在第一个 TA 位, MDIO 引脚为高阻状态,第二个 TA 位为低电平,表示 PHY 芯片成功响应,并且接下来会输出 16 位寄存器数据;而如果第二个 TA 位处于高电平,则 PHY 芯片响应失败,有可能 PHY 地址不正确或者其它时序的错误。

需要注意的是, PHY 在 MDC 时钟的上升沿采集数据,为保证数据的稳定传输, MAC 在 MDC 的下降沿更新 MDIO 引脚的数据。当 MDIO 引脚切换至 PHY 驱动时, MDIO 数据在 MDC 时钟的下降沿更新,因此 MAC 在 MDC 时钟的上升沿采集数据。在读操作结束后, MAC 将 MDIO 引脚输出高阻,此时 MDIO 引脚的外部上拉电阻会将 MDIO 引脚拉高,此时 MDIO 接口处于空闲状态。

(MAC向PHY传输数据时,MAC在 下降沿 更新数据,PHY在 上升沿 采集数据;

PHY向MAC传输数据时,MDIO数据在 下降沿 更新,MAC在 上升沿 采集数据;

所以总结:MAC与PHY的数据传输过程,MDIO在MDC的 下降沿 更新,MDIO在MDC的 上升沿 被采集。

下降沿更新、上升沿采集。)

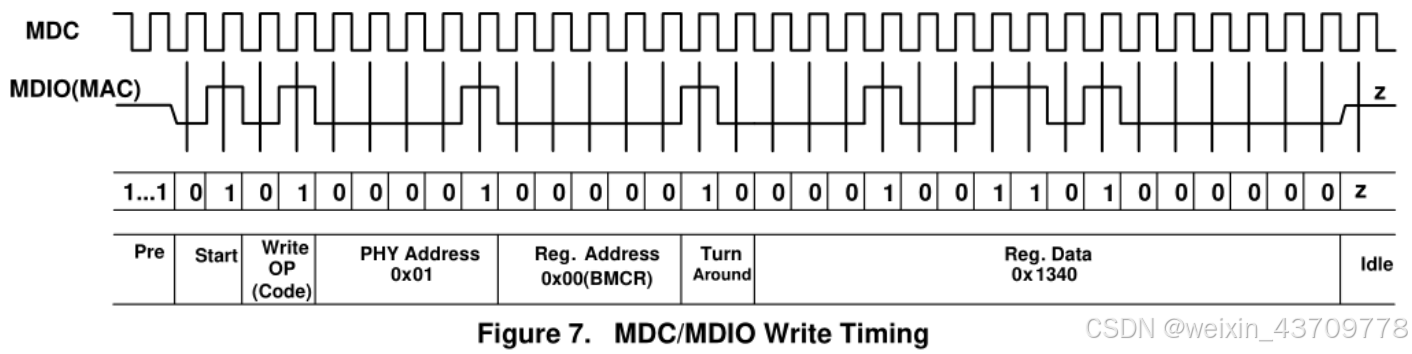

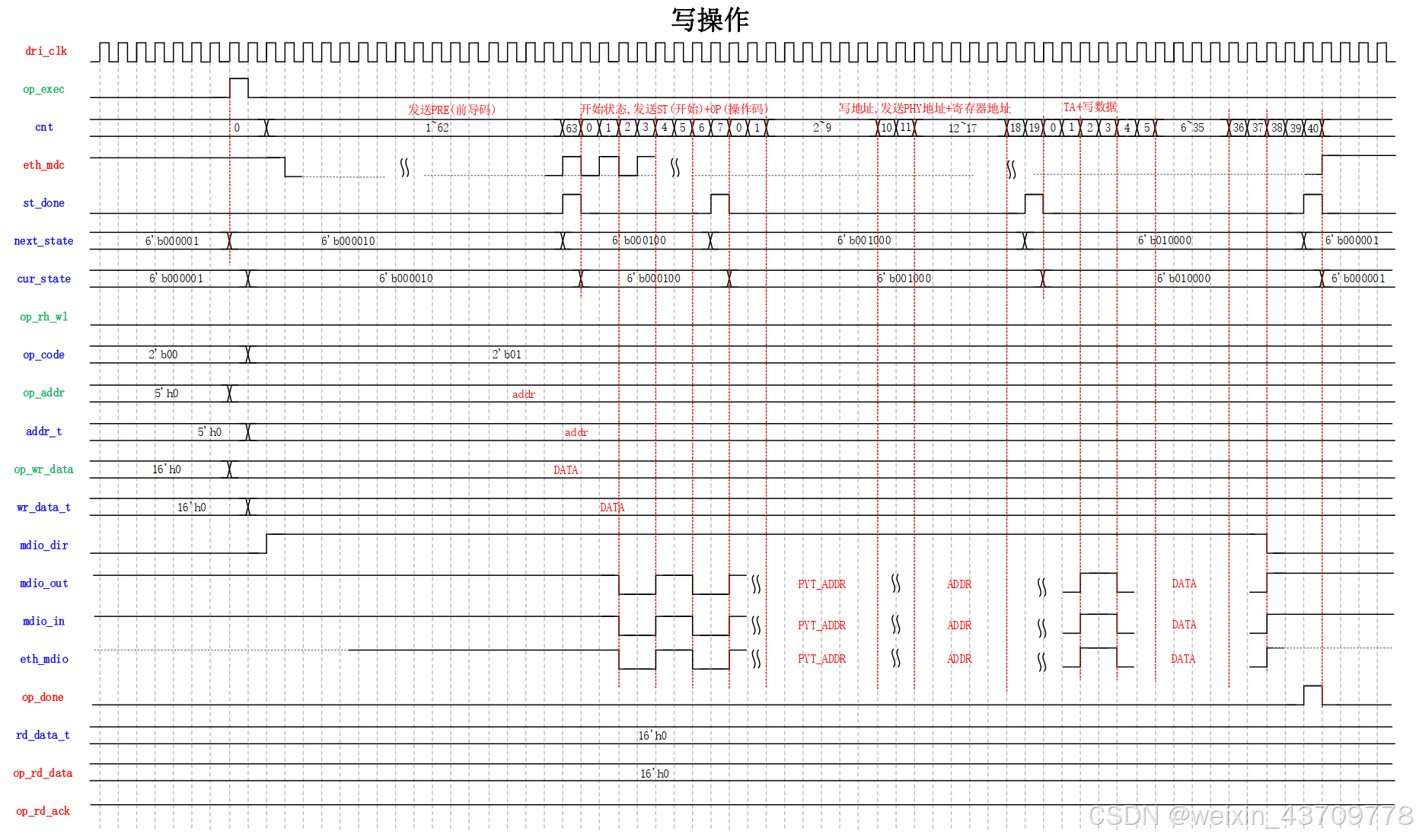

上图是以 PHY 地址为 0x01,向寄存器地址 0x00 写入 0x1340 为例,在整个写操作过程中, MDC 时钟和 MDIO 引脚一直由 MAC 端驱动,按照 MDIO 接口写通信协议开始传输数据。

需要注意的是, PHY 在MDC 时钟的上升沿采集数据,为保证数据的稳定传输, MAC 在 MDC 的下降沿将数据更新至 MDIO 引脚。

在写操作结束后, MAC 将 MDIO 引脚输出高阻,此时 MDIO 引脚的外部上拉电阻会将 MDIO 引脚拉高,此时 MDIO 接口处于空闲状态。

以太网 PHY 芯片( YT8531C/H)

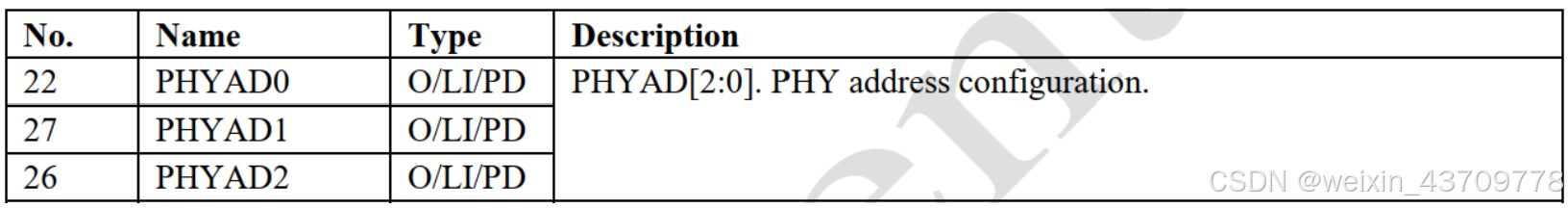

1) PHY 地址

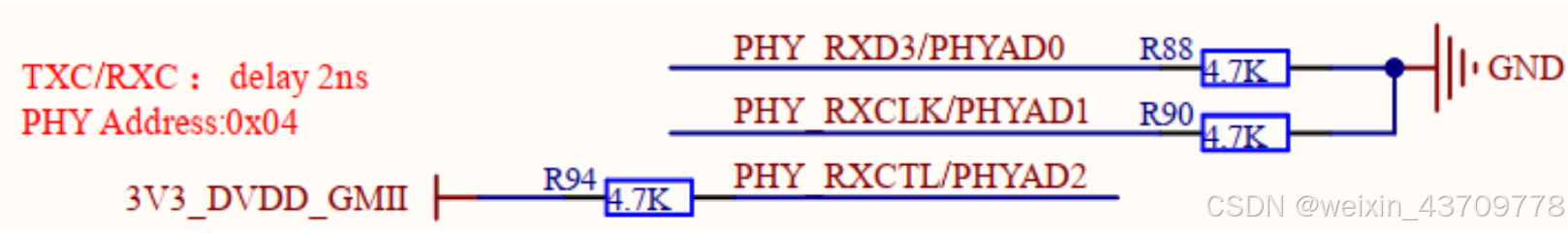

YT8531 芯片的 PHY 地址由 PHYAD0、 PHYAD1 和 PHYAD2 引脚决定,

如下图所示: PHY 地址一共有 3 位,我们可以通过硬件电路设置 PHYAD[2:0]引脚为上拉或者下拉,即分配为高低电平, 0 或 1,从而表示不同的地址。

以太网 PHY 芯片 PHYAD2 接上拉电阻, PHYAD1 和PHYAD0 接下拉电阻,因此 PHY 地址为 5’h04。

2)复位

YT8531 芯片复位后, PHY 内部寄存器的数据会恢复默认的状态,并且重新开始和 MAC 进行自协商。

YT8531 支持两种复位方式,一种是硬件复位,另外一种是软件复位。

硬件复位时通过 PHY_RST_N 引脚实现对 PHY 芯片的复位,当 ETH_RST_N 引脚持续 10ms 的低电平时,即可实现对 PHY 芯片的复位。

软件复位通过向寄存器地址 0x00 的 Bit[15]写入 1 进行复位,并且在完成复位后,该位会自动清零。

3)寄存器

YT8531 共有 22 位寄存器,这里我们仅介绍本实验用到的三个寄存器,控制寄存器、状态寄存器以及PHY 芯片具体状态寄存器。

(常用寄存器:控制和状态。)

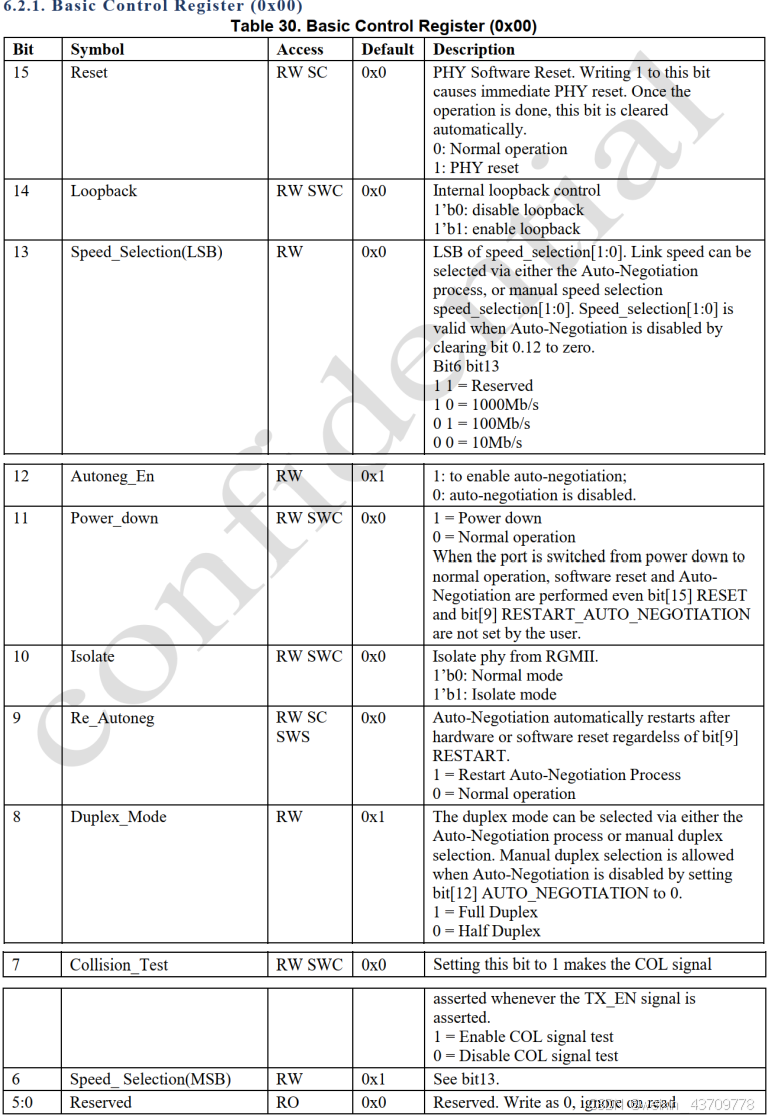

基本控制寄存器(Basic Control Register, Address 0x00),简写为: BCR, 用于芯片的复位和其它功能的控制,各个位的说明如下图所示:

部分常用位的说明如下:

Bit[15]:软件复位, 1: PHY 复位 0:正常模式;

Bit[14]:内部环回模式, 1:内部环回模式 0:正常模式;

Bit[6] Bit[13]:选择网速带宽 ,只有在自动协商使能不开启的情况下有效,

10: 1000Mb/s 01: 100Mb/s

00: 10Mb/s;

Bit[12]:自动协商使能 1:自动协商使能 0:自动协商不使能;

Bit[9]:重启自协商, 1:重新开始自协商 0:自协商重启完成。

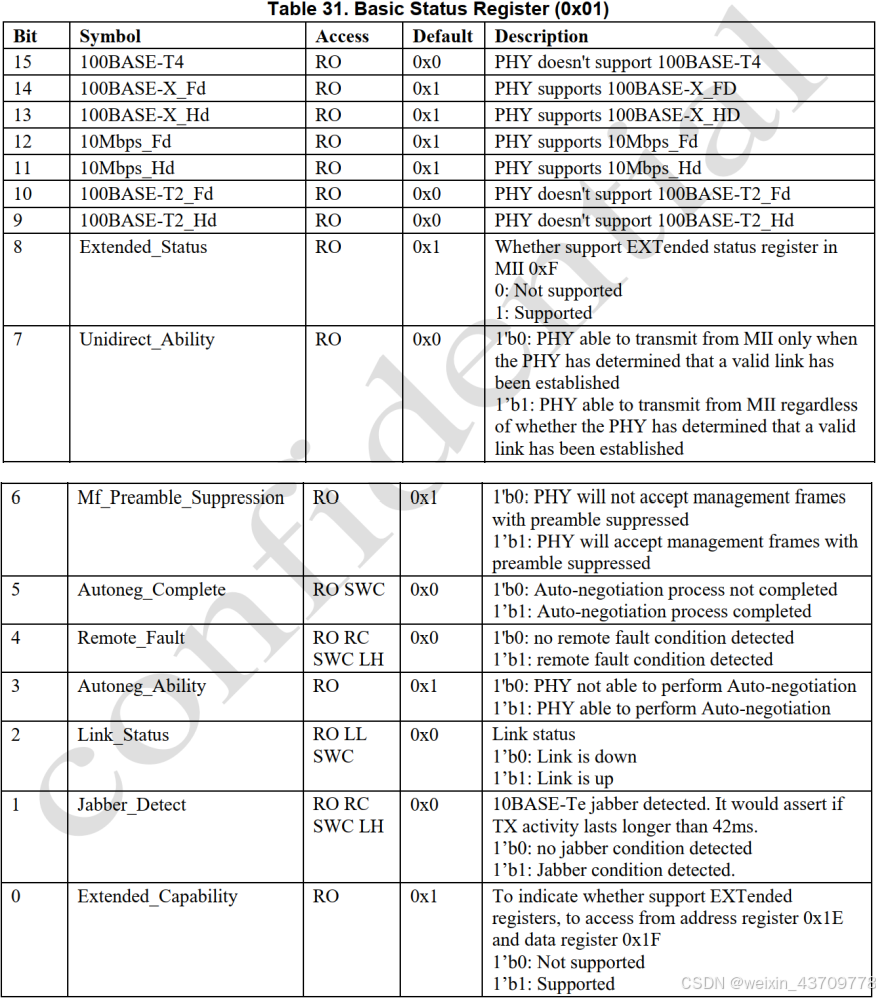

基本状态寄存器(Basic Status Register, Address 0x01), 简写为: BSR,各个位的说明如下图所示:

Bit[5]:自协商完成 1:自协商完成 0:正在进行自协商;

Bit[2]:连接状态, 1:连接成功 0:连接失败。

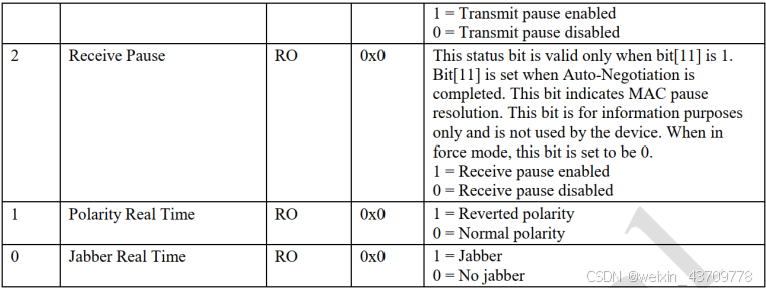

PHY 特定状态寄存器( PHY Specific Status Register , Address 0x11),简写为: PHYSR,各个位的说明如下图所示:

Bit[15:14]:连接速度

11:保留

10: 1000Mbps

01: 100Mbps

00: 10Mbps

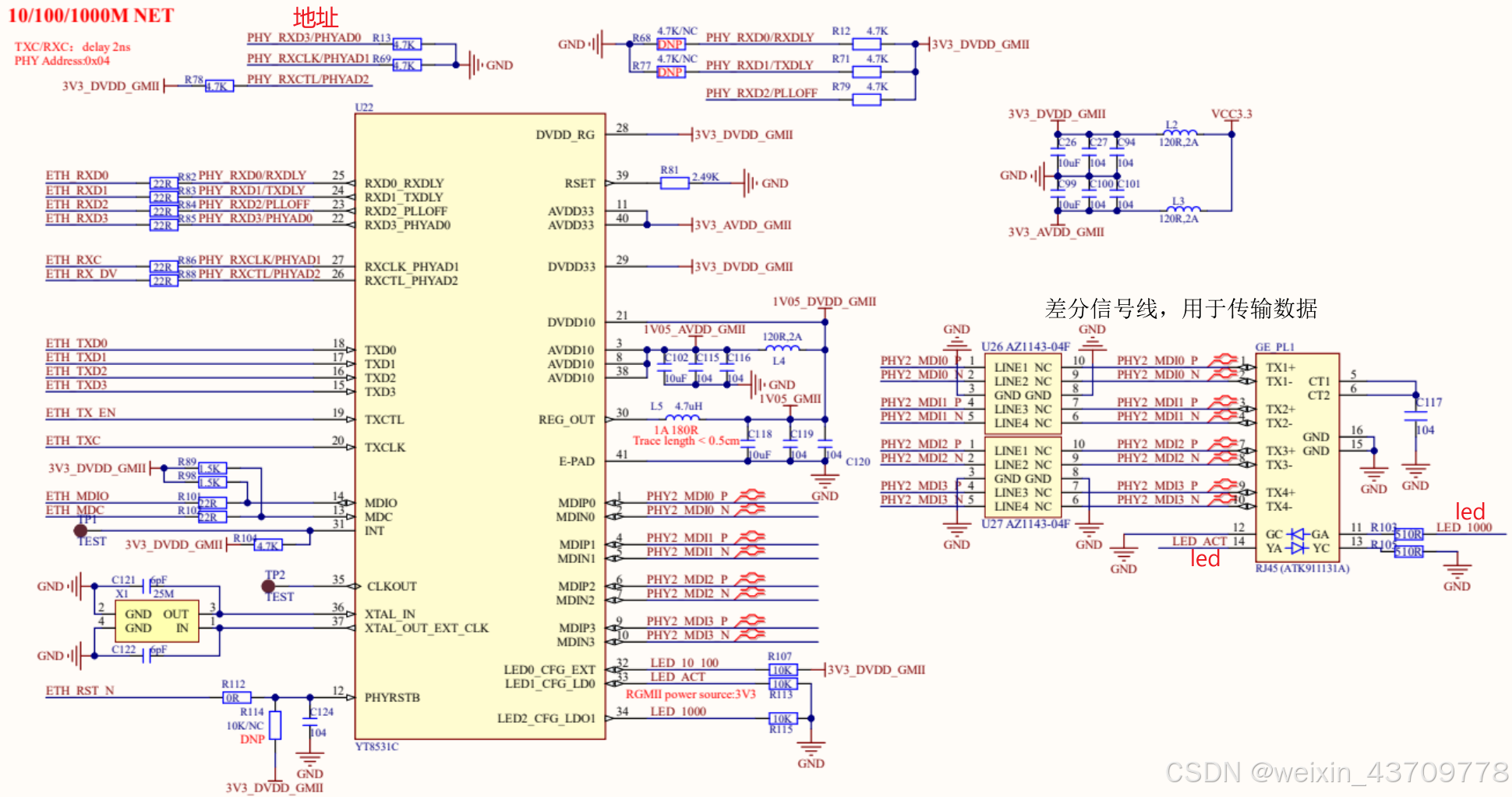

二、硬件设计

上图中的 LED_1000 和 LED_ACT 是 PHY 输出的 LED 信号,用于控制 RJ45 接口上的 LED 灯, MDP0/N0~ MDP3/N3 是 PHY 和 RJ45 接口间的差分信号线,用于传输数据。

以太网的数据传输离不开以太网 PHY(物理层)芯片的支持, 物理层定义了数据发送与接收所需要的电信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。

YT8531 是一个千兆以太网物理层收发器,支持 1000/100/10Mbps 通信速率,该芯片内部的参数可以通过 MDIO 接口进行配置。

由上图可知,以太网 PHY 芯片 PHYAD2 接上拉电阻, PHYAD1 和 PHYAD0 接下拉电阻,因此 PHY 地址为 5’h04。

原理图中的 ETH_MDC 和 ETH_MDIO 引脚均连接了上拉电阻,在空闲状态下,当 FPAG 控制ETH_MDIO 引脚输出高阻状态时, ETH_MDIO 会被上拉至高电平。

三、实验任务

节实验任务是使以太网接口,完成 MDIO 接口的读写测试实验。

板载的触摸按键( TPAD)控制 MDIO 接口进行软复位,并通过两个 LED 灯实时指示当前网口的连接速度。

当 LED0 灯亮的时候,表示当前的网口速率为 10Mbps;

当 LED1 亮的时候,表示当前网口的速率为100Mbps;

当两个 LED 都亮的时候,表示当前网口的速率为 1000Mbps;

当两个 LED 灯都熄灭时,说明当前网络自协商失败,硬件或者网络存在异常。

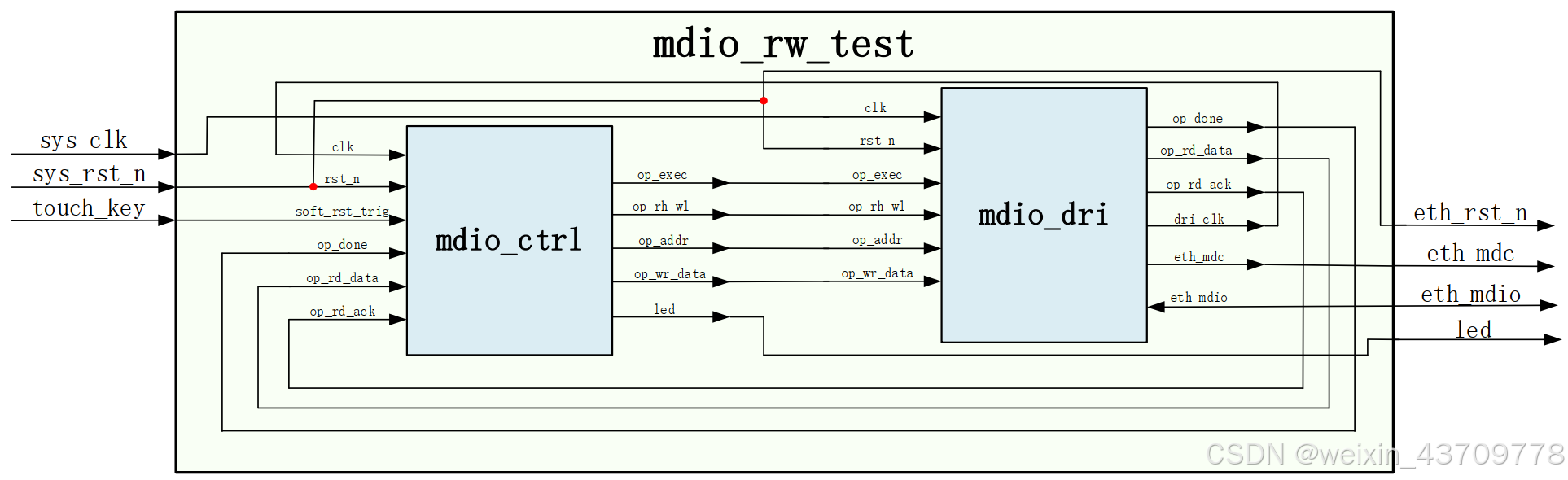

四、程序设计

4.1 整体模块设计

根据实验任务, 因为我们需要对 MDIO 接口进行驱动,所以需要设计一个 MDIO 驱动模块实现了对MDIO 接口的读写驱动。

(数据传输是通过MDIO传输的,读和写操作,所以需要有一个驱动模块。)

我们还需要一个输入的触摸按键的接口,实现了对 MDIO 接口驱动模块的写操作,并每隔一段时间对 MDIO 接口驱动模块进行读操作,将获取到的网口连接状态与速度通过 LED 灯进行指示,所以还需要设计一个 MDIO 接口控制模块。

(要对MDIO模块进行读/写的操作,并且需要led来指示状态,所以需要一个控制模块。)

因为要对MDIO接口进行读写操作,所以有MDIO接口读写(驱动)模块 ;

因为要使用外部按键对PHY进行软件复位,并且使用led指示网络速度,所以需要控制模块;

加上顶层模块,所以一共需要3个模块:

1、顶层模块;

2、驱动模块;

3、控制模块。

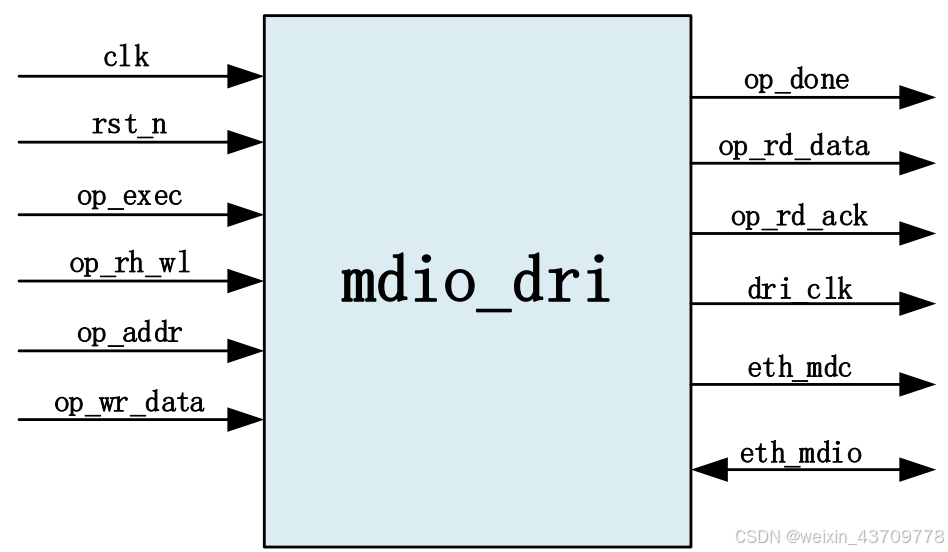

4.2 MDIO驱动模块设计

功能分析

MDIO 驱动模块主要作用是通过 mdio 接口读写 phy 芯片内部寄存器的数据。

输入信号中,

时钟信号 clk,频率 50MHz,作为系统时钟;

复位信号 rst_n,系统复位按键, 低电平有效;

触发开始信号 op_exec, op_exec 默认低电平,当触发信号时, op_exec 拉高,表示 PHY 芯片被触发;

读写信号 op_rh_wl,当 op_exec 被触发后,会根据读写信号 op_rh_wl 的高低电平判断读与写, 低电平进行写操作,高电平进行读操作;

op_addr 为寄存器地址,最大位宽为 5。

输出信号中,

op_wr_data 为向寄存器写入的数据,

op_rd_data 为向读出寄存器的数据,

当写入完成或者读出完成后, op_done 读写完成会拉高一个时钟周期,表示读或者写操作完成。

op_rd_ack 为读应答信号,默认拉高,当进入读操作之后,应答完成后会拉低应答信号,并读取寄存器中的数据。

dir_clk 为驱动时钟,

eth_mdc 为 PHY 管理接口的时钟信号, eth_mdc 是在 dri_clk 的基础上进行分频,一般频率不能超过12.5Mhz。

eth_mdio 为 PHY 管理接口的双向数据信号,既用于发送数据,也用于接收数据。

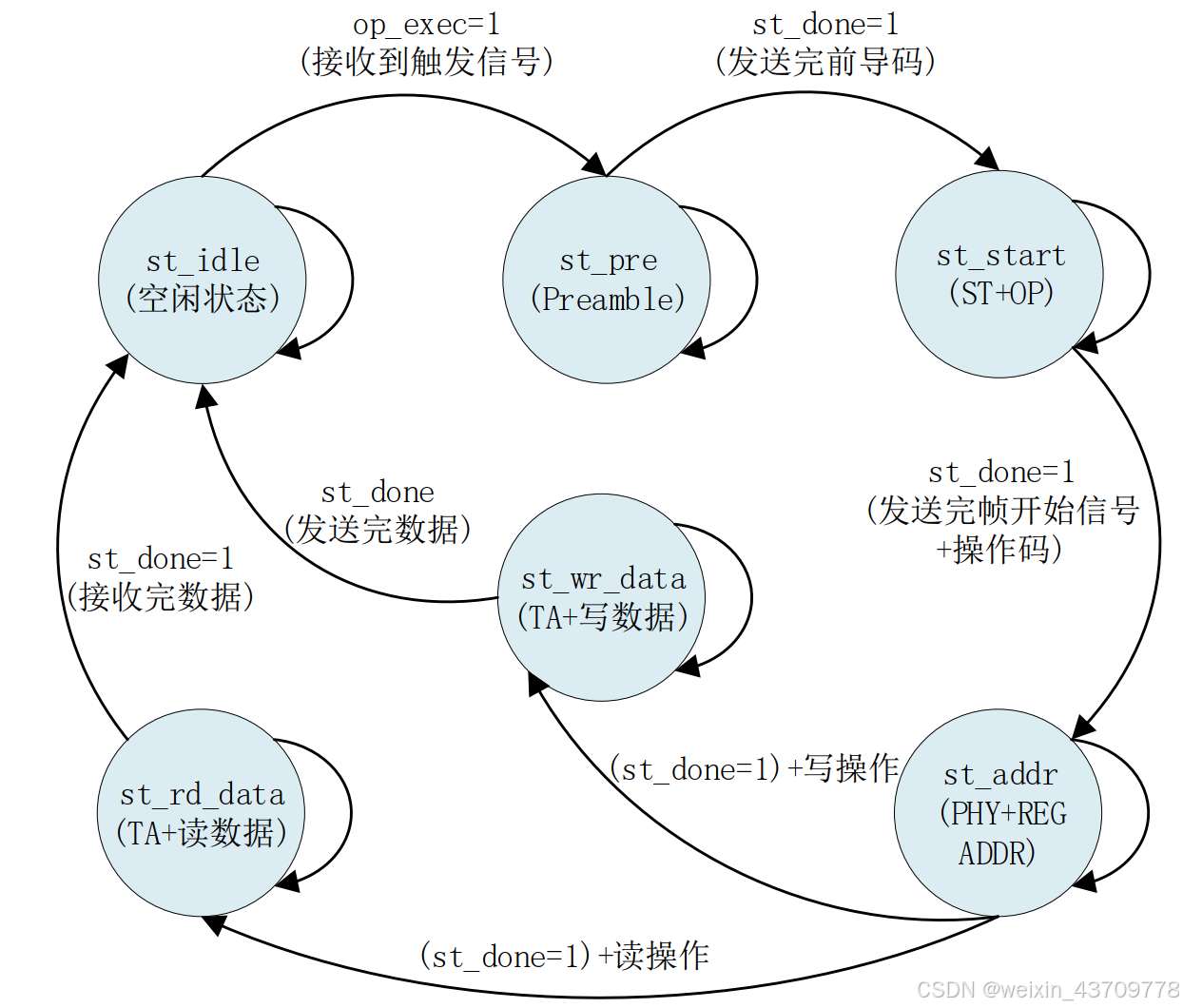

由简介部分 MDIO 接口读写时序图我们可以发现, MDIO 驱动模块非常适合采用状态机来编写。

状态机的跳转图如下图所示,

总共有 6 个状态,分别为 st_idle(空闲状态)、 st_pre(发送前导码状态)、 st_start (发送帧开始+操作码)、 st_addr(发送 PHY 地址+寄存器地址)、 st_wr_data(发送 TA+写入数据)和st_rd_data(接收 TA+接收数据)。

当状态机处于空闲状态时,如果触发信号拉高( op_exec=1),状态机进入发送前导码状态。

另外当状态机处于 st_addr 时,在发送完 PHY 地址和寄存器地址之后,接下来状态机根据读或者写操作来跳转至 st_wr_data 状态或者 st_rd_data 状态。

在读或者写完数据后,状态机重新跳转至空闲状态。

绘制波形图

FPGA 通过 MDIO 控制模块向 MDIO 驱动模块读写数据时,拉高触发控制信号 op_exec 来触发 MDIO驱动模块, op_rh_wl 用于表示读或者写操作,当 op_rh_wl 为低电平时, MDIO 驱动模块执行写操作,当op_rh_wl 为高电平时, MDIO 驱动模块执行读操作。

op_addr 表示读写寄存器地址, op_wr_data 信号表示写入的数据, op_rd_data 信号表示从 MDIO 接口的寄存器中读到的数据。

当读或者写操作完成时, MDIO 驱动模块会产生一个时钟周期的 op_done 信号,表示 MDIO 驱动模块读或者写操作完成。

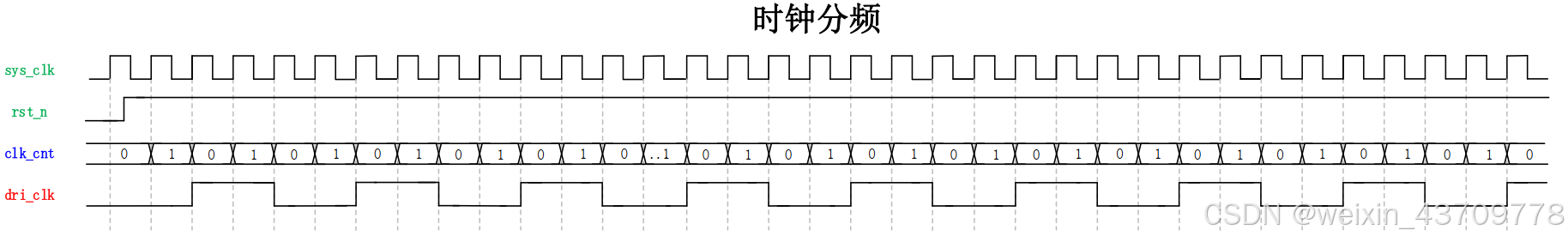

由于 eth_mdc 需要在输入时钟的基础上进行分频,为了方便操作,这里先对输入的时钟进行分频,得到一个 dri_clk 时钟,作为 MDIO 驱动模块和 MDIO 控制模块的操作时钟。

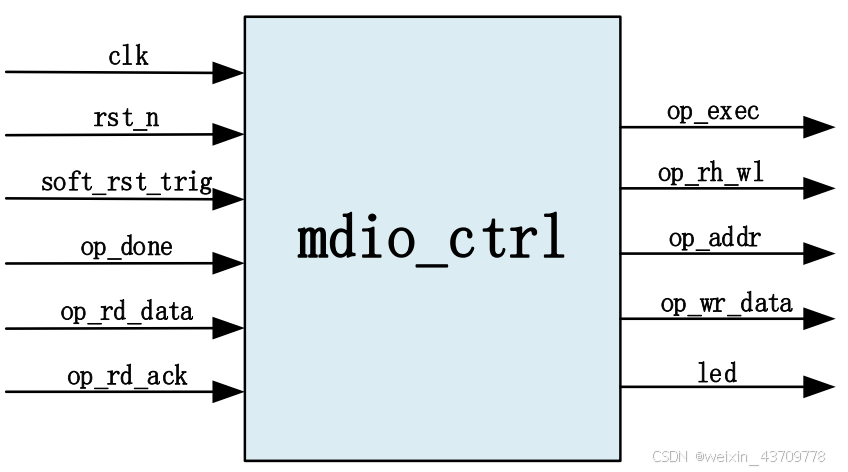

4.3 MDIO控制模块设计

控制模块主要使用板载的触摸按键( TPAD)控制 MDIO 接口进行软复位,并通过两个 LED 灯实时指示当前网口的连接速度。

软件复位:向0x00寄存器的bit[15]写1;

led显示速度:需要读取寄存器0x11的bit[15:14],读取寄存器0x01,获取连接状态;

MDIO控制模块输入输出信号信号功能描述::

| 信号名 | 位宽 | 方向 | 端口说明 |

| clk | 1 | 输入 | 驱动时钟 |

| rst_n | 1 | 输入 | 系统复位按键, 低电平有效 |

| soft_rst_trig | 1 | 输入 | 软复位触发信号 |

| op_done | 1 | 输入 | 读写完成 |

| op_rd_data | 16 | 输入 | 读出的数据 |

| op_rd_ack | 1 | 输入 | 读应答信号 0:应答 1:未应答 |

| op_exec | 1 | 输出 | 触发开始信号 |

| op_rh_wl | 1 | 输出 | 低电平写,高电平读 |

| op_addr | 5 | 输出 | 寄存器地址 |

| op_wr_data | 16 | 输出 | 写入寄存器的数据 |

| led | 2 | 输出 | LED灯指示以太网连接状态 |

输入信号中,

clk 作为驱动时钟,频率 12.5MHz;

复位信号 rst_n,系统复位按键, 低电平有效;

soft_rst_trig 为软复位触发信号,当 soft_rst_trig 被按下,会进行软件复位,在软复位完成后判断 MDIO 链路是否正常并且进行自协商。

op_done 为读写完成信号,当 op_done 拉高时,表示完成一次读或者写的操作;

op_rd_data 为读出的数据,

op_rd_ack 为读应答信号,当 op_rd_ack 拉低是表示读应答响应。

输出信号中,

op_exec 为触发开始信号,当 soft_rst_trig 被按下或者定时信号拉高, op_exec 则会被触发。

op_rh_wl 为读写信号, op_rh_wl 低电平写入,高电平读取。

op_addr 为寄存器地址,

op_wr_data 为写入寄存器的数据,

led 为 LED 灯指示以太网连接状态, LED 会根据以太网连接的状态显示对应的通讯速率。

4.4 顶层模块设计

顶层模块主要是对各个子功能模块的实例化,以及对应信号的连接。

2021

2021

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?