项目名称

流水灯

具体要求

4个led每隔0.5s循环点亮,1-2-3-4-3-2-1,假设高电平状态下流水灯点亮,初始值led=1000

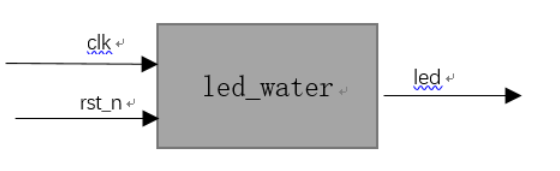

设计架构

需要计数500_000_000/20=25000_000次,由于仿真时间较长,将计数值改为10

代码设计

verilog代码设计

采用状态机实现,从左到右和从右到左两个显示状态

需要注意的是从左到右显示到最后一个0001的时候,要在此状态下将显示状态改变为0010才可以跳转从右到左显示

同样从右到左显示到1000的时候,也需要在此状态下将显示状态改变为0100

module led_water

#(parameter delay_top=25'd25000000)

(

input clk,

input rst_n,

output reg[3:0]led

);

//延迟电路设计计数25000000

reg [24:0] cnt;

always@(posedge clk or negedge rst_n)

if(!rst_n)

cnt<=25'd0;

else if(cnt<delay_top)

cnt<=cnt+1'd1;

else

cnt<=25

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3194

3194

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?