文章目录

五、Cortex-M3设计综述

本章主要面向片上系统(SoC)设计人员,他们可能会有兴趣将Cortex-M3用于他们的工程中。普通的微控制器用户则无须了解这些细节,不过,若对Cortex-M3处理器内部操作感兴趣,本章可以提供处理器设计的概况。

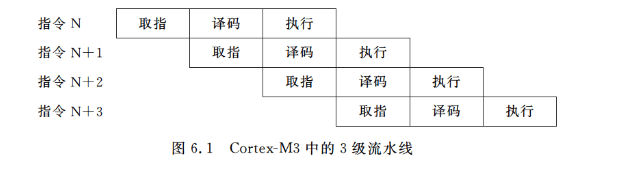

5.1 流水线

Cortex-M3具有三级流水线,三个阶段分别为取指、指令译码和指令执行(见图6.1)。

由于访问存储器时总线接口的流水线行为,有些人可能会认为应该为四个阶段。不过,这个阶段是处理器外部的,因此处理器本身还是只有三个阶段。

当运行的程序多是16位指令时,你会发现处理器可能不会在每个周期都取指令。这是因为处理器每次最多取出2个指令(32位),那么当一个指令取出后,下一条已经在处理器里了。在这种情况下,处理器总线接口可能会下次才取指,或者若缓冲满,总线接口可能会处于空闲状态。有些指令的执行需要花费多个周期,在这种情况下,流水线就会暂停。

在执行跳转指令时,流水线会被清空。处理器必须从跳转目的取出指令以填充流水线。不过,Cortex-M3处理器支持v7-M架构的多个指令,因此,有些小范围的跳转可能会被条件执行代码代替。

由于处理器的流水线特性,要保证程序同Thumb代码兼容,在指令执行期间读取程序计数器时,读出值需要为指令的地址加4。如果利用程序计数器生成存储器访问的地址,就会使用指令地址加4的字对齐值,偏移为常量,而不管16位Thumb指令和32位Thumb2指令如何组合。这样也就保证了Thumb和Thumb2的一致性。

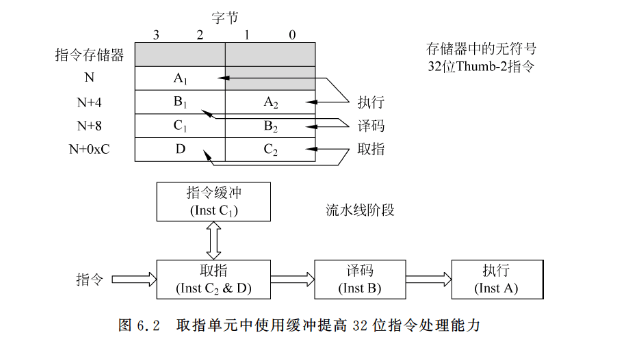

在处理器内核的指令预取单元中,也存在一个指令预取缓冲(见图6.2),其可以让指令在使用前排队等候。在指令序列中包含的32位Thumb2指令若有非字对齐的,该缓冲可以避免流水线暂停。不过,该缓冲不会增加额外的流水线阶段,因此不会增加跳转开销。

5.2 详细框图

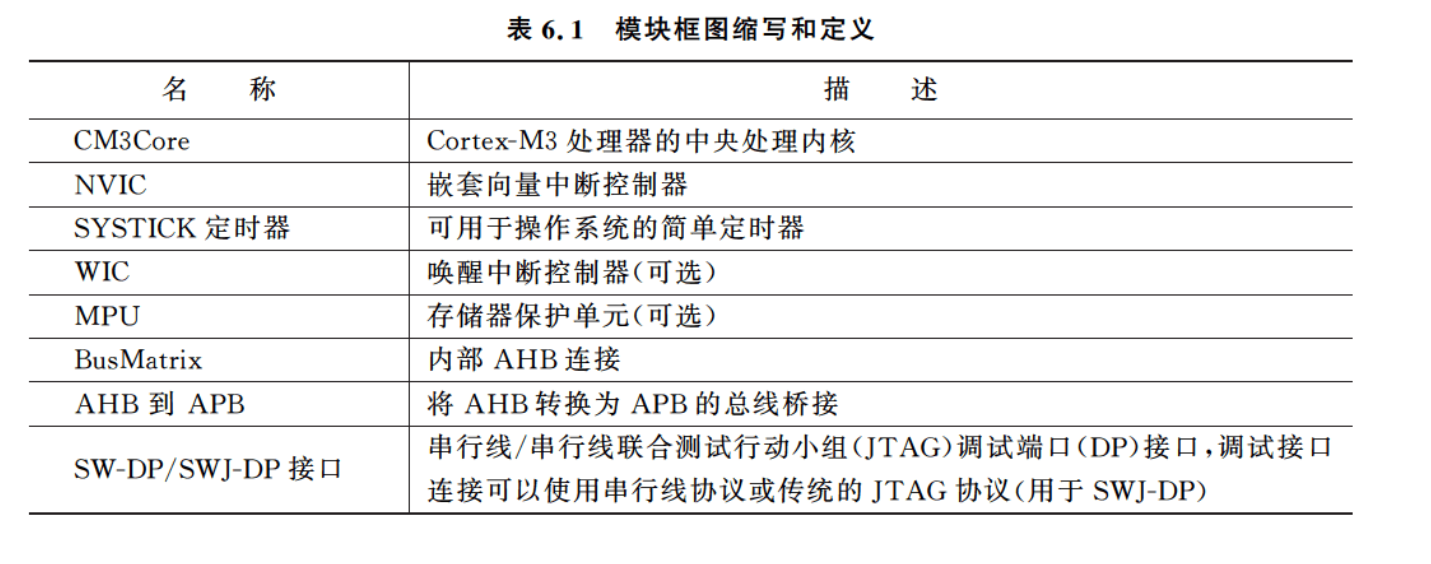

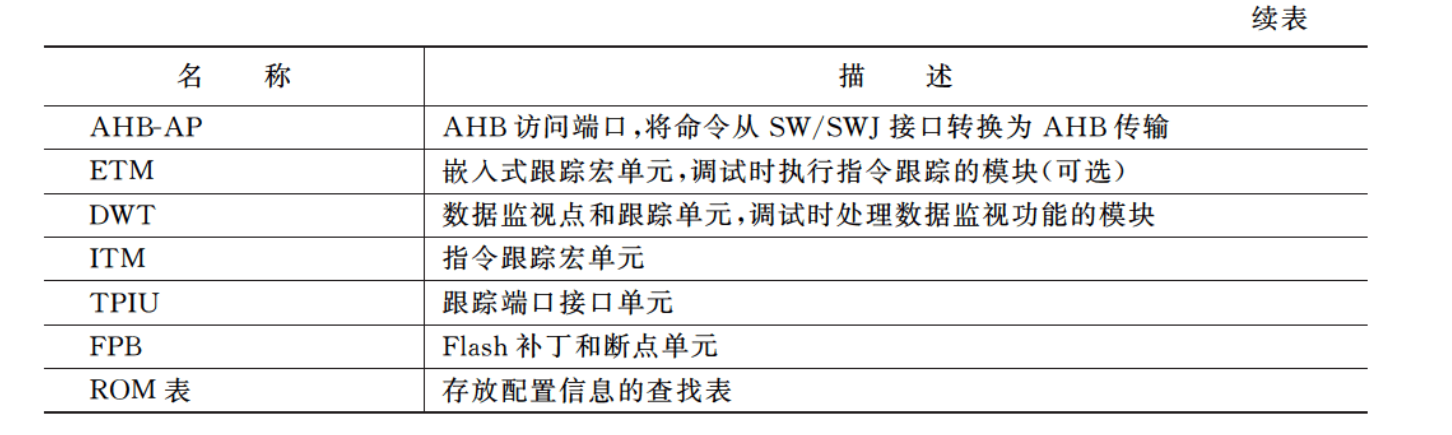

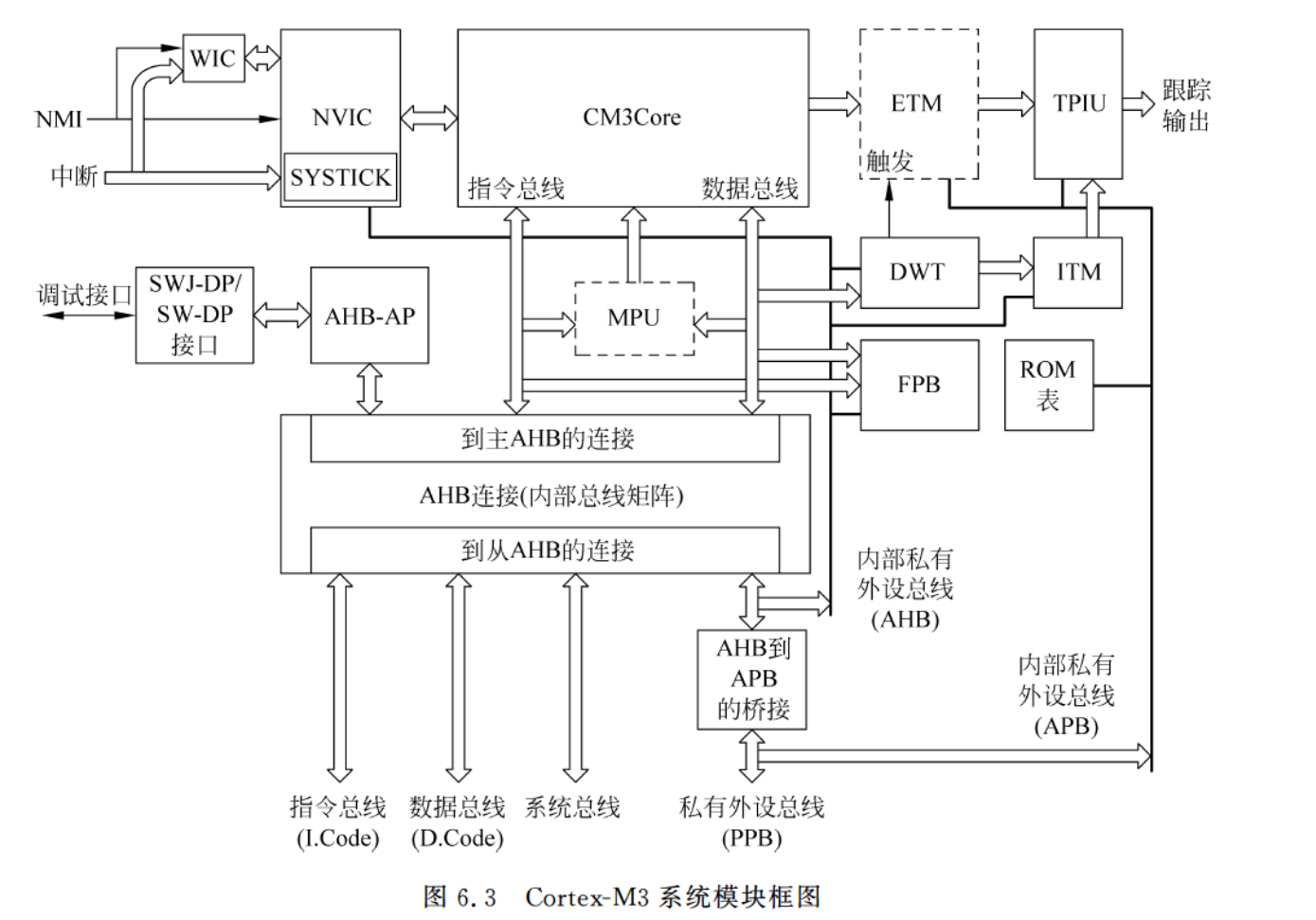

Cortex-M3处理器内不仅有处理器内核,还包含多个用于系统管理的部件以及调制支持部件(见图6.3)。这些部件使用高级高性能总线(AHB)以及高级外设总线(AHB)相互连接,AHB和APB为高级微控制器总线架构(见《Advanced Microcontroller Bus Architecture,AMBA》,参考文献[4])标准的一部分。

应该注意的是,MPU、WIC和ETM为可选模块,它们可以在实现阶段包含在微控制器中。表6.1中列出了多个新部件。

Cortex-M3处

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2722

2722

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?