题目

Synchronous HDLC framing involves decoding a continuous bit stream of data to look for bit patterns that indicate the beginning and end of frames (packets). Seeing exactly 6 consecutive 1s (i.e., 01111110) is a “flag” that indicate frame boundaries. To avoid the data stream from accidentally containing “flags”, the sender inserts a zero after every 5 consecutive 1s which the receiver must detect and discard. We also need to signal an error if there are 7 or more consecutive 1s.

Create a finite state machine to recognize these three sequences:

0111110: Signal a bit needs to be discarded (disc).

01111110: Flag the beginning/end of a frame (flag).

01111111…: Error (7 or more 1s) (err).

When the FSM is reset, it should be in a state that behaves as though the previous input were 0.

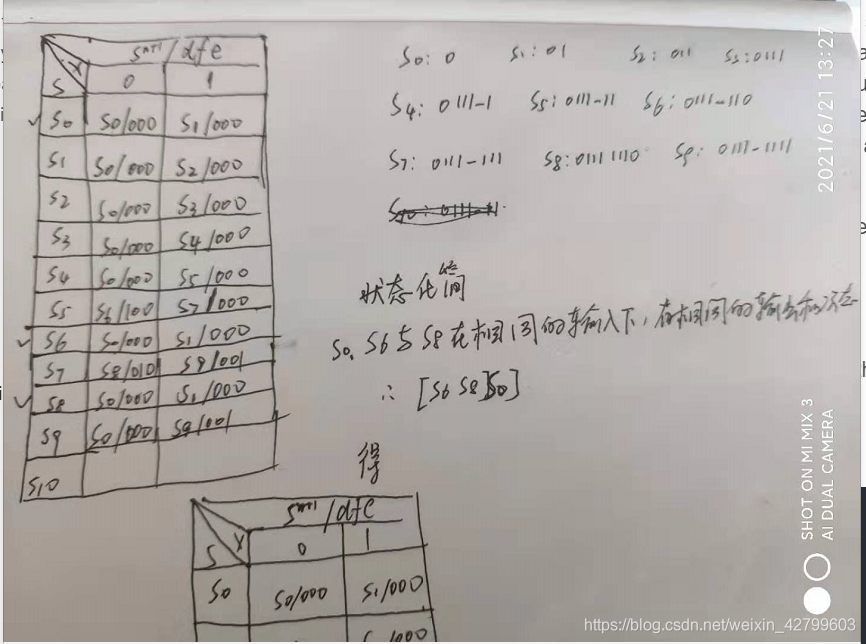

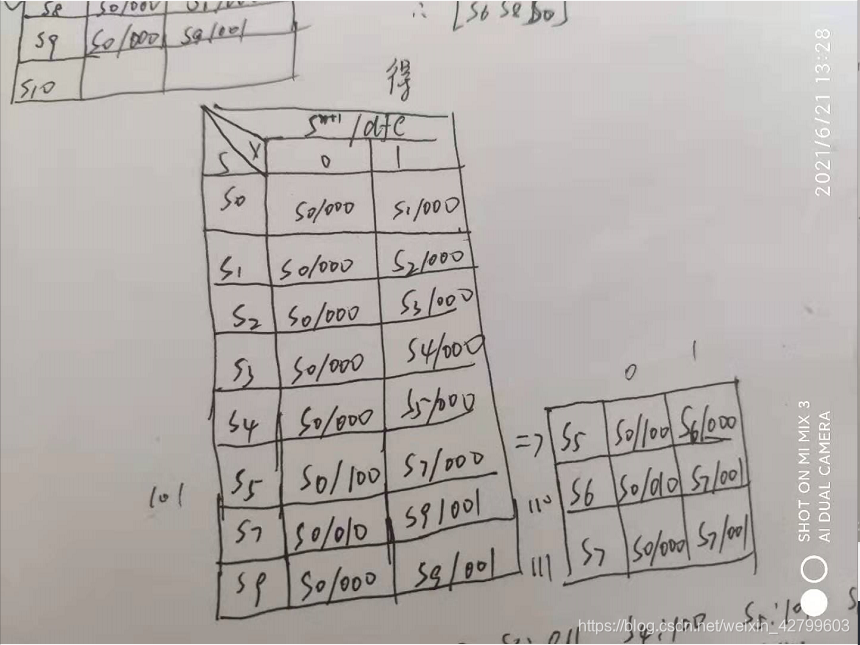

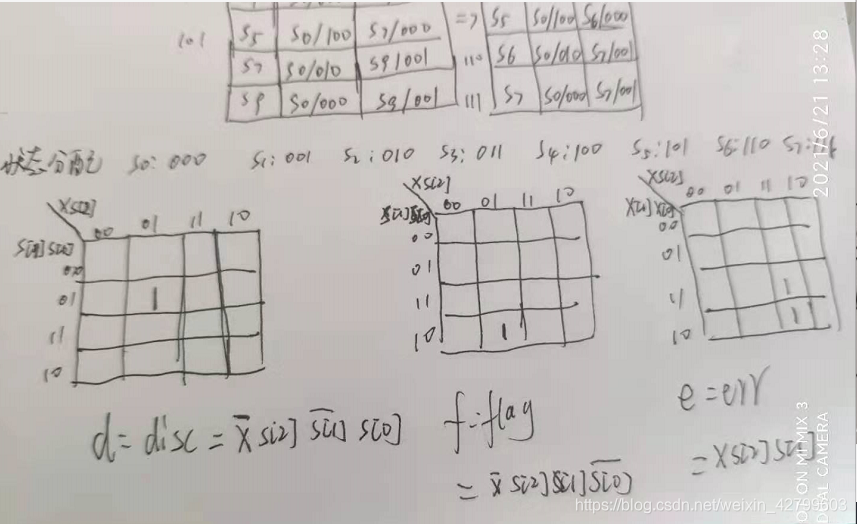

Mealy型

module top_module(

input clk,

input reset, // Synchronous reset

input in,

output reg disc,

output reg flag,

output reg err);

parameter s0 = 0, s1 = 1, s2 = 2, s3 = 3, s4 = 4, s5 = 5, s6 = 6,s7 = 7;

reg [2:0] state,next_state;

always@

本文详细介绍了如何使用Mealy和Moore型状态机来识别同步HDLC帧中的三种关键序列:连续6个1的标志、错误检测和帧边界。通过Verilog实现的模块展示了两种状态机模型的区别,并解释了它们在数据处理中的作用。

本文详细介绍了如何使用Mealy和Moore型状态机来识别同步HDLC帧中的三种关键序列:连续6个1的标志、错误检测和帧边界。通过Verilog实现的模块展示了两种状态机模型的区别,并解释了它们在数据处理中的作用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?