DMA(direct memory access),直接存储器访问是用来数据搬运的技术,在没有DMA的情况下,数据的访问要通过CPU一条一条执行指令来实现,这种访问方式不仅速度慢,而且占用cpu算力。对于高速外设,数据传输的速度必须要快,否则可能出现丢包错误,基于这种情况,出现了DMA技术,DMA是一个搬运工,采用DMA的传送方式不需CPU干预,外设和存储器之间的数据访问可以在DMA控制器(DMAC)的控制下直接进行,少去了逐条指令执行的麻烦,释放了内核并使传输效率大大提高。DMA主机有控制AHB总线的权利,当DMA执行数据传输时,CPU会把总线的控制权交给DMA控制器。

CPU会启动一个数据传输,之后就会让出总线控制权,让DMA这个总线主设备来执行数据传输,在执行传输之前需要对DMA的相关寄存器进行配置,包括:

1.控制命令寄存器 配置传输数据的发起方式、数据的大小及通道和地址的控制命令。

2.初始地址寄存器 DMAC根据该寄存器的值,可进行正确的寻址进行数据的传送。

单通道DMAC有如下特点:

- 支持双向传输;

- 源地址和目的地址,采用递增的地址产生方式;

- DMA burst尺寸可通过编程改变,传输效率会更高;

- 支持8Bit,16bit和32bit宽度传输;

- 32bit AHB master总线宽度;

- DMA完成传输完成中断请求

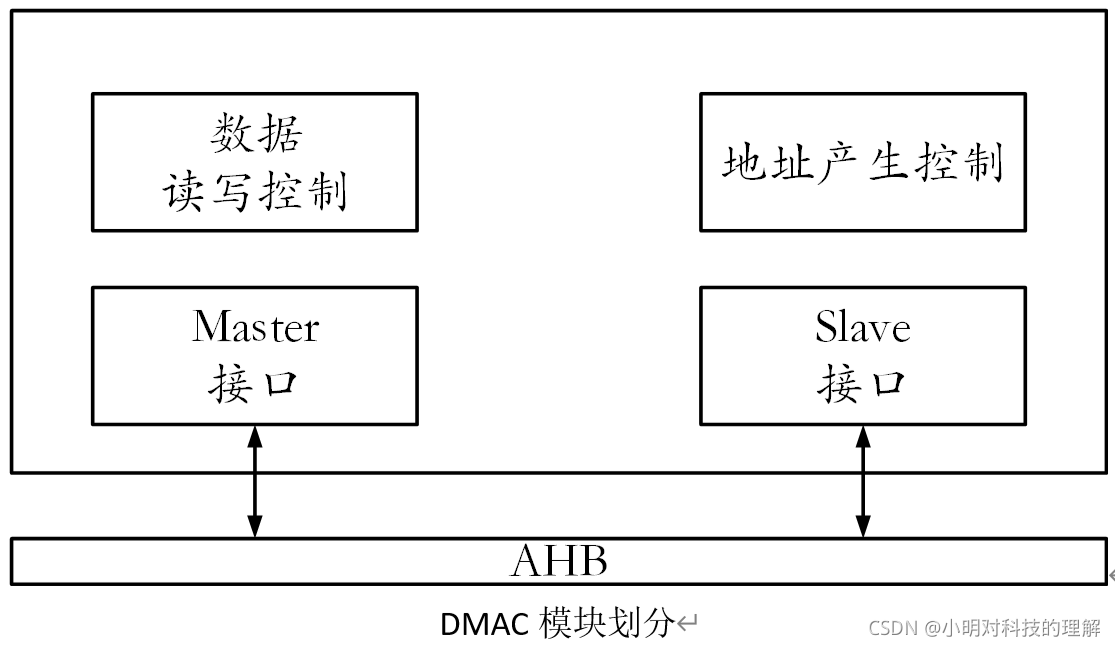

DMA控制器分为master接口模块、slave接口模块、地址产生控制模块和数据传送控制模块:

DMA支持四中传输方式,分别是存储器到存储器、存储器到外设、外设到存储器和外设到外设。

数据传送请求有两种方式:

- 存储器进行数据传送时不需要发起请求,可直接进行传送;

- 外设需要进行数据传送时,需等待外设发起的请求信号;

DMA数据传送流程:

- CPU将各参数的地址信息配置到通道寄存器,然后传送到DMAC的不同模块;

- 译码器解码,判断设备是存储器还是外设,将判断信号发给总线请求模块,总线根据译码器和硬件握手信号做出判断,最终发起数据传输请求;

- 请求信号通过master 接口给出,由cpu 来判断是否给予DMAC 总线使用权,当条件满足,DMAC 获得了总线使用权后,开始进行数据传送;

数据传送过程:

- 源和终端两个地址状态机依据寄存器中给出的传送起始地址及自身状态机的跳转,将地址信号给到地址产生控制模块;

- 地址产生控制模块判断来自两个状态机的地址信号,根据FIFO给出的控制信号进行判断,将其中一个地址作为当下有效地址;

- 将有效地址通过master接口给到AHB总线,之后总线可通过该地址进行寻址;

- 根据来自DMAC 内部的判断信号,总线寻址之后进行数据读写,将总线数据搬到此地址下,或者是将此地址下的数据转移到总上;

- FIFO将来自主机接口的数据存在FIFO的缓存中,当FIFO 满时,读写使能模块将改变使能信号,根据使能信号的跳转,数据控制模块将FIFO缓存中的数据通过master 接口给到总线,通过总线把数据存到终端设备中。

- 数据传送完毕,DMAC 会给出一个中断信号,这个中断信号将通过master 接口以及总线告知CPU ,此时CPU 将会给出一个中断清除信号,同时将会收回DMAC 的总线使用权,或者是重新对DMAC 进行下一次配置。

其中FIFO 顶层模块中包含数据控制模块和读写使能判断模块,数据控制模块中的状态机进行数据的存取。

DMA(直接存储器访问)技术用于高速数据传输,避免CPU参与逐条指令执行,提高效率。DMA控制器控制数据在存储器和外设间直接传输,支持多种宽度传输并具备中断请求功能。其工作流程包括CPU配置参数、DMA请求总线使用权、地址产生与数据读写,并在传输完成后发出中断信号通知CPU。

DMA(直接存储器访问)技术用于高速数据传输,避免CPU参与逐条指令执行,提高效率。DMA控制器控制数据在存储器和外设间直接传输,支持多种宽度传输并具备中断请求功能。其工作流程包括CPU配置参数、DMA请求总线使用权、地址产生与数据读写,并在传输完成后发出中断信号通知CPU。

1873

1873

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?