Cortex-M3 的存储系统架构与传统的 ARM 处理器有很大的区别。 Cortex-M3 处理器采用哈佛( Harvard)结构,拥有独立的指令总线( I-Code)与数据总线( D-Code)。具有以下新特性:

1. 存储器映射是预定义的,它规定了存储器访问所使用的总线。访问不同的存储设备时,处理器可对访问速度进行优化。

2. Cortex-M3 的存储系统支持位带操作,可对存储器和外设的位数据进行原子操作(位带操作仅限于存储器的部分特殊区域)。

3. Cortex-M3 的存储器系统支持非对齐的数据传输和互斥访问,并同时支持小端格式与大端格式两种配置。这些新特性都是 ARMv7-M 架构微处理器所特有的。

存储器映射

Cortex-M3 处理器采用单一固定的存储器映射, NVIC 和 MPU 都在相同的位置布设寄存器,使得它们与具体器件无关,从而方便软件代码在各种不同型号的 Cortex-M3 微处理器间移植。

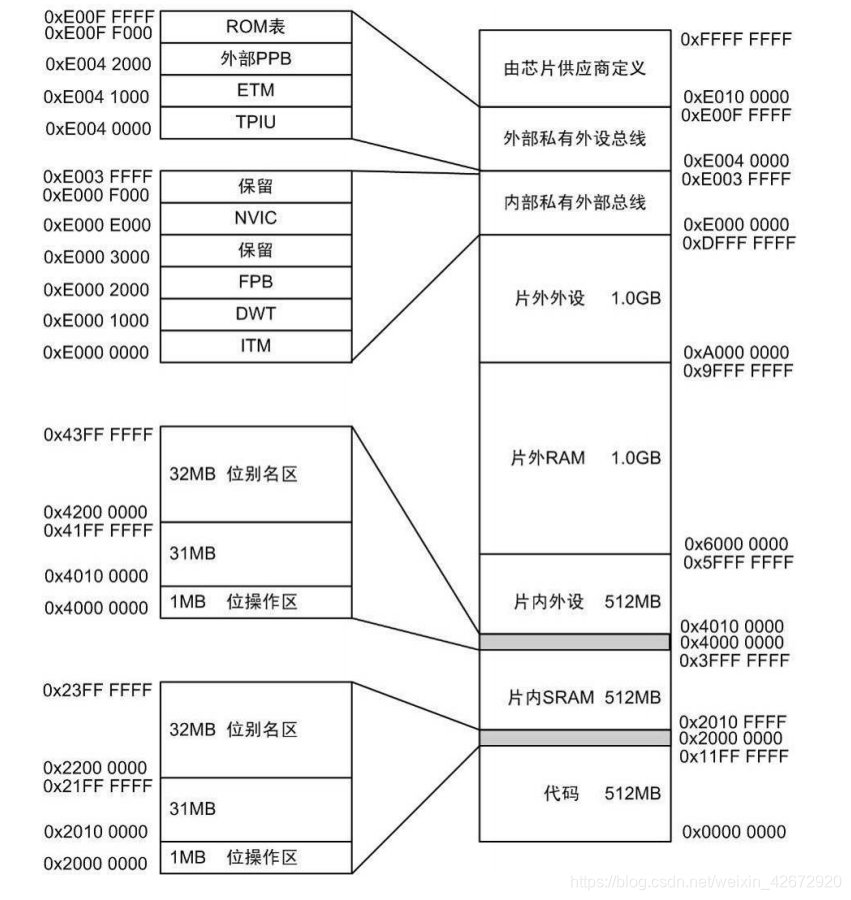

Cortex-M3 支持 4GB 的地址空间,程序可以在代码区、内部 SRAM 和外部 RAM 中运行。由于指令总线与数据总线是分开的,最理想的是将程序放到代码区,取指和数据访问使用各自的总线,并行不悖的执行。 Cortex-M3 存储器映射如图下图所示。

存储器映射寻址与处理器接口见下表

| 存储器映射 | 接口 |

|---|---|

| 代码区 | 指令取指在 ICode 总线上执行,数据访问在 DCode 总线上执行 |

| SRAM 区 | 指令取指和数据访问都在系统总线上执行 |

| SRAM 位操作区 | 位别名区域,数据访问是别名,指令访问不是别名 |

| 外设区 | 指令取指和数据访问都在系统总线上执行 |

| 片外 RAM 区 | 指令取指和数据访问都在系统总线上执行 |

| 片外外设区 | 指令取指和数据访问都在系统总线上执行 |

| 私有外设总线 | AHB 私有外设总线:只用于 Cortex-M3 内部的 APB 设备,包括: NVIC、 FPB、DWT 和 ITM; APB 私有外设总线:既用于 Cortex-M3 内部的 APB 设备,也用于外部设备(指相对于内核而言。Cortex-M3 允许器件制造商再添加一些片上 APB 外设到 APB 私有总线上,它们通过 APB 接口来访问 |

| 芯片厂商定义区 | 厂商系统外设的系统部分 |

4999

4999

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?