输入输出系统 ——I/O系统

I/O系统的组成

包括:

需要用于输入、输出和存储信息的设备;

需要相应的设备控制器;

控制器与CPU连接的高速总线;

有的大中型计算机系统,配置I/O通道;

1. I/O系统的基本功能及模型

1)主要功能:

隐藏物理设备细节,方便用户

用户使用抽象的I/O命令即可

实现设备无关性,方便用户

用户可用抽象的逻辑设备名来使用设备,同时也提高了OS的可移植性和易适应性。

提高处理机和设备的并行性,提高利用率:缓冲区管理

对I/O设备进行控制:控制方式、设备分配、设备处理

确保对设备正确共享:虚拟设备及设备独立性等

错误处理

2)I/O/系统的层次结构和模型

层次结构:系统中的设备管理模块分为若干个层次

层间操作:下层为上层提供服务,完成输入输出功能中的某些子功能,并屏蔽功能实现的细节。

①用户层软件

实现与用户交互的接口,用户可直接调用在用户层提供的、与I/O操作有关的库函数,对设备进行操作。

②设备独立软件

用于实现用户程序与设备驱动器的统一接口、设备命名、设备的保护以及设备的分配与释放等,同时为设备管理和数据传送提供必要的存储空间。

③设备驱动程序

与硬件直接相关,用于具体实现系统对设备发出的操作指令,驱动I/O设备工作的驱动程序。

④中断处理程序

用于保存被中断进程的CPU环境,转入相应的中断处理程序进行处理,处理完后再恢复被中断进程的现场后,返回到被中断进程。

块设备

数据的存取和传输都是以数据块为单位的设备。基本特征是传输速率较高、可寻址。磁盘设备的I/O常采用DMA方式。

特点

隐藏了磁盘的二维结构:块设备接口隐藏了磁盘地址是二维结构的情况:每个扇区的地址需要用磁道号和扇区号来表示。

将抽象命令映射为低层操作:块设备接口将上层发来的抽象命令,映射为设备能识别的较低层具体操作。

字符设备:

数据的存取和传输是以字符为单位的设备。如键盘、打印机等。基本特征是传输速率较低、不可寻址,常采用中断驱动方式。

get和put操作:

由于字符设备是不可寻址的,因而对它只能采取顺序存取方式。(用户程序)获取或输出字符的方法是采用get和put操作。

in-control指令:

因字符设备的类型非常多,且差异甚大,系统以统一的方式提供了一种通用的in-control指令来处理它们(包含了许多参数,每个参数表示一个与具体设备相关的特定功能)。

通过某种方式,把计算机连接到网络上。

操作系统必须提供相应的网络软件和网络通信接口,使得计算机能通过网络与网络上的其它计算机进行通信,或上网浏览。

1)程序I/O方式

cpu对I/O设备的控制采取程序I/O方式,或称忙—等待方式

向控制器发送一条I/O指令;启动输入设备输入数据;把状态寄存器busy=1。

然后不断测试标志。为1:表示输入机尚未输完一个字,CPU继续对该标志测试;直到为0:数据已输入控制器数据寄存器中。

CPU取控制器中的数据送入内存单元,完成一个字的I/O 。

高速CPU空闲等待低速I/O设备,致使CPU极大浪费。

2)中断驱动I/O方式

CPU向相应的设备控制器发出一条I/O命令

然后立即返回继续执行任务。

设备控制器按照命令的要求去控制指定I/O设备。

这时CPU与I/O设备并行操作。

I/O设备输入数据中,无需CPU干预,因而可使CPU与I/O设备并行工作。从而提高了整个系统的资源利用率及吞吐量。

3)直接存储器访问DMA 方式

①该方式的特点是:

数据传输的基本单位是数据块;

所传送的数据是从设备直接送入内存的,或者直接从内存进设备;不需要CPU操作。

CPU干预进一步减少:仅在传送一个或多个数据块的开始和结束时,才需CPU干预,整块数据的传送是在控制器的控制下完成的。

可见DMA方式又是成百倍的减少了CPU对I/O的干预,进一步提高了CPU与I/O设备的并行操作程度。

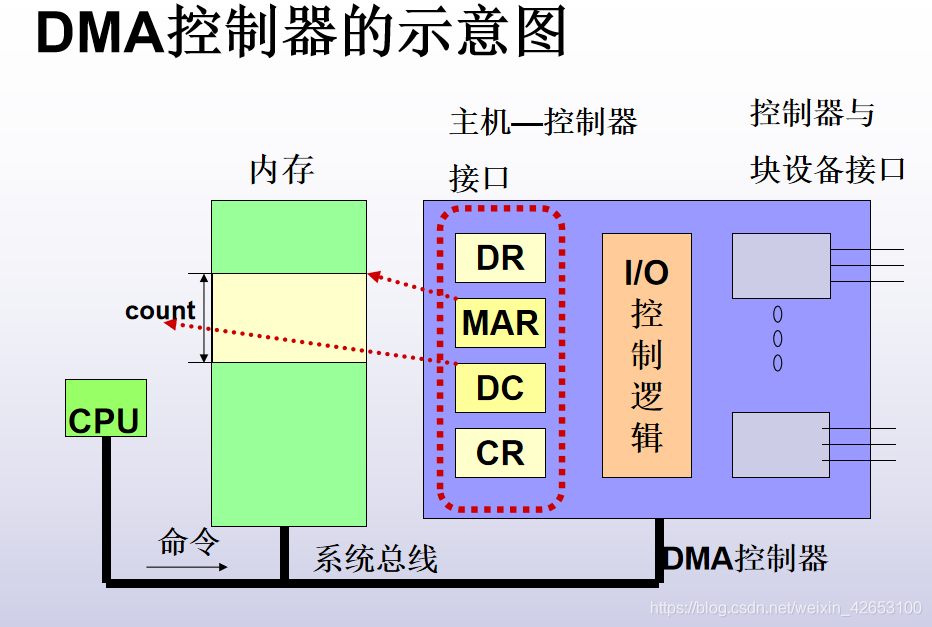

②DMA控制器的组成

DMA控制器由三部分组成:

主机与DMA控制器的接口;

DMA控制器与块设备的接口;

I/O控制逻辑。

如下页图。

③DMA工作过程

CPU先向磁盘控制器发送一条读命令。

该命令被送到命令寄存器CR中。

同时发送数据读入到内存的起始地址,该地址被送入MAR中;

要读数据的字数则送入数据计数器DC中;

将磁盘中的数据原地址直接送入DMA控制器的I/O控制逻辑上,按设备状态启动磁头到相应位置。

启动DMA控制器控制逻辑开始进行数据传送

DMA控制器读入一个数据到数据寄存器DR中,然后传到内存MAR地址中;

接着MAR+1,DC-1,判断DC是否为0,如否,继续,反之控制器发中断请求,传送完毕。

4)I/O通道控制方式

DMA适用于读一个连续的数据块;

如一次读多个数据块到内存不同区域,须由CPU分别发送多条I/O指令、进行多次DMA中断处理。

再进一步减少CPU的干预(减少中断), 引入通道。

实现对一组数据块的读(写)及有关的控制和管理为单位的干预。

此时,CPU只需发一条I/O指令,给出通道程序的首地址及要访问设备即可。

- CPU、通道和I/O设备三者的并行操作,提高整系统资源利用率。

缓冲管理

I/O控制方式减少CPU对I/O的干预提高利用率;

缓冲则通过缓和CPU和I/O设备速度不匹配矛盾,增加CPU和I/O设备的并行性,提高利用率。

现代OS中,几乎所有的I/O设备与处理机交换数据时,都用了缓冲区。

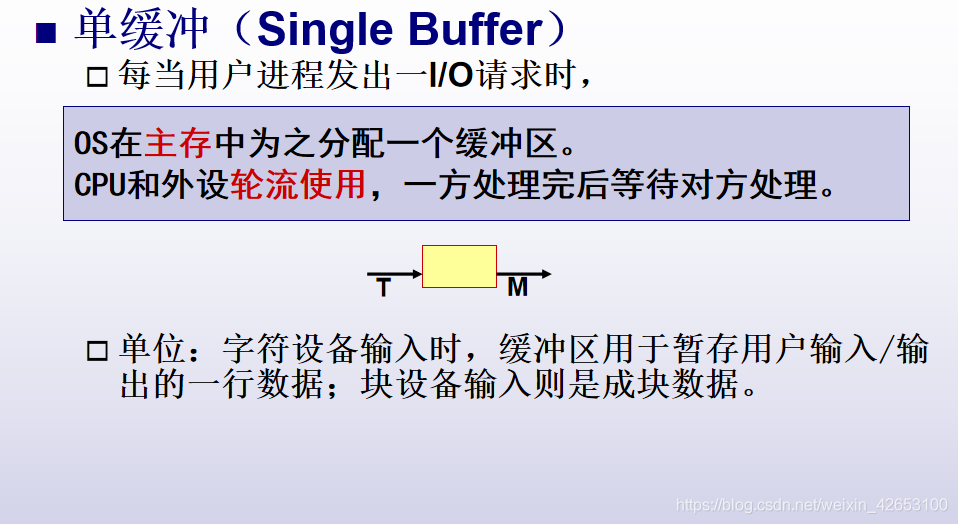

1)单缓冲与多缓冲

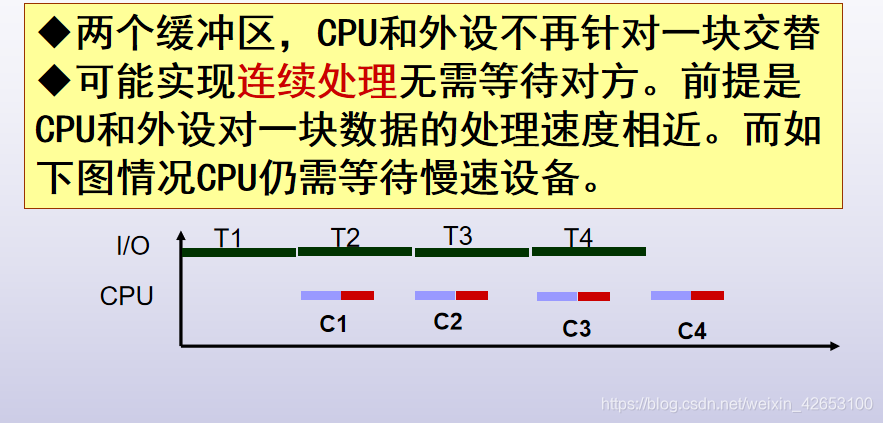

双缓冲(Double Buffer)

进一步加快输入和输出速度,提高设备利用率制,也称缓冲对换(Buffer Swapping)

输入:数据送入第一缓冲区,装满后转向第二缓冲区。

读出:OS从第一缓冲区中移出数据,送入用户进程,再由CPU对数据进行计算。

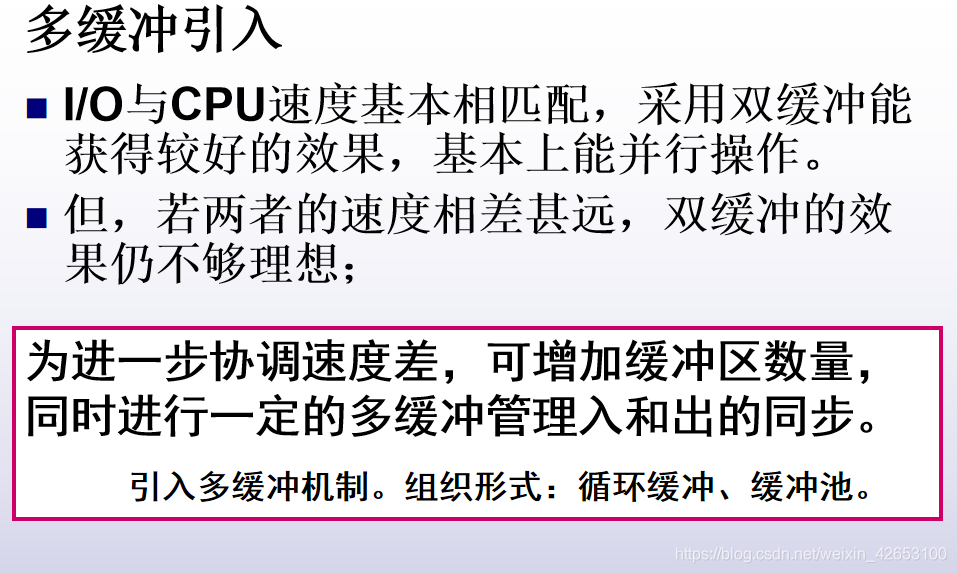

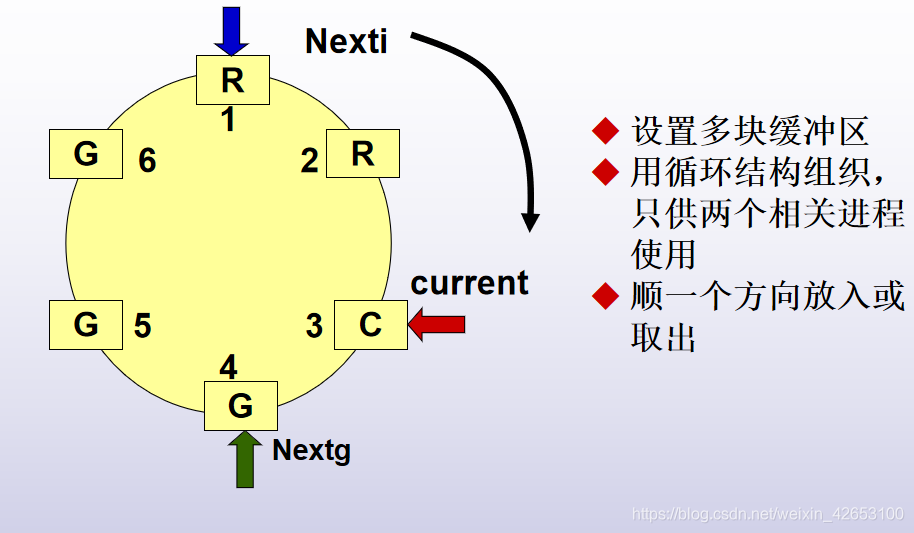

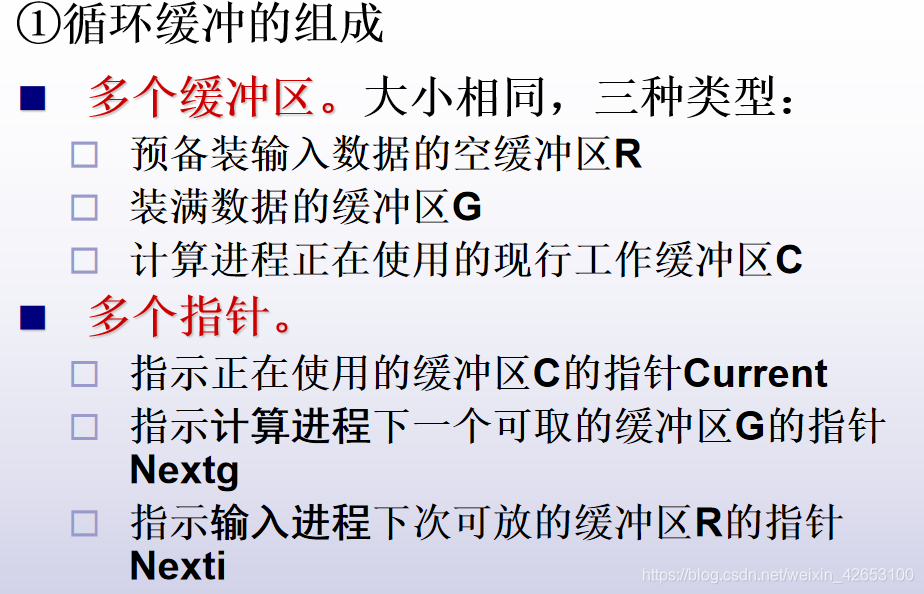

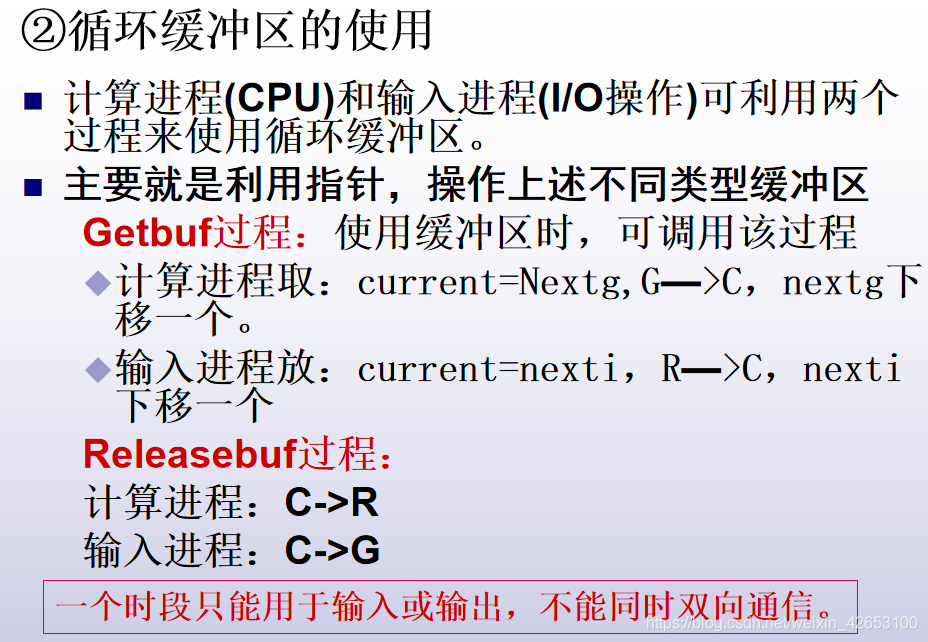

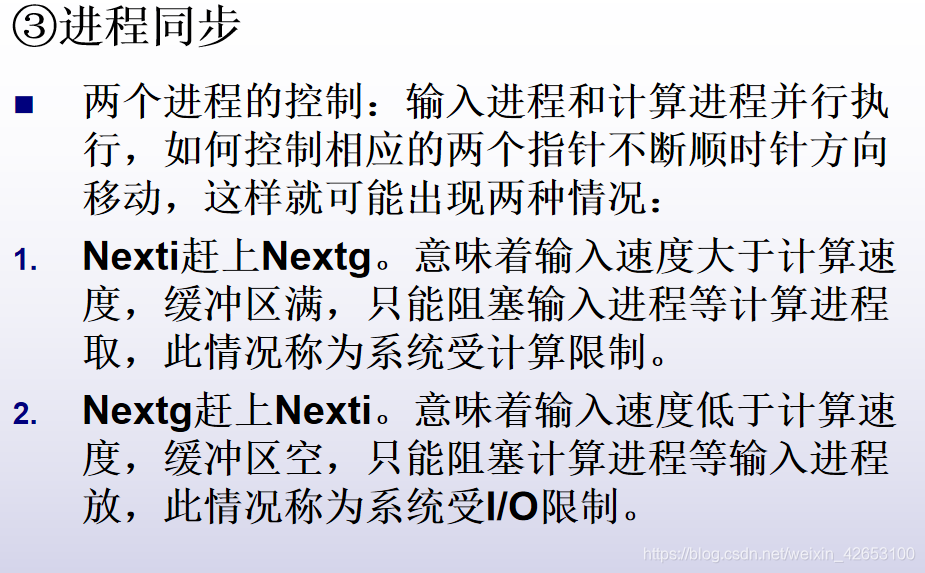

2)循环缓冲(circular buffer)

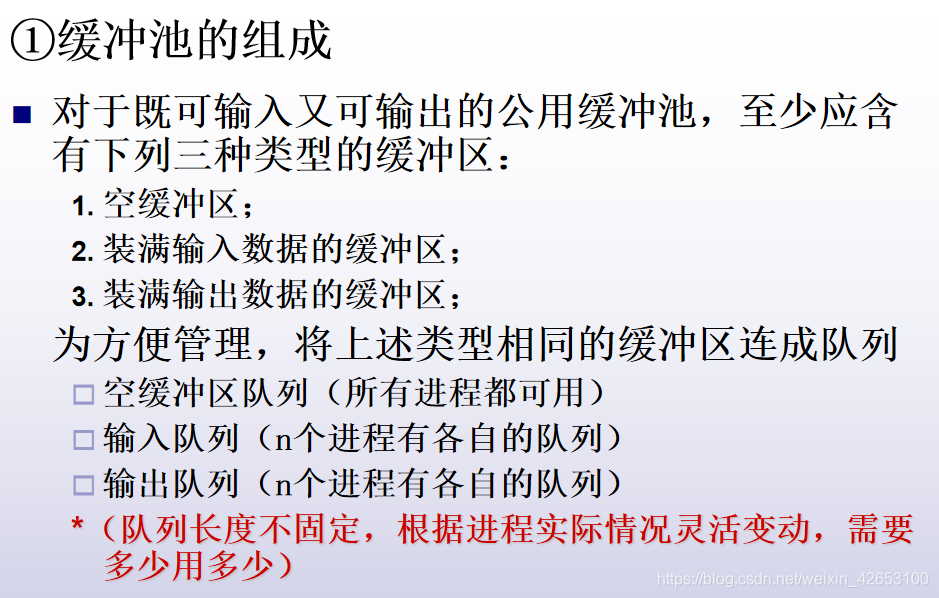

3)缓冲池(Buffer Pool)

循环缓冲的问题

不能同时双向通讯

利用率不高。缓冲区是专用缓冲。(每个进程都要维护自己的一个循环缓冲区),使用有剩余时也不给其他进程使用,消耗大量内存空间。

系统并发程序很多时,许多这样的循环缓冲需要管理,比较复杂。

为提高缓冲区的利用率,目前广泛流行缓冲池,在池中设置多个可供若干个进程共享的缓冲区。

缓冲区的使用

*Getbuf(队列,工作区)

*Putbuf(队列,工作区)

*同步控制

1.每队设置一个互斥信号量MS;

2.判断每个队列是否有可用的缓冲区,需一个资源信号量RS。获取缓冲区时P(RS),释放时V(RS)。

本文详细介绍了操作系统中的输入输出系统,包括I/O系统的组成、基本功能及模型,如设备控制器、高速总线、I/O通道等。此外,还讲解了I/O系统的层次结构,如用户层软件、设备独立软件、设备驱动程序和中断处理程序。重点讨论了块设备和字符设备的特点,以及程序I/O、中断驱动I/O、直接存储器访问(DMA)和I/O通道这四种不同的I/O控制方式。最后,文章探讨了缓冲管理在解决CPU与I/O设备速度不匹配问题中的作用,如单缓冲、双缓冲、循环缓冲和缓冲池的应用。

本文详细介绍了操作系统中的输入输出系统,包括I/O系统的组成、基本功能及模型,如设备控制器、高速总线、I/O通道等。此外,还讲解了I/O系统的层次结构,如用户层软件、设备独立软件、设备驱动程序和中断处理程序。重点讨论了块设备和字符设备的特点,以及程序I/O、中断驱动I/O、直接存储器访问(DMA)和I/O通道这四种不同的I/O控制方式。最后,文章探讨了缓冲管理在解决CPU与I/O设备速度不匹配问题中的作用,如单缓冲、双缓冲、循环缓冲和缓冲池的应用。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?