False path:在设计中,不需要满足setup/hold时序的数据路径需要设置成false path。

设置成false_path的数据路径,EDA工具仍然会计算累加这条路径上的timing arc延时,但是不优化和报告这条数据路径上的setup/hold时序违例,会继续优化和报告这条数据路径上的逻辑DRC

max_transition

max_capacitance

max_fanout

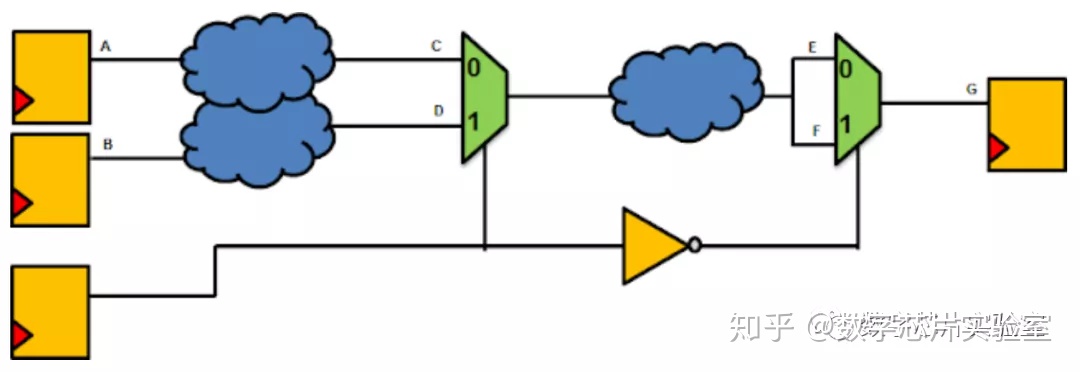

对于上述设计

A -> C -> E -> G 和 B -> D -> F -> G需要设置成False path。

在芯片设计中利用两级触发器防止信号的亚稳态传播,此时两级触发器的第一级是不做时序检查的,因此在设计约束中也需要将其设置为False path来避免对第一级触发器进行时序分析。

Disable timing:set_disable_timing 用来disable 设计中某个timing arc 。

设置disable_

本文介绍了在芯片设计中如何处理False path和使用set_disable_timing命令。False path用于标记不需要满足时序要求的路径,工具会计算但不优化其时序违例。而set_disable_timing则用于禁用特定timing arc,阻止工具对其进行计算和分析,尤其适用于异步电路中的timing loop处理。两者在处理时序路径和timing arc上有显著区别。

本文介绍了在芯片设计中如何处理False path和使用set_disable_timing命令。False path用于标记不需要满足时序要求的路径,工具会计算但不优化其时序违例。而set_disable_timing则用于禁用特定timing arc,阻止工具对其进行计算和分析,尤其适用于异步电路中的timing loop处理。两者在处理时序路径和timing arc上有显著区别。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?