惨痛教训

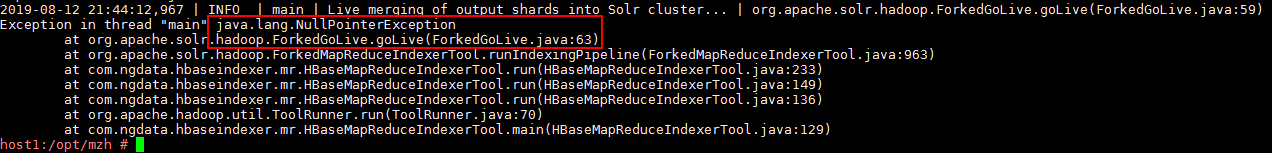

刚刚经历了一个java.lang.NullPointerException的惨痛教训,引以为戒!

源码定位

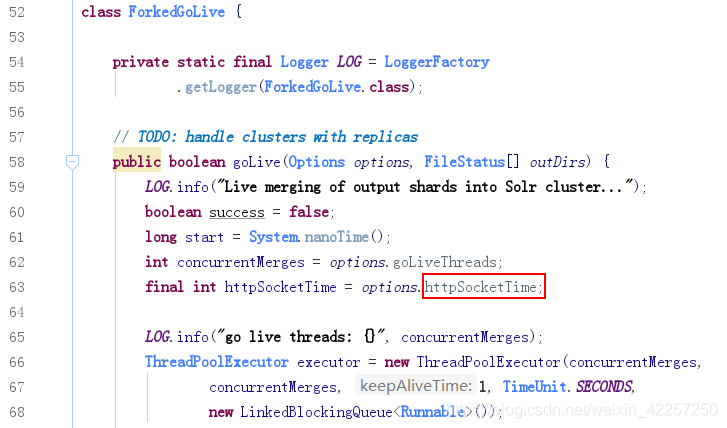

Integer httpSocketTime = null;(某种原因,导致是null)

int httpSocketTime = httpSocketTime;(用到该参数时,由于未判空导致空指针异常)

未被初始化的Integer类引发的空指针:Integer类是包装类,如果不初始化,将被定义为null,从而引发了空指针。

- 提问:此处定义httpSocketTime为原始类型int行不行?

- 答案:也不行,int参数如果不初始化,将被赋值为0,用作超时参数也是不可行的。

总结提升

- 请重视任何直接对接客户的接口和参数,因为他们将可能改变用户的行为,改变用户的代码(难于登天)。

- 请详细考虑修改可能引入的不同业务场景,必须保证向下兼容性,保证原来的使用方式不受影响。

a. 原来不加参数的场景

b. 加了超时参数,参数值小的场景

c. 加了超时参数,参数值大的场景- 雪中送炭最为珍贵,锦上添花也可以点赞,画蛇添足的引以为戒,下次就请出门右转不送。

本文分享了一次因Integer变量未初始化导致的Java空指针异常(NPE)经历,深入探讨了自动装箱拆箱机制,并强调了参数处理的重要性,尤其是在客户接口中。

本文分享了一次因Integer变量未初始化导致的Java空指针异常(NPE)经历,深入探讨了自动装箱拆箱机制,并强调了参数处理的重要性,尤其是在客户接口中。

445

445

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?