1、源码及注释

ENTRY(lowlevel_init)

/*

* Setup a temporary stack. Global data is not available yet.

*/

ldr sp, =CONFIG_SYS_INIT_SP_ADDR

bic sp, sp, #7 /* 8-byte alignment for ABI compliance */

#ifdef CONFIG_DM

mov r9, #0

#else

/*

* Set up global data for boards that still need it. This will be

* removed soon.

*/

#ifdef CONFIG_SPL_BUILD

ldr r9, =gdata

#else

sub sp, sp, #GD_SIZE

bic sp, sp, #7

mov r9, sp

#endif

#endif

/*

* Save the old lr(passed in ip) and the current lr to stack

*/

push {ip, lr}

/*

* Call the very early init function. This should do only the

* absolute bare minimum to get started. It should not:

*

* - set up DRAM

* - use global_data

* - clear BSS

* - try to start a console

*

* For boards with SPL this should be empty since SPL can do all of

* this init in the SPL board_init_f() function which is called

* immediately after this.

*/

bl s_init

pop {ip, pc}

ENDPROC(lowlevel_init)

2、相关指令介绍

- ldr

ARM指令集中,LDR通常都是作加载指令的,但是它也可以作伪指令。

(1)LDR r0,=name,像这种带等号的是伪指令,而不是ARM指令,LDR 伪指令用于加载立即数或一个地址值到指定寄存器。

如果name是立即数的话:LDR R0,=0X123;//将0X123存入R0

如果name是个标识符:LDR R0,=NAME;//将NAME的地址存入R0

相当于:

LDR R0,LABEL;

LABEL DCB NAME;//分配内存并用NAME初始化(LABEL为内存的起始地址?)

(2)LDR R1,[R0] ;如果没有等号,LDR 指令用于从内存中读取数据放入寄存器中.该指令是 将R0 地址处的数据读出,保存到R1 中(零偏移)。

3、代码解读

ldr sp, =CONFIG_SYS_INIT_SP_ADDR // 为global data设置堆栈

./include/configs/mx6sabre_common.h

#define CONFIG_SYS_SDRAM_BASE PHYS_SDRAM

#define CONFIG_SYS_INIT_RAM_ADDR IRAM_BASE_ADDR

#define CONFIG_SYS_INIT_RAM_SIZE IRAM_SIZE

#define CONFIG_SYS_INIT_SP_OFFSET \

(CONFIG_SYS_INIT_RAM_SIZE - GENERATED_GBL_DATA_SIZE)

#define CONFIG_SYS_INIT_SP_ADDR \

(CONFIG_SYS_INIT_RAM_ADDR + CONFIG_SYS_INIT_SP_OFFSET)

./arch/arm/include/asm/arch-mx6/imx-regs.h

#define IRAM_BASE_ADDR 0x00900000

#define IRAM_SIZE 0x00040000 //256k

./lib/asm-offsets.c

/* Round up to make sure size gives nice stack alignment */

DEFINE(GENERATED_GBL_DATA_SIZE,

(sizeof(struct global_data) + 15) & ~15); //256 sizeof(struct global_data) = 248 = GD_SIZE

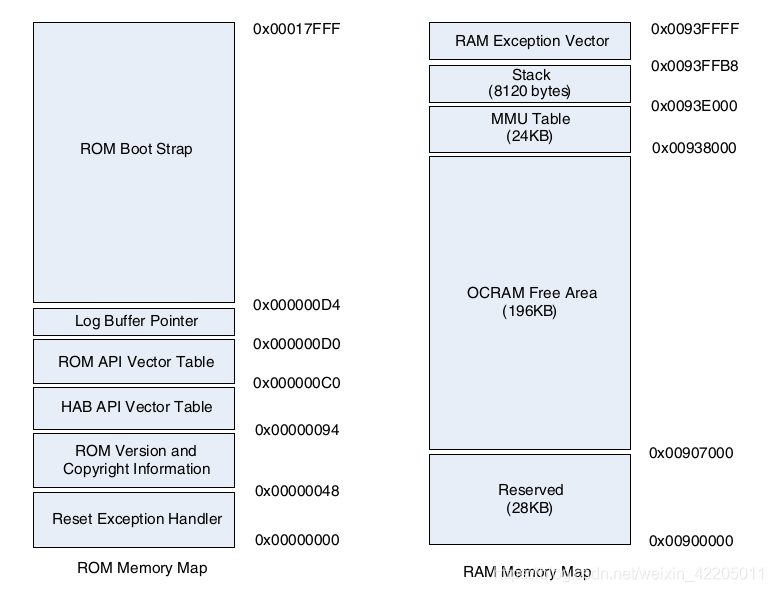

根据以上定义,CONFIG_SYS_INIT_SP_ADDR = 0x00900000 + 0x00040000 - 256 = 0x0093FF00。下图为IMX6DL内存模型。

/*

* Call the very early init function. This should do only the

* absolute bare minimum to get started. It should not:

*

* - set up DRAM

* - use global_data

* - clear BSS

* - try to start a console

*

* For boards with SPL this should be empty since SPL can do all of

* this init in the SPL board_init_f() function which is called

* immediately after this.

*/

bl s_init

pop {ip, pc}

//暂时看不懂,应该是初始化时钟,先放着

./arch/arm/mach-imx/mx6/soc.c

void s_init(void)

{

struct anatop_regs *anatop = (struct anatop_regs *)ANATOP_BASE_ADDR;

struct mxc_ccm_reg *ccm = (struct mxc_ccm_reg *)CCM_BASE_ADDR;

u32 mask480;

u32 mask528;

u32 reg, periph1, periph2;

if (is_cpu_type(MXC_CPU_MX6SX) || is_cpu_type(MXC_CPU_MX6UL))

return;

/* Due to hardware limitation, on MX6Q we need to gate/ungate all PFDs

* to make sure PFD is working right, otherwise, PFDs may

* not output clock after reset, MX6DL and MX6SL have added 396M pfd

* workaround in ROM code, as bus clock need it

*/

mask480 = ANATOP_PFD_CLKGATE_MASK(0) |

ANATOP_PFD_CLKGATE_MASK(1) |

ANATOP_PFD_CLKGATE_MASK(2) |

ANATOP_PFD_CLKGATE_MASK(3);

mask528 = ANATOP_PFD_CLKGATE_MASK(1) |

ANATOP_PFD_CLKGATE_MASK(3);

reg = readl(&ccm->cbcmr);

periph2 = ((reg & MXC_CCM_CBCMR_PRE_PERIPH2_CLK_SEL_MASK)

>> MXC_CCM_CBCMR_PRE_PERIPH2_CLK_SEL_OFFSET);

periph1 = ((reg & MXC_CCM_CBCMR_PRE_PERIPH_CLK_SEL_MASK)

>> MXC_CCM_CBCMR_PRE_PERIPH_CLK_SEL_OFFSET);

/* Checking if PLL2 PFD0 or PLL2 PFD2 is using for periph clock */

if ((periph2 != 0x2) && (periph1 != 0x2))

mask528 |= ANATOP_PFD_CLKGATE_MASK(0);

if ((periph2 != 0x1) && (periph1 != 0x1) &&

(periph2 != 0x3) && (periph1 != 0x3))

mask528 |= ANATOP_PFD_CLKGATE_MASK(2);

writel(mask480, &anatop->pfd_480_set);

writel(mask528, &anatop->pfd_528_set);

writel(mask480, &anatop->pfd_480_clr);

writel(mask528, &anatop->pfd_528_clr);

}

1369

1369

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?