一:亚稳态及其危害

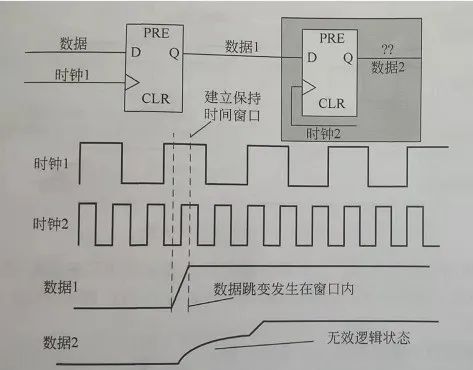

对于沿触发的触发器来说,其输出存在两个有效的状态,即高和低(或者说逻辑1和逻辑0)。触发器的建立时间和保持时间在时钟上升沿左右定义了一个时间窗口,如果触发器数据输入数据输入端口上的数据在这个时间窗口内发生变化,那么就会产生时序违规。存在这个时序违规是因为建立时间和保持要求不满足了.此时触发器内部的某个节点可能会在一个电压范围内浮动.无法稳定在逻辑0或者逻辑1状态。换句话说,如果数据在上述窗口中被采集,触发器中的晶体管不能可靠地设置为逻辑0或者逻辑1对应的电平上,所以,此时的晶体管并未处于饱和区对应的高或者低电平,而是徘徊在一个中间电平状态。图1所示就是所谓的亚稳态。

如图1的波形所示,信号的跳变发生在建立时间和保持时间边界组成的时间窗口内,或者说时钟2刚好在数据1发生变化的时刻对其进行采样,这意味着第二个寄存器的输出不会是逻辑0或逻辑1对应的确定电平,而是它们之间的一个中间电平。输出保持亚稳态的时间是随机的,甚至可能在整个时钟周期内都保持亚稳态。那么,如果这个亚稳态值输入到组合逻辑,就可能会发生错误的操作。从时序收敛的角度来说说,两个触发器之间的组合逻辑延时都要求要小于最小的时钟周期,但这种亚稳态信号保持亚稳态的时间,本来就是变相的增加了逻辑延时,显然,一个亚稳态信号会给设计带来致命的功能障碍,使得该信号在两个时钟域相邻时钟沿上无法获得相同的状态,但是在跨过时钟域之后的第二个时钟上升沿时刻,数据应当能够稳定下来。

事实上需要注意的是,在FPGA设计流程中想通过仿真来确定亚稳态对设计的危害是非常困难的。纯数字的仿真器并不能检查到建立和保持时间违规,从而在时序违规发生时,仿真出一个逻辑“X"(未知)值。而普通的RTL仿真,并不会出现建立和保持时间违规,所以也就不会有信号出现亚稳态状态。尽管门级仿真的时候会检查建立和保持时间是否违规,但是仿真由两个异步信号对齐而导致一个同步故障依然是一件十分困难的事情。尤其困难的是,设计或者验证工程师并不是在设计伊始即查找问题。那么,理解如何保持设计的可靠性以及如何避免需要通过仿真来揭露设计的同步问题,就显得十分重要了。解决亚稳态的方法有很多,后面将逐一进行讨论。

图1亚稳态电路

二:处理亚稳态的经典办法---双触发

设计中使用的任何寄存器都会指定一个建立和保持时间,在时钟上升沿前后的这个时间内输人数据被禁止发生任何变动。所有器件中的寄存器都要指定这个精确參数,就是为了防止数据信号两次变化发生的时间间隔太过靠近,从而导致其输出陷入亚稳态。

当需要在两个时钟域传输信号的时候,需要考虑一个重要的问题是:是否需要采样从一个时钟域传输到另一个时钟域的这个信号的每个值,在跨时钟边界存在跨时钟域传输数据允许丢失部分采样值和跨时钟域传输数据不允许丢失任何信号采样值两种情况,而且确认设计到底属于哪种情况则变得非常重要。

对于第一种情况来说,没有必要去采样每一个值,但是需要注意的是被采样的值必需要确保精确度;而在第二种情况中,一个跨时钟域信号必需要被正确识别,或者说在其允许发生改变之前必须被识别。这两种情况中,跨时钟域信号都需要被同步到其接收时钟域之中。

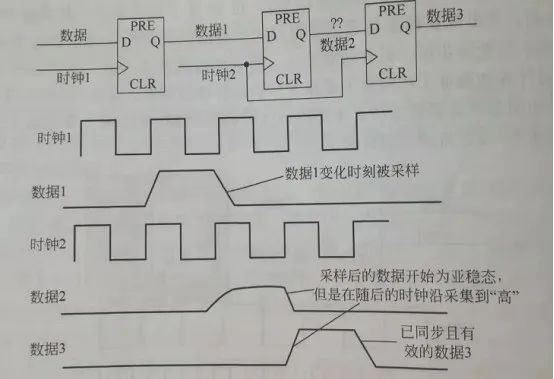

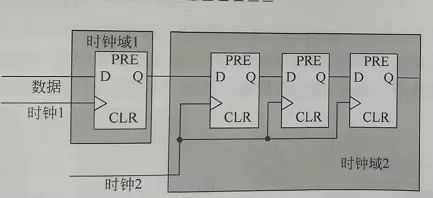

最常见的同步器就是使用两级寄存器,即使用寄存器打两拍的方式进行同步。所谓的同步器就是采样一个异步信号,采样输出能够同步到本地或采样时钟的模块。这种最简单也是使用最普遍的两级寄存的同步器如图2所示。

图2 双寄存器采样

当然,仍然有可能级联的第二个寄存器输出还会表现为非稳定状态.但是这种双寄存同步器已经可以解决大部分这类亚稳态问题。在设计这种同步器的时候应当注意遵循以下原则:

-

级联的寄存器必须使用同一个采样时钟。

-

发送端时钟域寄存器输出和接收端异步时钟域级联寄存器输人之间不能有任何其他组合逻辑.

-

同步器中级联的寄存器中除了最后一个寄存器外所有的寄存器只能有一个扇出,即其只能驱动下一级寄存器的输入。

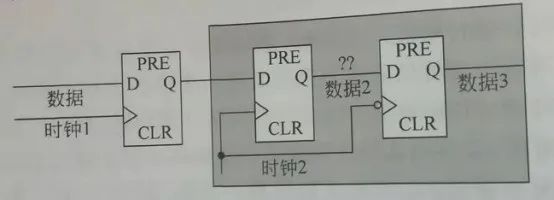

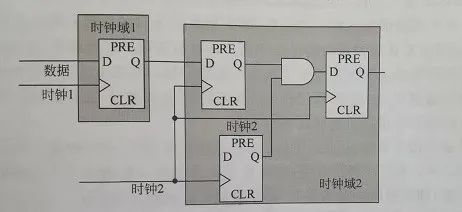

图3就展示了不符合上述第一个原则的情况.即接收时钟域两个级联寄存器使用了不同的时钟沿进行触发。这样处理大大增加了无法有效解决第一个寄存器亚稳态输出的风险,因为级联寄存器中的第一个寄存器很可能没有足够的时间来处理。

图3 不符合双寄存器采样调节

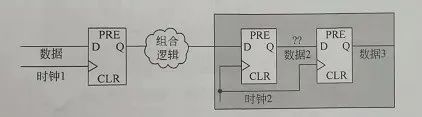

图4则展现了不符合上述第二个原则的情况,即发送时钟域寄存器输出和接收时钟域寄存器输入之间存在不合理的组合逻辑。由于组合逻辑会产生毛刺,这样同步器很有可能采样到不需要的数据,此外,组合逻辑输出的额外切换也增加了亚稳态的风险。

图4 跨时钟域边界存在不合理的组合逻辑

同步器中寄存器链的长度就是符合上述三个原则的寄存器个数,上述提到的典型的同步器长度是2,即两级寄存器。另外,只要同步器中寄存器链处于同一个时钟域,那么寄存器链中寄存器路径之间是可以存在组合逻辑的。图5所示即为这样的一个例子。

图5 同步级联寄存器之间有组合逻辑

三:使用三级触发器对亚稳态进行同步处理

首先来看一个概念,即平均故障间隔时间( Mean Time Between Failure,MTBF)。这是平均故障间隔时间(首先来看一个概念,即平均故障间隔时间)。这是衡量一个产品,尤其是电子产品的可靠性指标。对于大部分应用来说,计算所有跨时钟边界衡量一个产品,尤其是电子产品的可靠性指标.对于大部分应用来说,计算所有跨时钟边界信号的MTBF是非常重要的。对于前面讨论到的亚稳态同步器来说,这里的故障是指一个被传输到同步触发器的信号,当它经过第一级同步触发器时处于亚稳态,在随后的一个时钟周期内持续保持亚稳态并被采样到第二级同步器触发器。正是由于经过第一级同步寄存器后信号仍未稳定到一个已知状态值,故该信号的亚稳态状态继续被第二级寄存器采样并传递到接收时钟域,并会给相应逻辑导致潜在的故障。

显然,在计算MTBF时,大的MTBF值要好于小的MTBF值。MTBT值大表示两次故障间隔的时间长,相反,则表示两次故障间隔的时间短。

高速设计中使用的三级触发器同步器也是为了提供MTBF值。

图6 三级触发器同步器

5739

5739

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?