提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

前言

《Electromagnetic Compatibility Engineering》(中文版名字为《电磁兼容工程》)是一本非常好的EMC相关的教材,在这里记录和总结自己的学习过程。感谢 Henry W. Ott!

本文为该书Chapter2.1~2.2 布线中的电容耦合(电场耦合)。

一、电容耦合分析简易版本——两根裸露导体之间的耦合

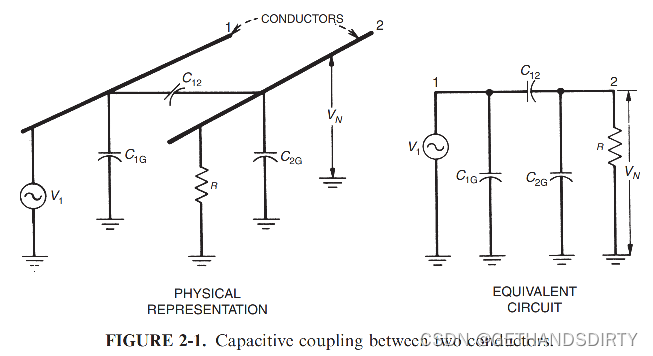

两根导线之间的电容耦合及其等效电路可以用以下模型表示:

其中:

- C12是导线1和导线2之间的寄生电容(stray capacitance);

- C1G是导线1和GND之间的电容;

- C2G是导线2和GND之间的电容,由导线2对GND的寄生电容和任何连接到导线2的电路的影响组成;

- R为导线2(也即一个电路)与GND之间的电阻,这里的电阻是由连接到导线2上的所有电路引起的,而非寄生电阻;

- V1是导线1上的电压,也就是导线2的干扰源;

- VN是导线2在导线1的电容耦合影响下,产生的噪声电压。

上图等效到右边的电路后,可以比较清楚地看出,噪声电压VN实际上就是C2G和R并联后的阻抗与C12阻抗对于V1的分压 (导线1和GND之间的电容C1G在这里对于导线2的电容耦合大小并没有影响),通过分压公式可得:

这么看公式比较复杂,不太能看出VN与各参数的依赖关系。因此做一些简化处理:

1.当R的阻抗比寄生电容C12+C2G的阻抗更低

即:

则上述公式将简化为:

这相当于上述模型的电容(电场)耦合可以近似于一个电流源,该电流源的电流为:

简化后,我们就可以比较容易地分析影响耦合电压的因素了:

- w为导线1(干扰源)的信号频率,频率越高则耦合电压越大,但这个是设计参数,我们轻易无法改变;

- V1为导线1(干扰源)上的电压,电压越高则耦合电压越大,这个同样是设计参数,我们轻易无法改变;

- R为导线2(也即噪声接收电路)与GND之间的电阻,这个也是与设计相关,我们轻易无法改变;

- C12为导线1和导线2之间的寄生电容(耦合电容),寄生电容越大则耦合电压越大,这个就是我们在设计时减小耦合电压的重点。

减小耦合电容一般有三种方法:

-

Orientation:通过合适的导线方向(即使得两根导体的电场线交叉重叠区域减少)可以减小耦合电容;

-

Shielding:即给接受电路加屏蔽线,屏蔽线到底可以起到怎样的作用见下述讨论。

-

Separating:顾名思义,即两个导线距离越远越好;

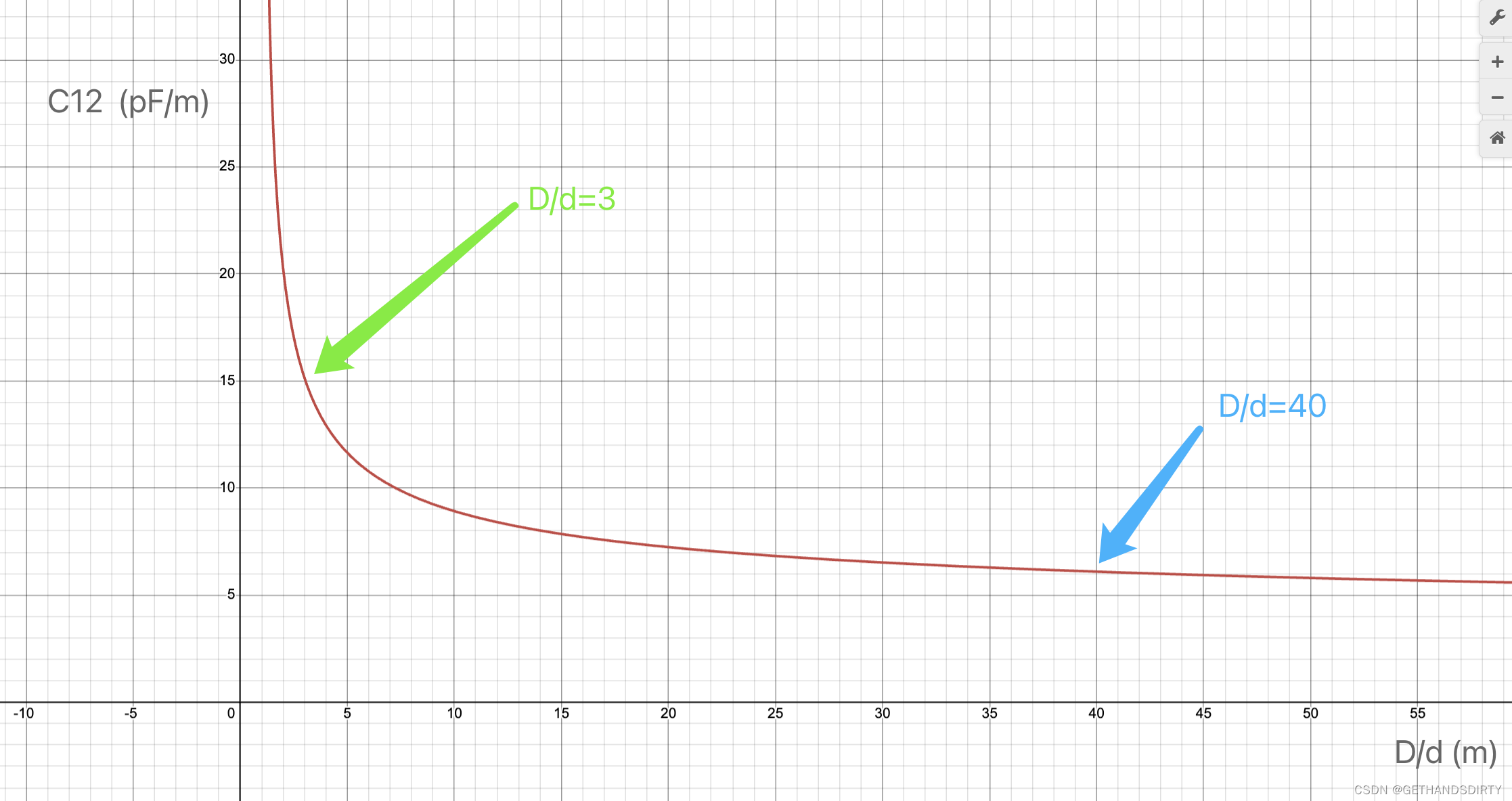

离多远为好呢?这里主要看布线空间(导线间距)与电容耦合大小之间的一个权衡。

两个直径为d,间隔距离为D的平行导线之间的电容是:

函数略复杂,绘出来直观看:

图中有两个信息:- 曲线拐点大概在D/d=3处,也就是说当D/d > 3时,通过增加导线间隔距离来减少导线之间的电容耦合的效果没有那么明显(边际递减),并且PCB布线空间也比较有限,权衡下来,使得导线间距大于3倍线宽(导线直径)就可以,这就是著名的布线「3W原则」的由来。

- 当D/d > 40时,增加导线间距已基本不可能再减小电容耦合。

2.当R的阻抗比寄生电容C12+C2G的阻抗更高

即:

此时耦合电压公式简化为:

此时噪声电压与导体1的信号频率w无关,当C12与C2G确定后(V1我们轻易无法改变),几乎是一个常数,所以重点还是在于将C12降低。

3.小结

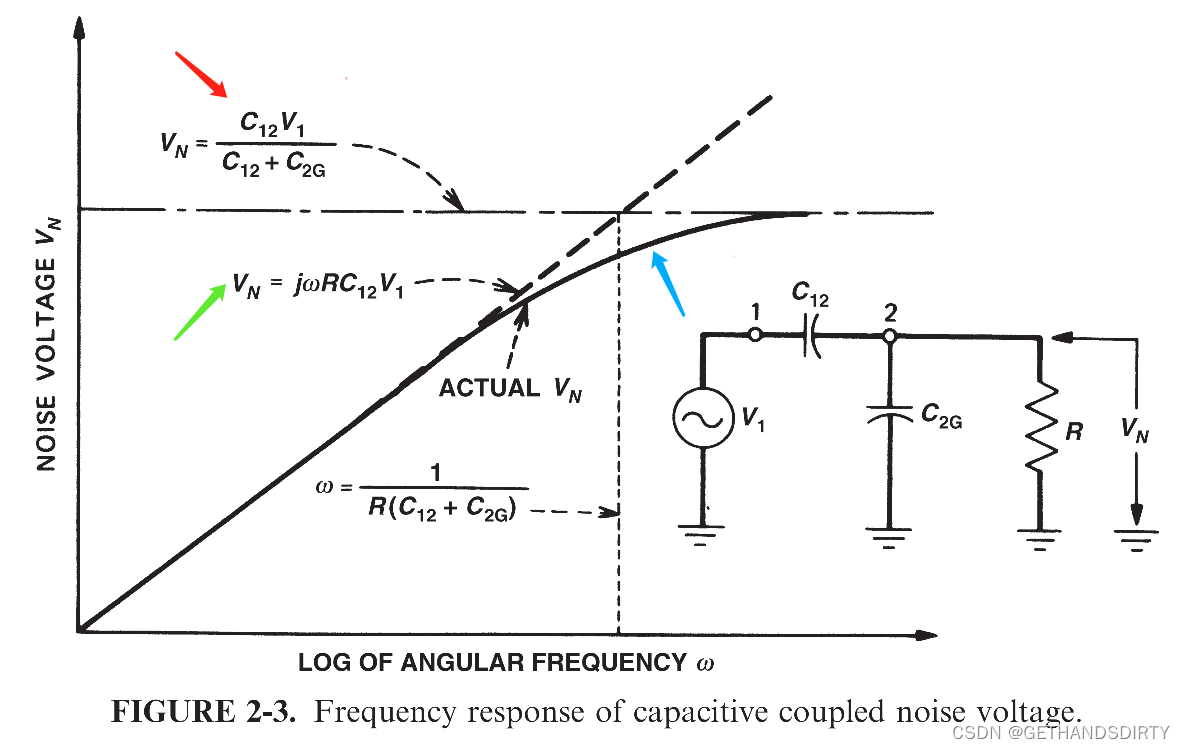

以上所有情况可以用一张图来表示:

此时假设电路完全确定,即C12,C2G,R,V1不变:

- 上图中「蓝色箭头」指示的是两根裸露导体发生电容耦合时,噪声接收电路(导体2)的耦合电压VN随着噪声源(导体1)的信号频率的变化而变化的曲线;

- 上图中「绿色箭头」指示的是当R的阻抗比寄生电容C12+C2G的阻抗更低时的曲线,此时,噪声接收电路(导体2)的耦合电压VN相对于噪声源(导体1)的信号频率是一个斜率不变的直线;

- 上图中「红色箭头」指示的是当R的阻抗比寄生电容C12+C2G的阻抗更高时的曲线,由于此时VN与频率w无关,因此是一个常数,这也是最大的噪声耦合值。

二、电场耦合分析进阶版本——带屏蔽线的两根导体之间的耦合

1.屏蔽层完全包裹导体2,屏蔽层未接地,导体2没有端接

- 屏蔽层完全包裹导体2:是指导体2完全没有超出屏蔽层,且屏蔽层是完整的(屏蔽层没有孔,例如编织屏蔽层),这是一种理想情况;

- 屏蔽层未接地:屏蔽层没有对地端接,可视为对地阻抗非常大;

- 导体2没有端接:连接到导体2的阻抗只有其与屏蔽层的耦合电容C2S。

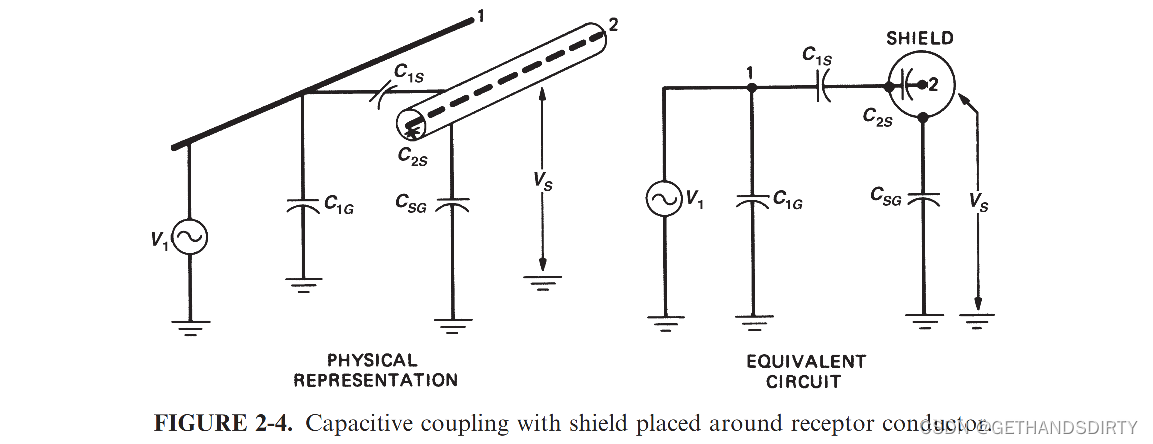

该情况下的模型及其等效电路如下图所示:

这种情况下:

- 由于屏蔽层的完全包裹,导体1与导体2之间没有直接的电容耦合;

- 屏蔽层可以看做是一根没有被屏蔽的导体,暴露在导体1的电场中,因此屏蔽层会受导体1电容耦合的影响;

- 若屏蔽层上有来自于导体1的噪声电压,则该噪声电压的电场与导体2的电场之间是有交互和重叠的,此时屏蔽层的电压会耦合到导体2上去。

接下来讨论这种情况下导体2上的耦合电压。

-

导体1对于屏蔽层的电容耦合:

由于屏蔽层对地没有端接(即阻抗非常大),因此可以用前面讨论的「当R的阻抗比寄生电容C12+C2G的阻抗更高」情况下的公式来确定导体1耦合到屏蔽层上的噪声电压Vs:

其中:- C1s是导线1和屏蔽层之间的寄生电容;

- Csg是屏蔽层和GND之间的电容。

-

屏蔽层对于导体2的电容耦合:

继续使用公式:

此时C2G=0,所以:

上述结果表明,即使加了看似完美的屏蔽层(完全包裹),但屏蔽层并未减小导线2拾取到的噪声电压。因此,若想减小噪声电压,需将屏蔽层接地,见下述讨论。

2.屏蔽层完全包裹导体2,屏蔽层接地,导体2没有端接

这种情况下,其它条件与上一种情况一致,只有一个不同之处,即屏蔽层从不接地变为了接地,此时无论导体1的电压耦合多少到屏蔽层上(Vs),随着屏蔽层的接地,Vs都会变为0。

那么上述导体2拾取噪声电压的公式便变成了:

因此可以得出结论:「在电容耦合中,屏蔽层必须接地,否则它是无效的」。

接下来我们讨论不那么理想的情况。

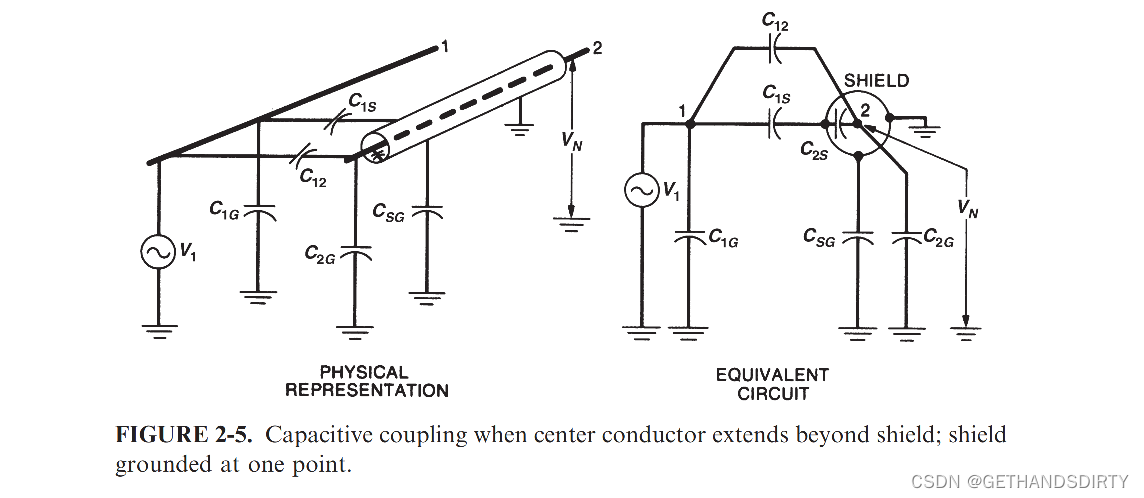

3.屏蔽层未完全包裹导体2,屏蔽层接地,导体2没有端接

在实际情况中,屏蔽层无法完全包裹导体,此时的模型及等效电路如下图所示:

此时与上面情况2相比,会多出两种电容,C12和C2G,这两种电容的存在是因为导体2的两端超出了屏蔽层,以及屏蔽层上有孔(比如编织屏蔽层),那么此时,即使屏蔽层接地,也会有噪声电压从导体1直接耦合到导体2上,但此时C12和C2G会比导体2没有屏蔽层时小很多。

此时耦合到导体2上的噪声电压为:

这里的C2s是导体2与屏蔽层之间的电容,由于屏蔽层接地,那么C2s相当于是导体2的另一个对地电容,即与C2G并联。

由这种情况下VN的公式可知,此时VN主要取决于导体2超出屏蔽层的长度,因此「有效的屏蔽层需要良好的接地,且使得导体超出屏蔽层长度最小」。

NOTE:假如走线不超过1/20波长,单点接地就是一个比较良好的屏蔽接地,若走见较长,则需要多点接地以保证接地性能良好。

接下来讨论最复杂的、最接近实际的情况。

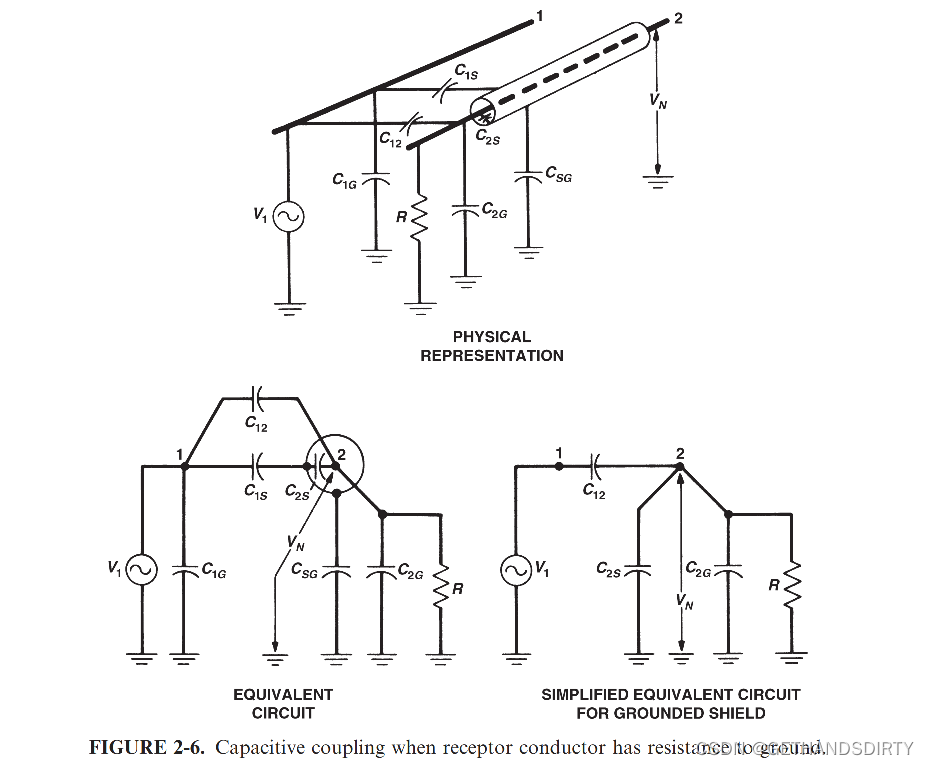

4.屏蔽层未完全包裹导体2,屏蔽层接地,导体2有端接R

实际情况中,导体2一般有端接电阻(即具有有限的接地电阻),模型及等效电路如下图所示。

左下角的等效电路相对复杂,但当屏蔽层接地时,等效电路可以简化为右下角的电路。

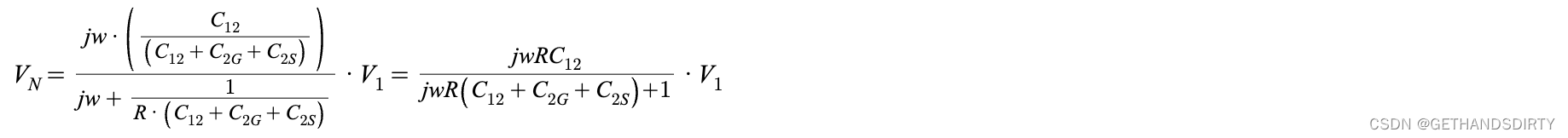

简化后的等效电路几乎与本文开始讨论的两根裸露导体之间的电容耦合模型是一样的(见本文的第一张图),只是多了一个与C2G并联的C2S。此时,耦合到导体2的噪声电压为:

运用和本文初同样的分析方法,当:

则耦合到导体2的噪声电压为:

此时VN的表达式看起来与本文开始讨论的「导体2裸露情况时」的表达式相同,但实际上这里的C12由于屏蔽层的的存在会大减小,此时的C12主要由导体1和导体2未屏蔽部分的电容(导体2伸出屏蔽层的部分,以及屏蔽层编织层上的孔露出的部分)组成。

总结

屏蔽层对于减小电场耦合(电容耦合)到底有没有用呢?有用!但是:

有效的屏蔽层需要良好的接地,且使得导体超出屏蔽层长度最小。

下一篇,让我们来看看磁场耦合(电感耦合)。

800

800

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?