1、FIR滤波器总体设计

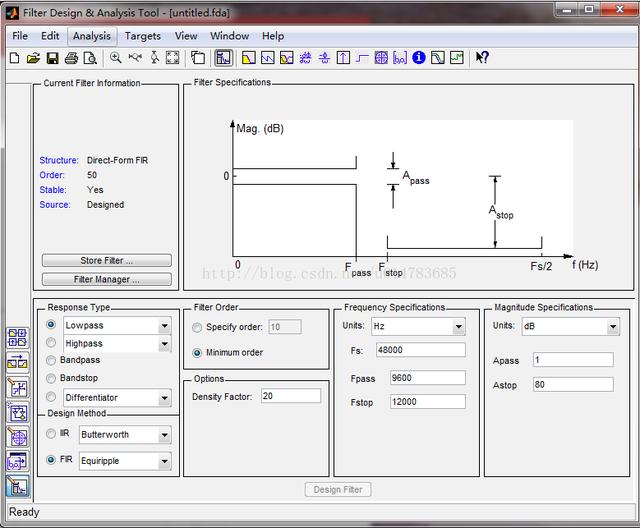

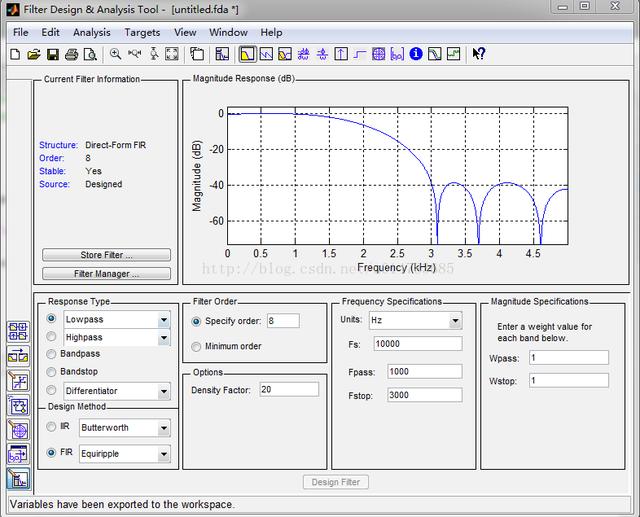

本设计是基于FPGA实现一个8阶的FIR数字低通滤波器。本次设计首先利用MATLAB中的FDAtool工具设计出一个采样频率为5KHZ、截止频率为1KHZ的FIR低通滤波器,通过FDAtool导出8点系数,然后将系数进行放大、取整,以便于在FPGA中使用,最后通过QuartusII进行Verilog语言编写滤波器算法,然后通过Modesim仿真结果和MATLAB仿真结果的比较来验证该滤波器的正确性。

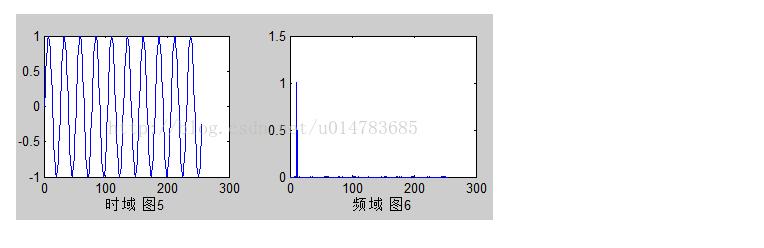

首先由MATLAB生成一个由三个正弦波叠加的待滤波信号,三个正弦波的频率分别是1KHZ,3KHZ,4KHZ。然后将待滤波信号送入Modesim仿真,观察滤波后的波形,再利用MATLAB里面的conv函数将滤波器系数和待滤波信号卷积并观察滤波后的波形图,将Modesim的仿真结果和MATLAB的仿真结果比较并验证在FPGA中滤波器算法的正确性。

2、FIR滤波器原理

在学习数字信号处理时,滤波器是重点,数字滤波器有很多种,比如FIR、IIR、LMS等滤波算法,FIR (Finite Impulse Response)滤波器的特点是它的冲击响应是有限的,它跟过去的信号无关,所以在使用时容易实现,速度快。

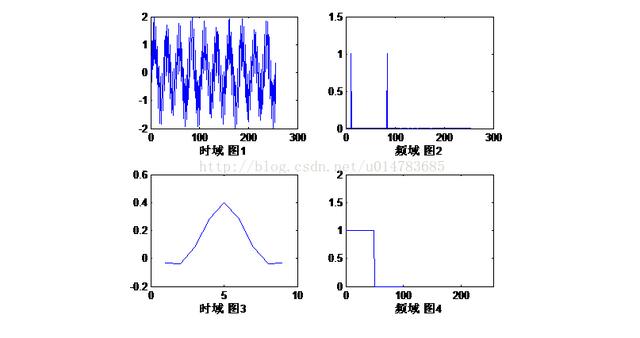

要理解FIR滤波器,需要知道信号的频域跟时域的关系,信号的频谱就是信号在频域上的表现形式,如果一个信号由2个正弦波叠加(图1)而成,我们在时域是看不出什么规律的,将信号进行傅里叶变换到频域(图2),我们就可以很清楚的看到该信号是由2个正弦波叠加而成的。

图7

本文详细介绍了如何使用MATLAB的FDAtool设计一个8阶FIR低通滤波器,采样频率5KHZ,截止频率1KHZ。设计过程包括在MATLAB中生成待滤波信号,导出滤波器系数,放大取整以适应FPGA。然后通过QuartusII使用Verilog编写FPGA滤波器算法,并在 Modesim 进行仿真验证。同时,对比MATLAB仿真结果,确保FPGA实现的正确性。

本文详细介绍了如何使用MATLAB的FDAtool设计一个8阶FIR低通滤波器,采样频率5KHZ,截止频率1KHZ。设计过程包括在MATLAB中生成待滤波信号,导出滤波器系数,放大取整以适应FPGA。然后通过QuartusII使用Verilog编写FPGA滤波器算法,并在 Modesim 进行仿真验证。同时,对比MATLAB仿真结果,确保FPGA实现的正确性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2071

2071

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?