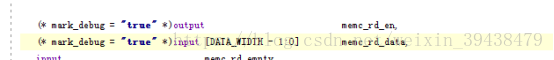

一、在想要抓取的信号之前添加(* mark_debug = "true" *)、保存、编译。如:

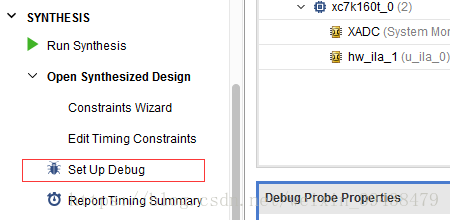

二、编译完成之后点击set up debug。

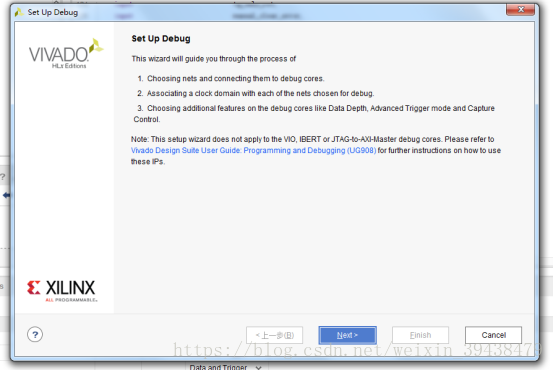

点击下一步.....

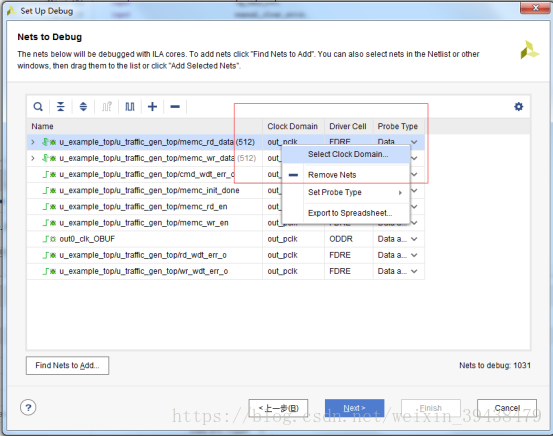

直至出现如下页面

右键clock domain-->select clock domain,选择抓取信号的参考时钟;注意:时钟的选取一定要选择free clock。否则编译后会发现是无效的,那将耗费大量时间。

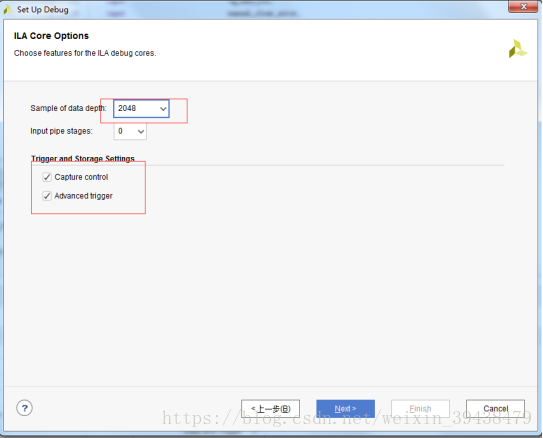

Sample of data depth 抓取信号的深度;选择capture control 与advanced trigger可以使用高级的抓取操作。设置好后点击Next-->finish。

1、点击重新编译生成bit文件。

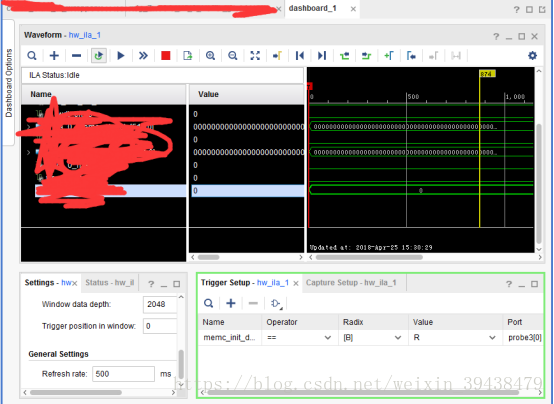

2、编译完成后,若选取的时钟没有问题那么在你将该bit和ltx文件下载到板子上后会自动弹出如下页面:

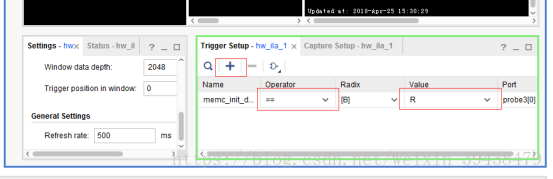

在下图中点击“+”按钮可添加触发信号,可设置触发条件。

注意:

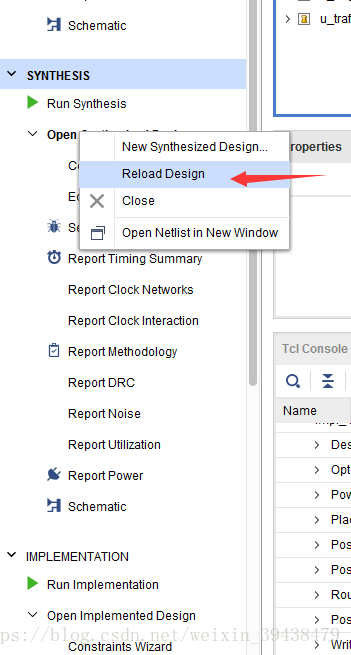

2、有时在代码中加入(* mark_debug = "true" *)后找不到信号,按如下操作

Reload Design之后点击Run Implementation,运行完成后再次点击Set Up Uebug后你想要抓取的信号就会出来了。

本文介绍了一种在硬件设计中调试信号的方法,包括如何标记信号、设置调试环境及进行信号捕获等步骤。通过此方法,可以帮助工程师更有效地定位问题并解决硬件调试中的难题。

本文介绍了一种在硬件设计中调试信号的方法,包括如何标记信号、设置调试环境及进行信号捕获等步骤。通过此方法,可以帮助工程师更有效地定位问题并解决硬件调试中的难题。

246

246

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?