flags.DEFINE

看了一篇论文,实现论文中的项目时,发现了这个知识点,查找了相关的知识,在此做一下关于tf.app.flags.DEFINE_xxx的说明。

tf.flags.DEFINE_xxx

tf.app.flags.DEFINE_xxx中的xxx就是数据类型,有string\float\boolean\bool\integer等。

简单来说,tf.app.flags.DEFINE_xxx就是添加命令行的可选参数。

下面从一个简单的实例来进行了解,建立一个test.py文件:

import tensorflow as tf

FLAGS = tf.app.flags.FLAGS

tf.app.flags.DEFINE_float('name_1', 0.015, 'input a float')

tf.app.flags.DEFINE_integer('name_2', 500, 'input a int')

tf.app.flags.DEFINE_string('name_3', 'look here', 'input a string')

print("FLAGS.flag_float:", FLAGS.name_1)

print("FLAGS.flag_int:", FLAGS.name_2)

print("FLAGS.flag_string:", FLAGS.name_3)

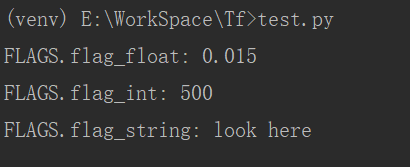

直接运行test.py文件,我们可以看到如下的结果:

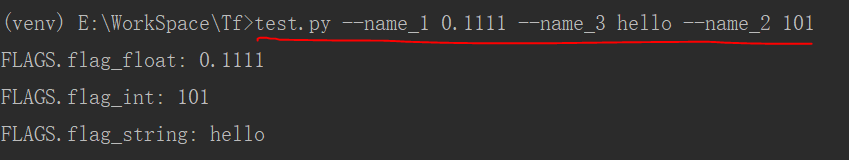

如果我们不直接运行,我们需要对其中的参数的赋值进行修改,可在在命令行中输入:

test.py --name_1 0.1111 --name_3 hello --name_2 101

可以得到如下图的结果

从上面可以看出,我们可以通过输入不同的文件名、参数,可以快速完成程序的调参和更换训练集的操作,不需要进入源码中更改。

tf.app.flags.FLAGS就是Tensorflow内部的一个全局变量存储器,同时可以用于命令行参数的处理。

本文深入解析tf.app.flags.DEFINE_xxx在TensorFlow中的应用,通过实例演示如何利用命令行参数进行高效调参,避免频繁修改源码。

本文深入解析tf.app.flags.DEFINE_xxx在TensorFlow中的应用,通过实例演示如何利用命令行参数进行高效调参,避免频繁修改源码。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?