1、有符号位符号数扩展

符号扩展是计算机算术中在保留数字的符号(正/负)和值的同时增加二进制数的位数的操作。例如10的二进制数“ 00 1010”,并且符号扩展操作将字长增加到16位,则新的表示形式就是“ 0000 0000 0000 1010”。-15的二进制补码值“1111110001”,并且将其符号扩展为16位,则新表示为“1111 1111 1111 0001 ”。

假设a和b是无符号数,是16位,out1 是17位,做减法的时候系统会自动帮我们补位0,如果a和b是有符号数,这时候我们就不能依靠系统来进行自动补位,我们要手动进行补位,不然得出来的结论是不正确的。

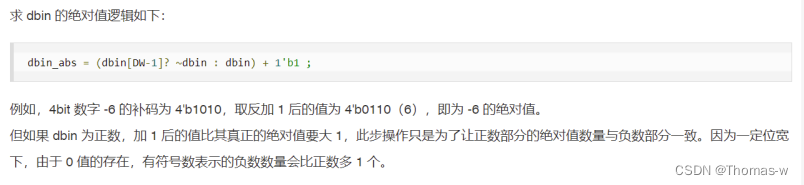

2、绝对值

本文涵盖了计算机算术的基础概念,如符号扩展和绝对值计算,以及有符号数到无符号数的转换。讨论了组合电路和时序电路的区别,强调了同步电路和异步电路在时序控制上的差异。此外,还提到了同步复位和异步复位在系统复位操作中的作用,并解释了阻塞和非阻塞赋值在硬件描述语言中的应用。

本文涵盖了计算机算术的基础概念,如符号扩展和绝对值计算,以及有符号数到无符号数的转换。讨论了组合电路和时序电路的区别,强调了同步电路和异步电路在时序控制上的差异。此外,还提到了同步复位和异步复位在系统复位操作中的作用,并解释了阻塞和非阻塞赋值在硬件描述语言中的应用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9044

9044

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?