本节讲解Ultrascale IDELAYE3的TIME模式的延时;

TIME模式下延时:

由于关于IDELAYE3原语,COUNT模式下只有抽头计数,没有具体的延时考量,不过多关注;

TIME模式下,延时逻辑却又与7系列简单的延时逻辑差别较大,且仿真中原语没有实现补偿功能和时钟/数据对齐延迟Align_Dealy,导致其仿真现象和实际上板现象有差别,且不容易理解其工作机制,而且在实际工作时ps级的延时也没法像在仿真中一样可以直接观察到,接下来就上板测试简单查看下其现象,下面部分推测不保证完全正确,仅作为个人观点;

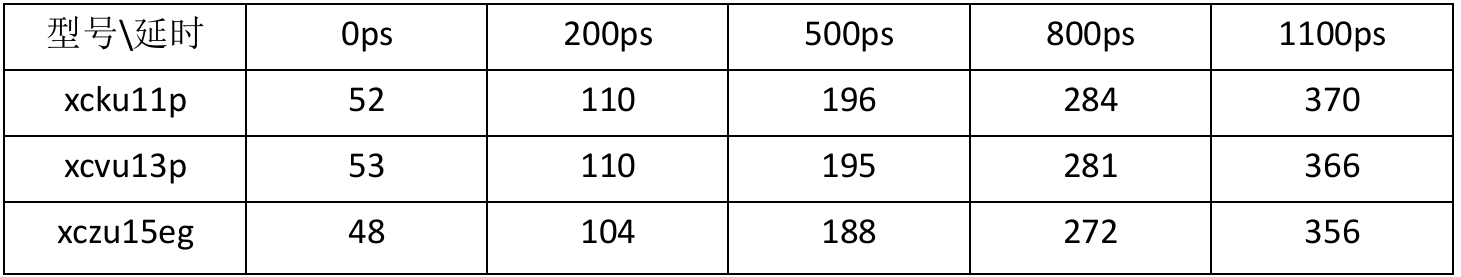

TIME模式延时抽头记录:

暂时能测试的有三张Ultrascale+架构的卡,分别是

Kintex Ultrascale+的xcku11p-ffve1517-2-i,

Virtex Ultrascale+的xcvu13p-figd2104-2-e,

ZYNQ MPSOC Ultrascale+的xczu15eg-ffvb1156-2-i;

由于实际上板后也没有办法能查看到其实际对数据线的延时,所以这里我们主要以TIME模式下,FIXED模式下的输出抽头值为观察对象;

修改DELAY_VALUE参数生成BIT上板测试后,记录观察到的抽头值:

从记录值可以看到,不同的板卡,设置延时时间后,其达成该延时的所使用的抽头个数也不同,测试时三张卡芯片在25到30度左右,且它们的数值有时会有±1的波动,不是恒定该值的,说明其补偿机制正在工作;

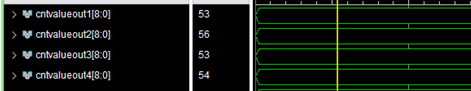

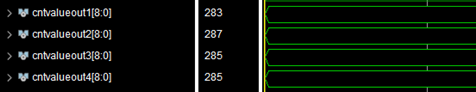

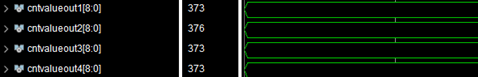

尝试xcku11p板卡同时例化4个IDELAYE3:

设置0ps,抽头值分别为53、56、53、54;

设置800ps,抽头值分别为283、287、285、285;

设置1100ps,抽头值分别为373、376、373、373;

可以看到,就算同一块板子,不同的IDELAYE3组件的抽头延时都会是不同的;

前面曾讲述过,TIME模式下,在BISC过程中将使用输入延迟线的多个抽头来消除接收器的第一个数据捕获器处的数据与时钟之间的插入延迟差Align_Delay,当数据经过IDELAYE3,输出数据线的延时总量是Align_Delay和DELAY_VALUE的总和,当然这里应该也要加上仿真中我们看到的一个0.144ns(不一定是该值)的固有的延时。

Xilinx官方文档介绍Align_Delay的值介于45到65个抽头之间,平均为50到54个抽头。

仿真时我们看到当DELAY_VALUE设置为0时,CNTVALUEOUT总线值为0,延时0.144ns,表示仿真中只体现了固有延迟,因为Align_Delay在仿真和Timing Report中都没有建模,无法观察;

所以当上板设置FIXED模式,将DELAY_VALUE延迟时间设置为0ps时,我们看到三张卡都有有一个不为0的抽头值,分别是52、53、48,这几个抽头值,就是TIME模式下的Align_Delay值,也符合官方所讲45到65之间;

接下来看其的延时精度和延时值,以xcku11p为例:

0ps时测得Align_Delay为52个抽头,200、500、800、1100ps分别为110、196、284、370;

Tap延时 = 总延时 /(总抽头 - Align_Delay)

按1100ps时的值进行计算:

Tap延时 = 1100ps/(370-52) = 3.4591195ps

可以看到其每个tap的延时值,那我们根据这个精度计算下200、500、800ps下的抽头值:

抽头值 = Align_Delay + (总延时 / Tap延时)

200ps抽头值 = 52 + 200/3.4591195 = 109.818 ≈ 110

500ps抽头值 = 52 + 500/3.4591195 = 196.545 ≈ 197

800ps抽头值 = 52 + 800/3.4591195 = 283.273 ≈ 283

可以看到其计算出的值基本符合ila观察到的值,且tap延时值符合Ultrascale+架构的2.1-12ps的tap延时精度范围;

使用相同方法,计算另外两张板卡记录的tap精度;

xcvu13p:

Align_Delay = 53;

Tap延时 = 1100ps/(366-53) = 3.514377ps

200ps抽头值 = 53 + 200/3. 514377= 109.9 ≈ 110

500ps抽头值 = 53 + 500/3. 514377= 195.27 ≈ 195

800ps抽头值 = 53 + 800/3. 514377= 280.64 ≈ 281

xczu15eg:

Align_Delay = 48;

Tap延时 = 1100ps/(356-48) = 3.571429ps

200ps抽头值 = 48 + 200/3. 571429= 103.999 ≈ 104

500ps抽头值 = 48 + 500/3. 571429= 187.999 ≈ 188

800ps抽头值 = 48 + 800/3. 571429= 271.999 ≈ 272

可以看到,三张板卡记录到的抽头值,都符合前述定义;

上述讲解的是延时总值和Tap延时精度还有Align_Delay的关系,但是TIME模式下还有VARIABLE和VAR_LOAD模式,在这个模式下,该如何保持修改抽头值后,能得到想要的延时值?

根据上述的延时计算,我们明白,想要得到一个比较准确的总延时值,那么需要知道该IDELAYE3的工作时刻的Align_Delay和Tap精度,

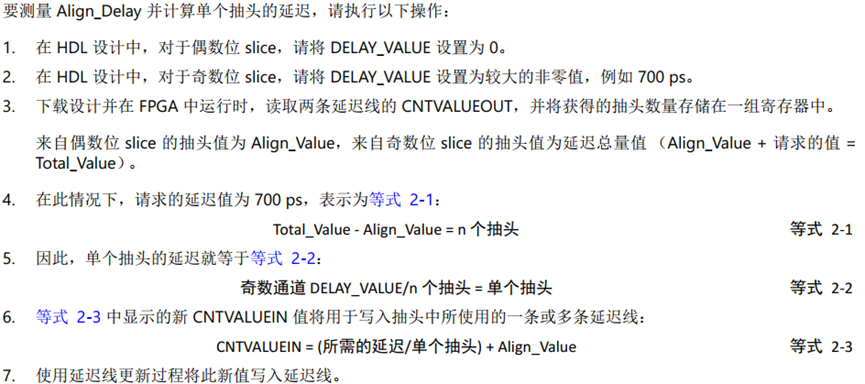

以下是官方文档的描述:

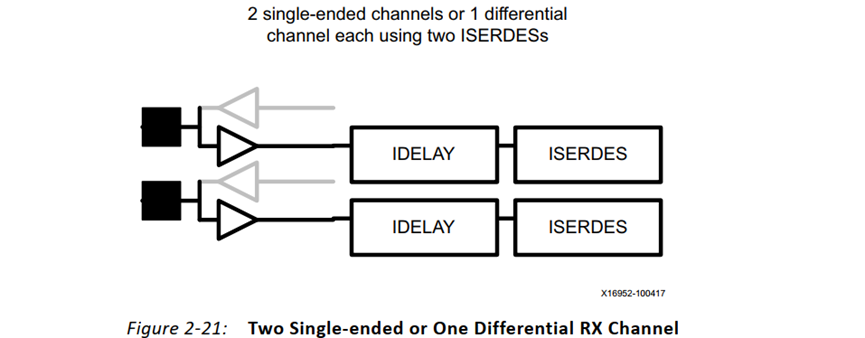

可以看到,官方文档描述的是,单端或差分输入时,单端例化两个相邻的IDELAYE3,差分就是两条线分别例化一个IDELAYE3,

一个IDELAYE3设置初始值0ps,那么这个原语输出的抽头值就是Align_Delay;

另一个IDELAYE3设置一个较大的初始值,如上述的700ps,主要是要避免这个原语的延时抽头值小于Align_Delay的抽头值范围,导致当使用类似(总抽头-Align_Delay)之类的式子计算时出现负值无法计算;

当两个IDELAYE3,一个上电能得到Align_Delay的抽头值,一个上电能得到一个较大延时值对应的抽头值,图中设置是700ps,我们根据这两个数值,就能得到我们将要设置的延时对应的总抽头值该设置多少;

但是上述方法,还是比较麻烦,因为如此写时还要多例化一个IDELAY组件,

如果需要的延时值不是非常精确,我们可以取官方提供的Align_Dealy抽头值的中间值54,作为要进行计算的Align_Dealy的抽头值;

可以按以下流程进行:

Align_Dealy = 54,为官方推荐使用的平均值;

从EN_VTC=1开始,在程序综合前,DELAY_VALUE设置为一个较大非零值DLY0,这是为了让其总抽头值较大,保证其能大于Align_Dealy,一般选择500ps以上就差不多;

在VAR_LOAD模式下,想要准确的切换到一个新的延时值DLY1,按以下操作:

1 将EN_VTC置0,然后等待10个时钟周期;

2 读取现在IDELAY的CNTVALUEOUT值,此时抽头值为DLY0延时的总抽头值;

3 加载新的CNTVALUEIN = (CNTVALUEOUT - Align_Dealy) (DLY1/DLY0) + Align_Dealy;

举一个前面测试过的例子,xcku11p记录值,其中想从DLY0=500ps变到DLY1=800ps,

记录的Align_Delay = 52,500ps的CNTVALUEOUT=196;

新的CNTVALUEIN = (196-52)(800/500)+52 = 282.4,接近284,

如果使用推荐的平均值54进行计算,CNTVALUEIN = (196-54)*(800/500)+54 =281.2,

所以当不想每次详细测量时,将上述的Align_Delay固定为54,其实数值也比较接近, 如果使用芯片的Align_Delay的平均值与54相差过大,那么使用观察到的值也可以;

4 新的CNTVALUEIN加载完毕后,等待10个时钟周期,将EN_VTC置1即可;

且注意在更该抽头线时一次调整不要超过8,否则信号可能会出现捕获故障;

本文章由威三学社出品

对课程感兴趣可以私信联系

1352

1352

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?