今天把小编昨天帮助社区训练营学员远程协助的一个经典案例分享给大家。希望能够帮助到更多需要帮助的人。如果各位想跟小编来系统学习数字后端设计实现的,可以联系小编。

数字IC后端手把手实战教程 | Innovus verify_drc VIA1 DRC Violation解析及脚本自动化修复方案

通过这个经典数字后端项目案例的学习,大家可以掌握到如何根据Innovus各种DRC Violation来分析drc violation原因,修复violation方法以及Calibre典型DRC Violation的修复方法。

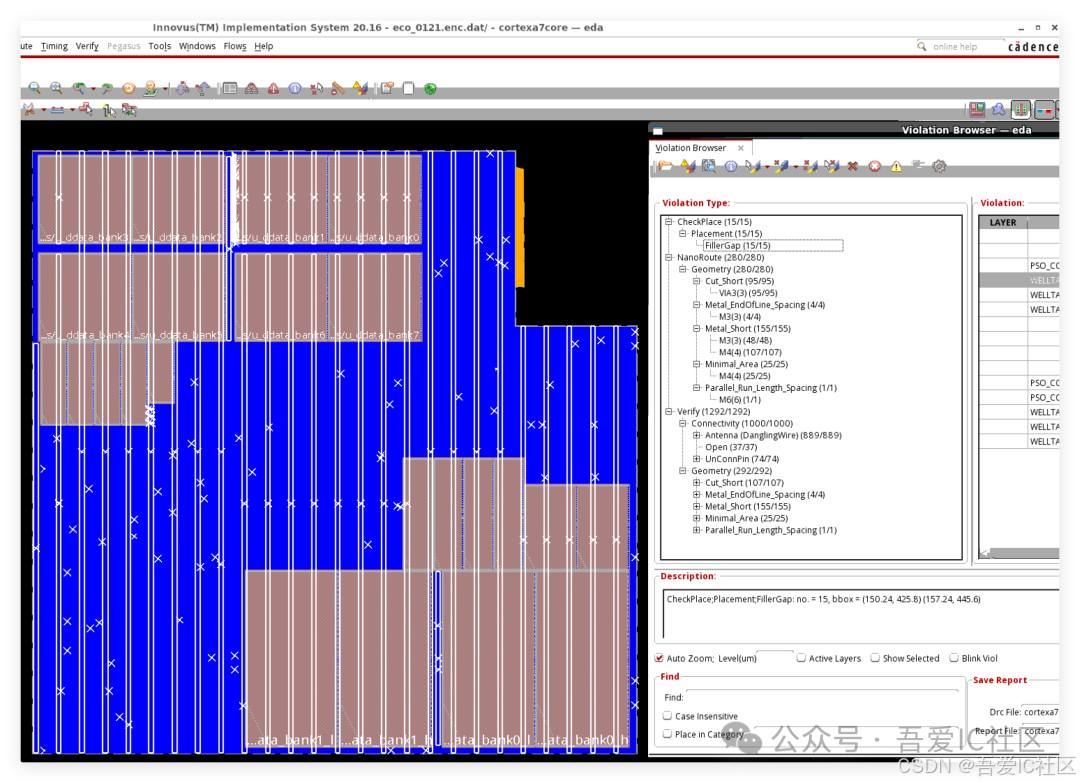

咋一看DRC Violation种类和数量都比较多,是不是看得晕头转向的?

别急,我们先整体看下DRC Violation的种类。是不是很容易发现整个Violation browser只显示CheckPlace,NanoRoute和Verify这三大类DRC Violation?

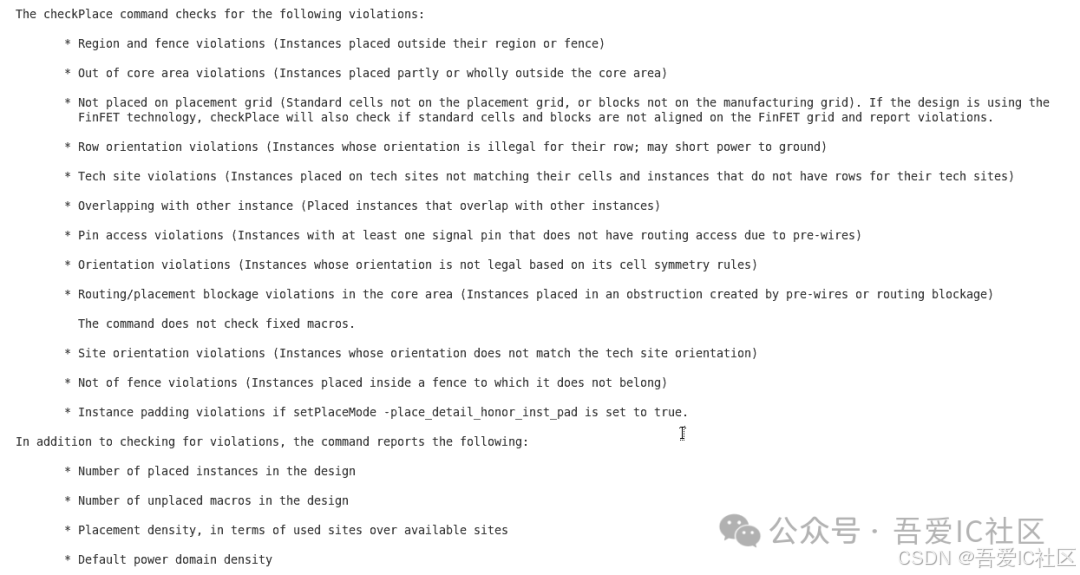

咱们训练营直播课一直强调checkPlace是检查设计中各种cell摆放是否符合placement constraint。这些约束条件主要有以下几种:

- PlacementBlk violation

2)Region/Fence Violation

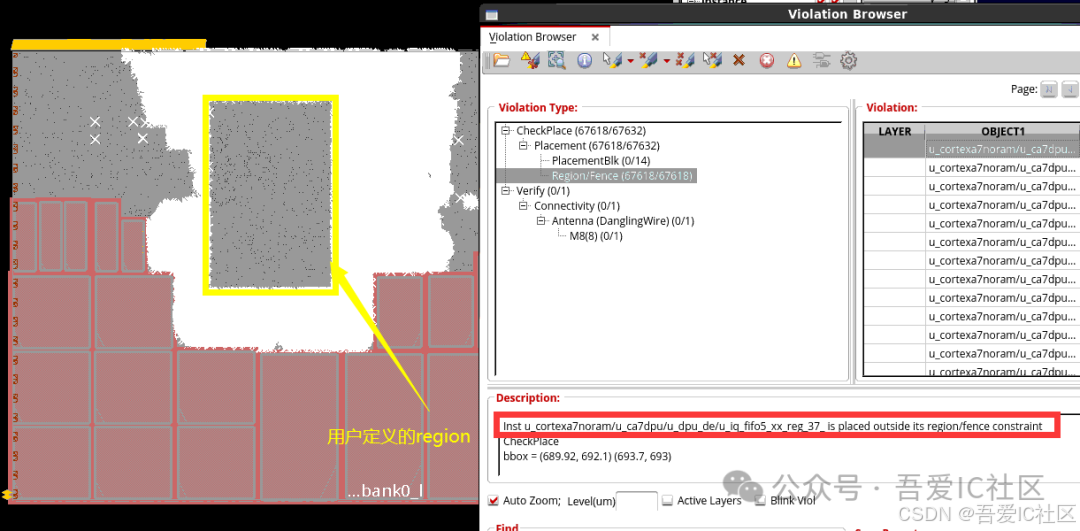

在咱们T28nm cortexa7core后端训练营中,我们知道该设计逻辑关键路径一定是DPU相关的path,而且需要严格控制好这个module的分布。如果工具自动摆放的结果不是很理想,我们可以给这个module添加region physical constraint。

【思考题】逻辑关键路径和物理关键路径区别?

这种其实是工具在报工具实际摆放的效果与用户设置的物理约束(region)不匹配。那这种一定会有DRC问题吗?显然不会,因为被摆放到dpu region之外的这些cell也是工具正常摆放出来的,而且都是legal的。

但是这里之所以会出现这个问题是因为学员所添加的region太小了。所以建议把这个module的region画大一点。

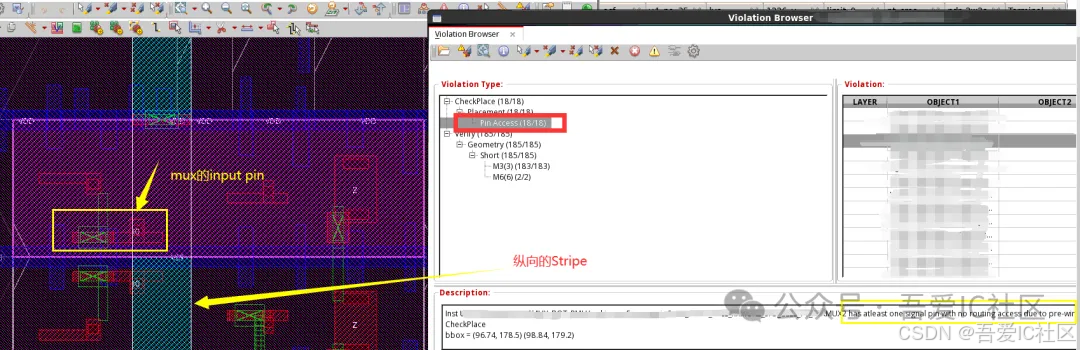

3)Pin Access Violation

更多关于IP,Macro,子模块接口,标准单元Pin Access DRC Violation出现场景及解决方案,可以通过搜索关键词“pin access” ,快速找到对应的后端实现教程(智能匹配大小写)。

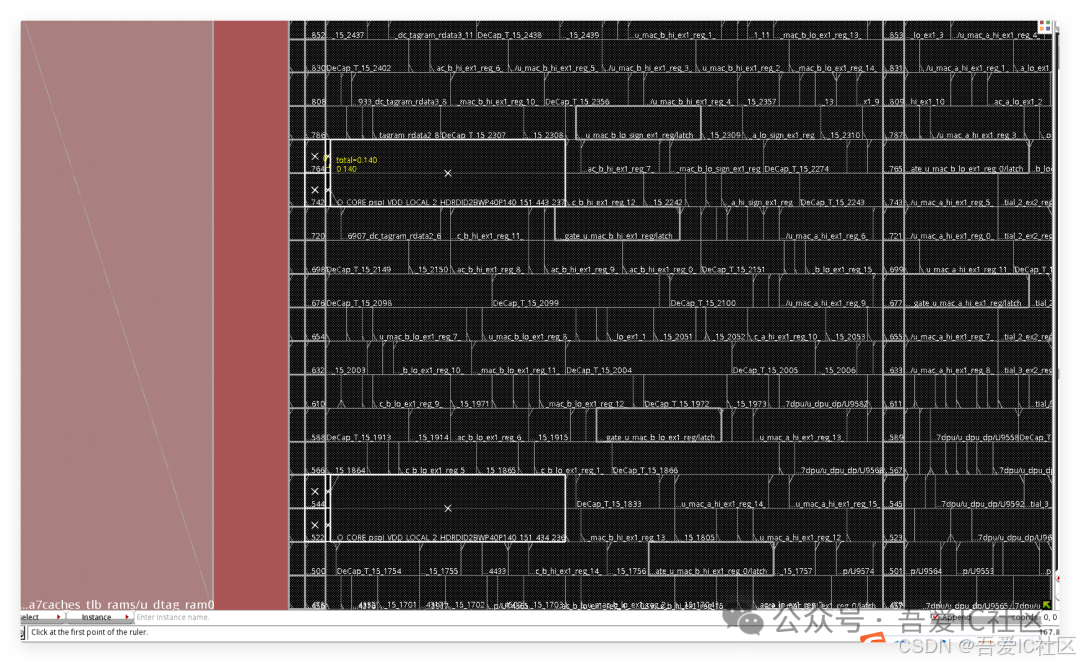

4)FillerGap Violation

这个是这个设计中Power Switch Cell和边上的TapCell之间存在一个基本site的间距0.14um。

看到这里很多学员都会有个疑问:“我在PR Flow中已经设置了inst gap最小必须是2,为何还会出现一倍Filler大小的缝隙呢”?

setPlaceMode -place_detail_legalization_inst_gap 2

原因是这个是两个physical only的cell间距不够,这两个cell都在在floorplan阶段就已经添加好了,而上面那个placeMode是约束工具在做placement的。

最终Calibre DRC检查这个DRC Violation属于假错!

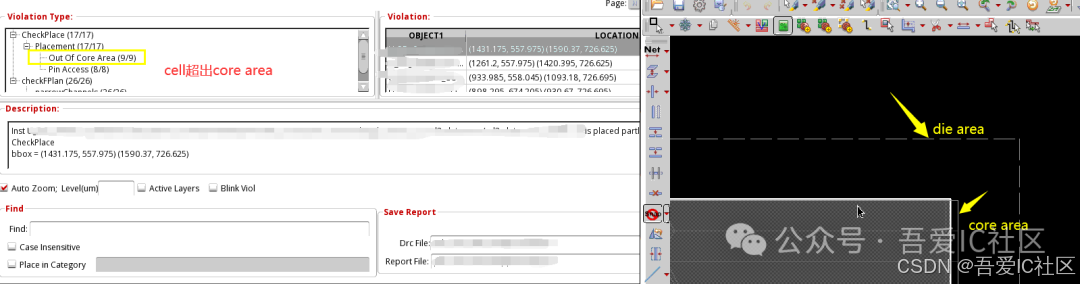

5)Out of Core area

任何cell只要在die area内都是合理的。

6)Cell overlap violation

这个是报告当前设计中存在重叠的cell。这类overlap的violation会导致base layer drc violation。在咱们训练营项目pt timing eco阶段会把PrimeTime输出的eco脚本返回Innovus,就需要做一下refinePlace和checkPlace。如果设计中存在cell overlap的情况,工具就会报告对应的checkPlace violation。

7)Placement Grid Violation

这类错大部分也是假的。这里分instance不在grid上和metal不在grid上两种。由于tech file中有定义metal的track,所以工具走出来的metal走线正常都会在grid上。

在FinFet工艺节点上,这项检查还会Fin的相关检查,比如Fin是否满足奇偶要求等。

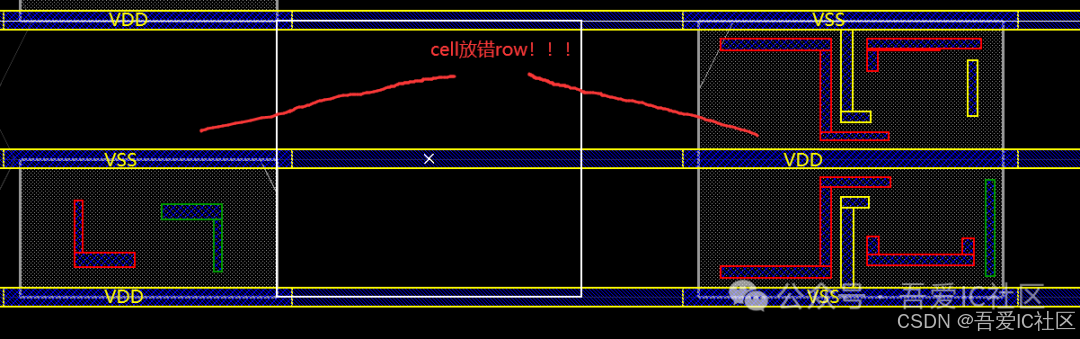

8)Row & Cell Orientation Violation

出现这类错需要特别关注,因为这个会导致cell的pg pin(VDD&VSS)和最终的power rail(follow pin)不匹配,即VDD pin可能会落在VSS的rail上。显然这种就会出现大规模的pg short问题。

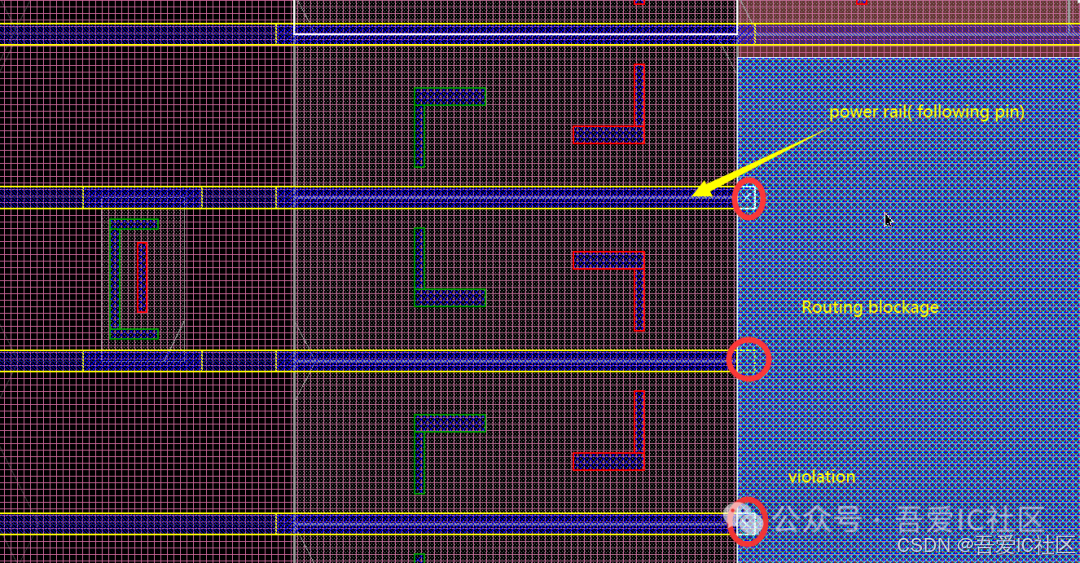

9)Preroute DRC Violation

这类preroute drc violation本质上还是由于右侧有routing blockage或route guide导致的。显然也是假错。

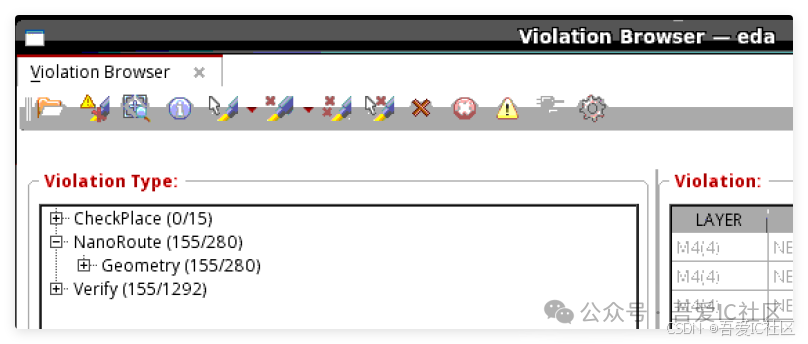

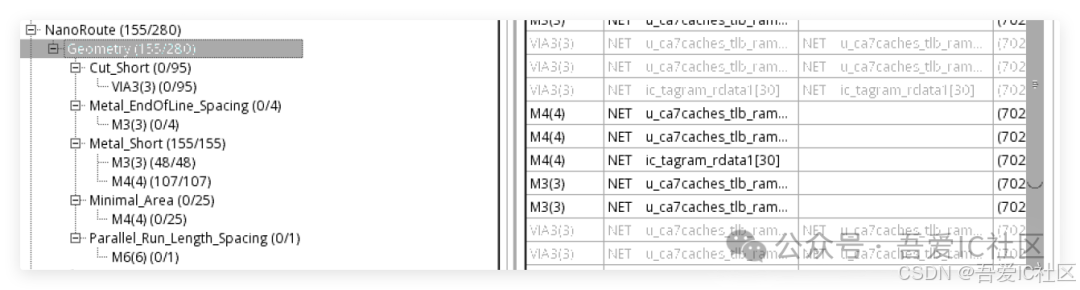

下面接着看NanoRoute的DRC Violation。

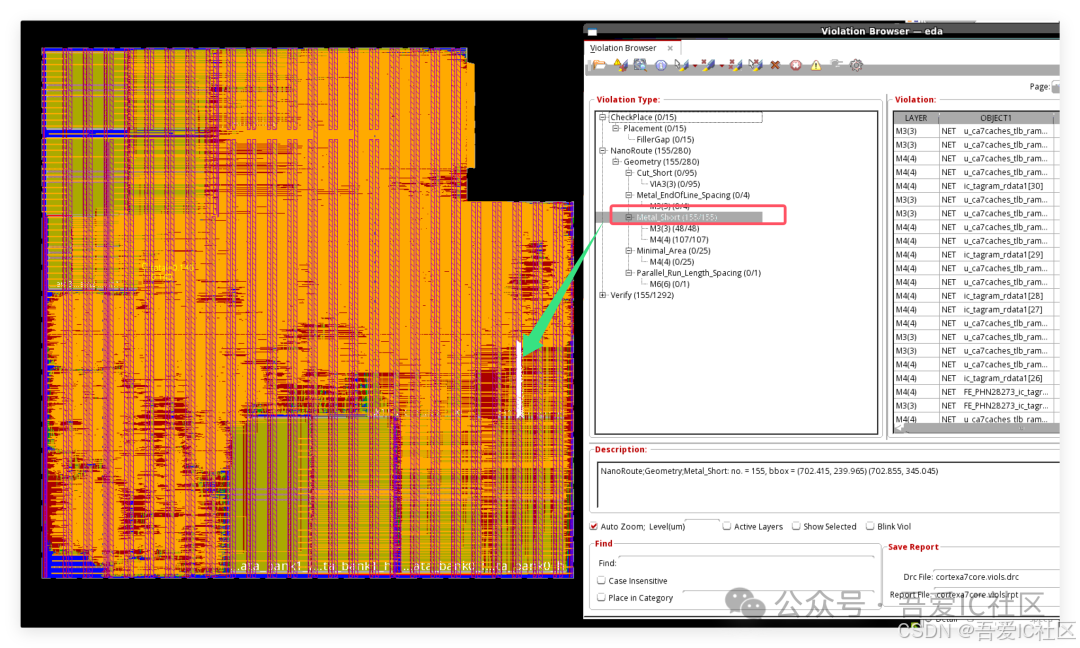

我们也反复强调NanoRoute DRC Violation优先看short种类和位置分布。

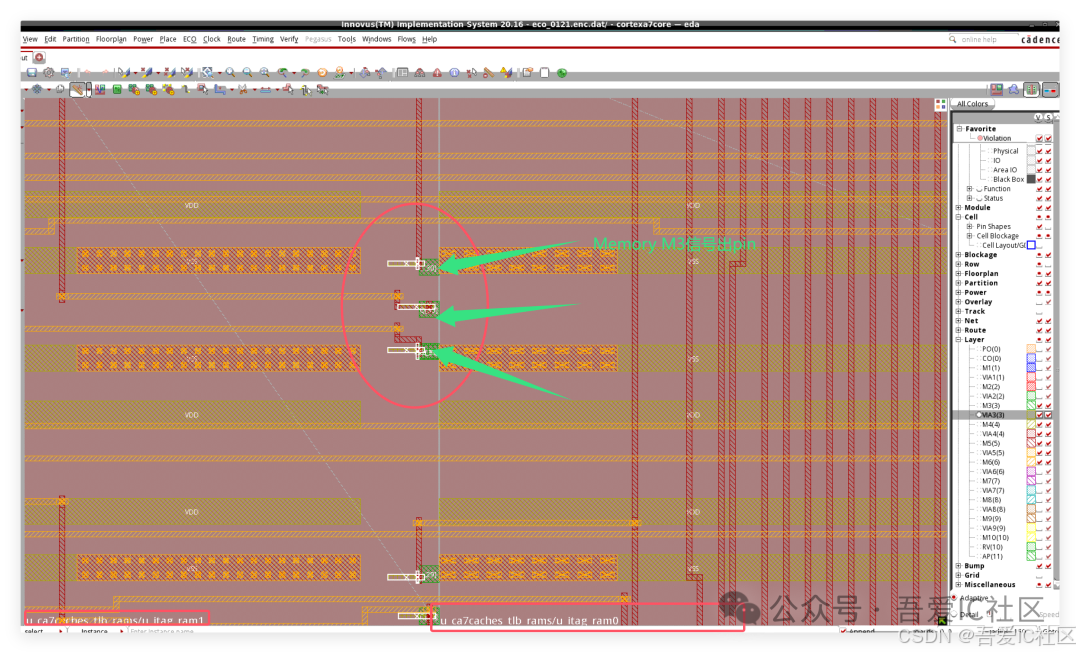

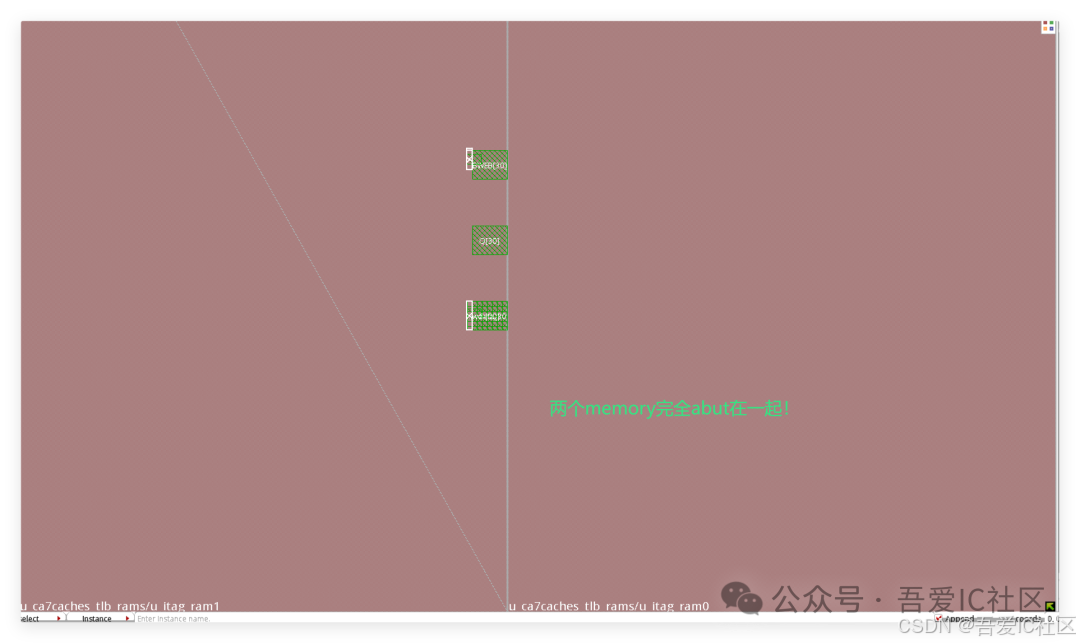

我们通过仅高亮(only show this type)Metal short来快速定位设计中所有short位置。通过定位我们发现这类violation是出现在memory出pin附近。

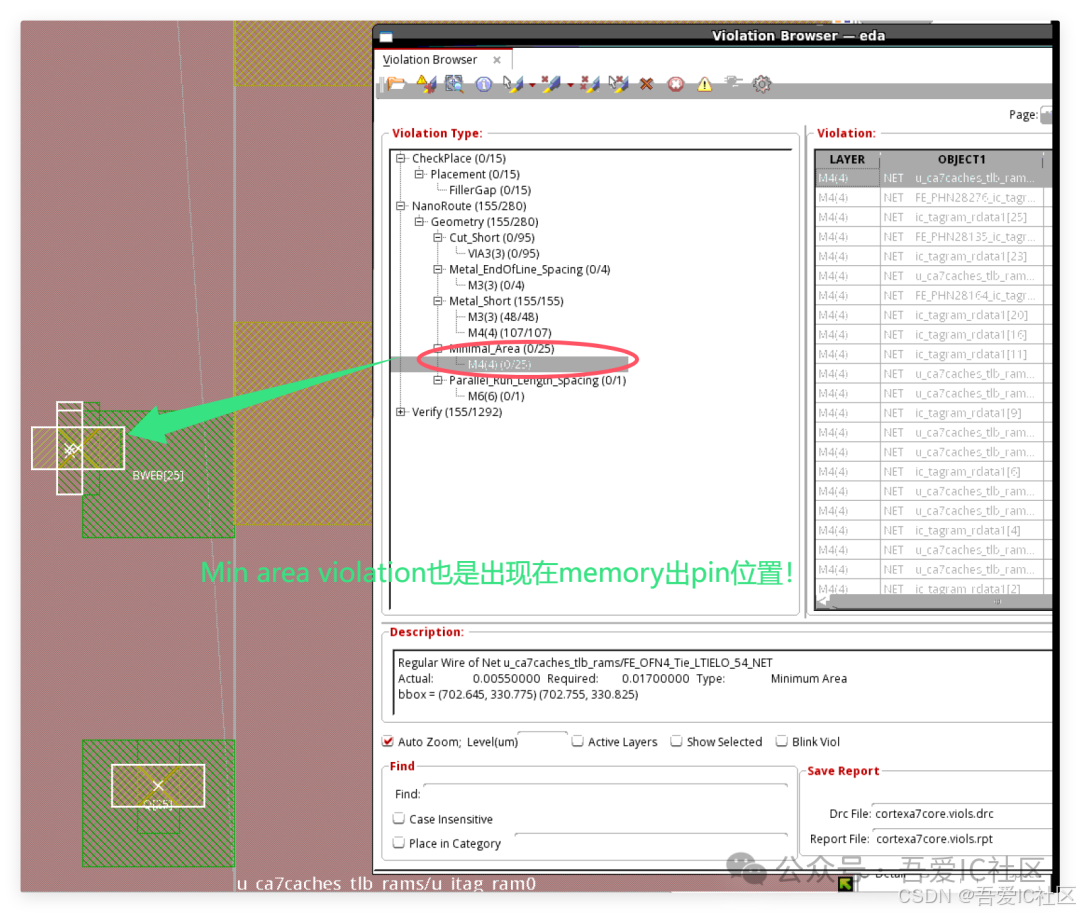

局部放大后就可以发现这类short是出现在memory M3出pin处。这里出现short的主要原因有以下几点:

1)这两颗memory之间没有任何间距(直接abut)

2)Memory身上M1-M4都存在cell blockage

至于M4 Min Area drc violation,通过定位很快发现这些violation也是在memory出pin处。主要原因是这些M3 pin要连出去很困难,而memory内部又不让走M4及以下的layer。

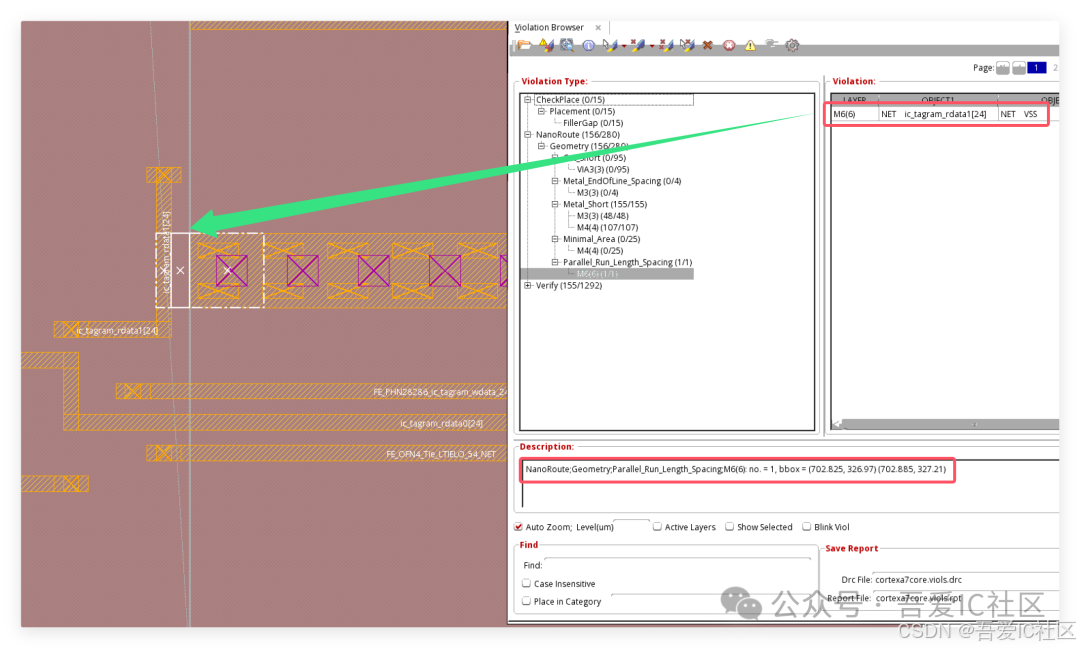

M6 Parallel Run Length Spacing Violation是存在一段M6 net和VSS net间距不够。

这种DRC Violation修复起来比较简单。只需要删掉原来那段M6 net shape,重新ecoRoute即可。

当然也可以直接在下图所示net处添加M6的routing blockage,然后直接ecoRoute即可。

除了checkPlace,nanoroute drc violation外,设计中还有一类verify drc violation。这类drc violation是使用verify_drc检查出来的结果。

【思考题】verify drc violation和NanoRoute drc violation有何差异?

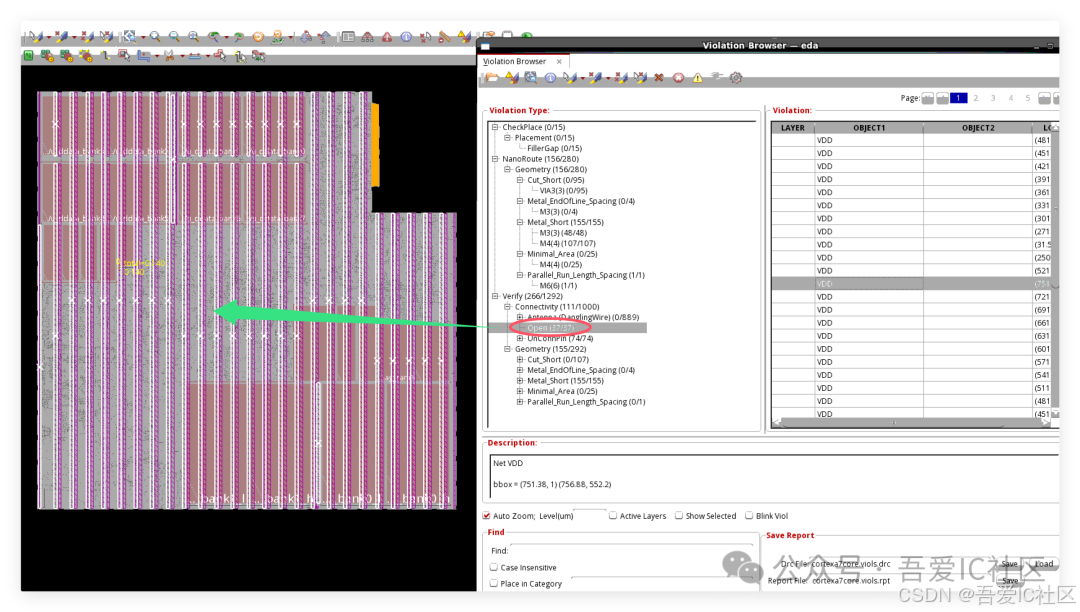

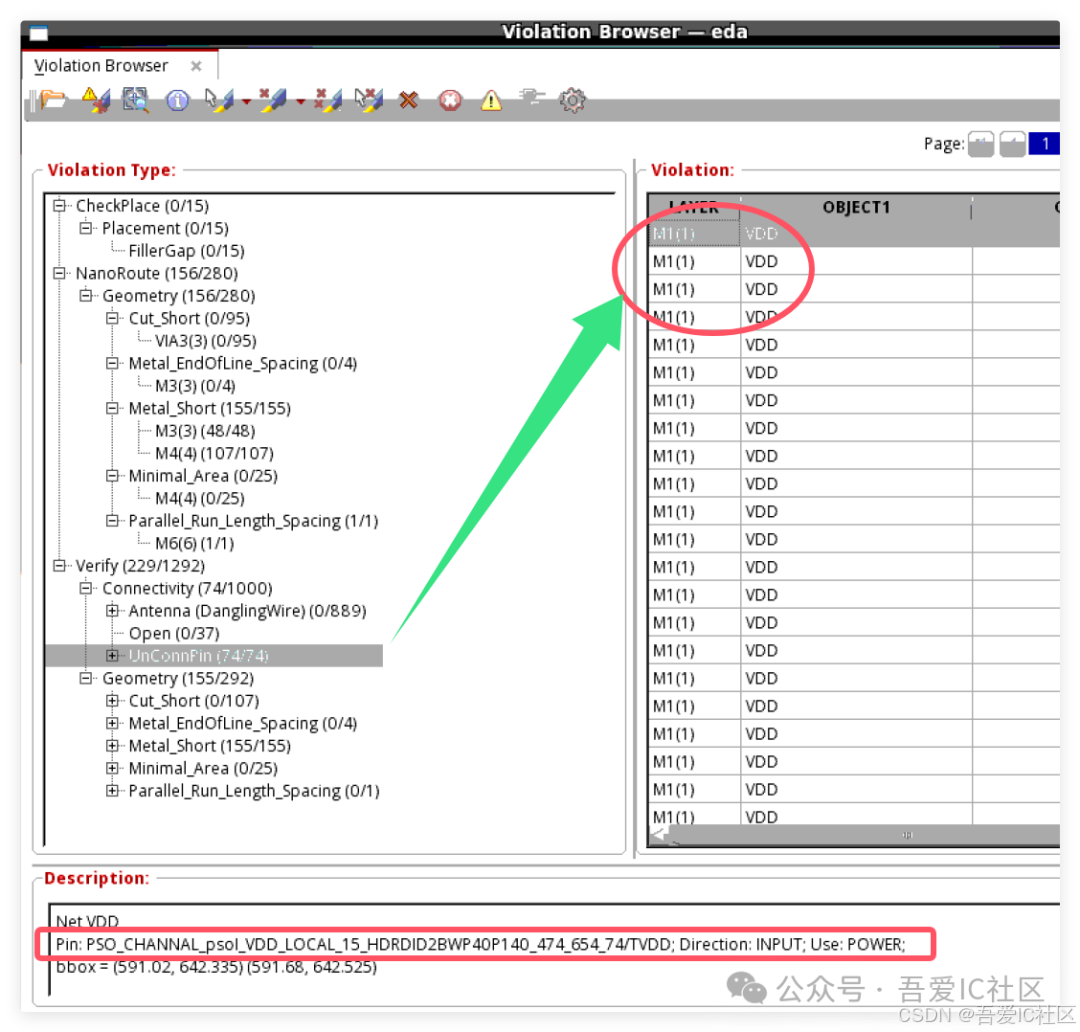

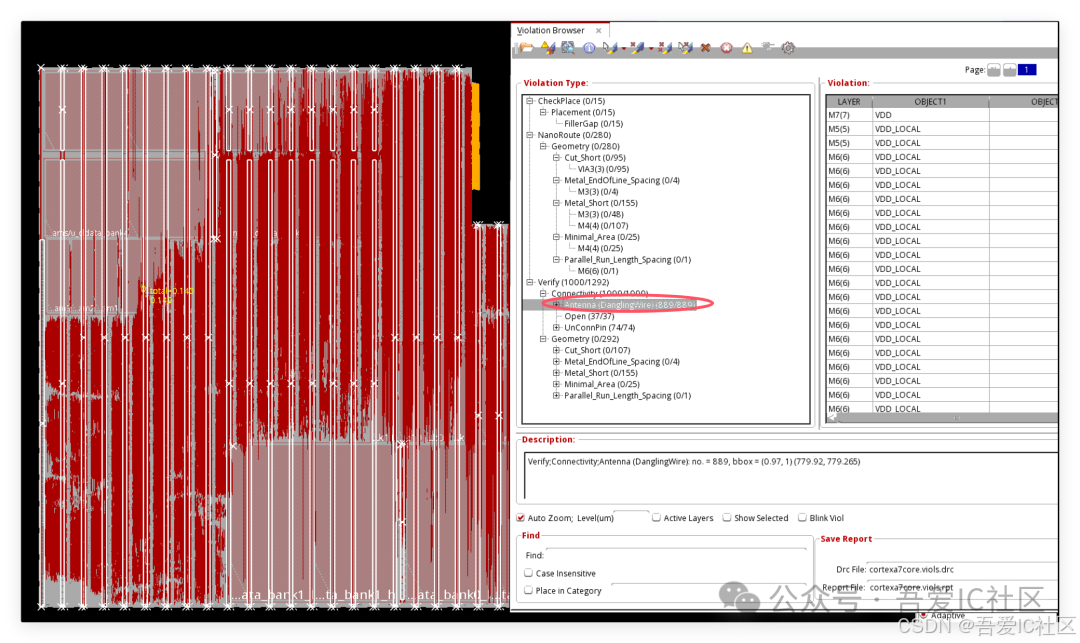

verify_drc不仅仅检查信号线,它还检查PG Net的drc violation。比如下图中的open和UnConnPin Violation。

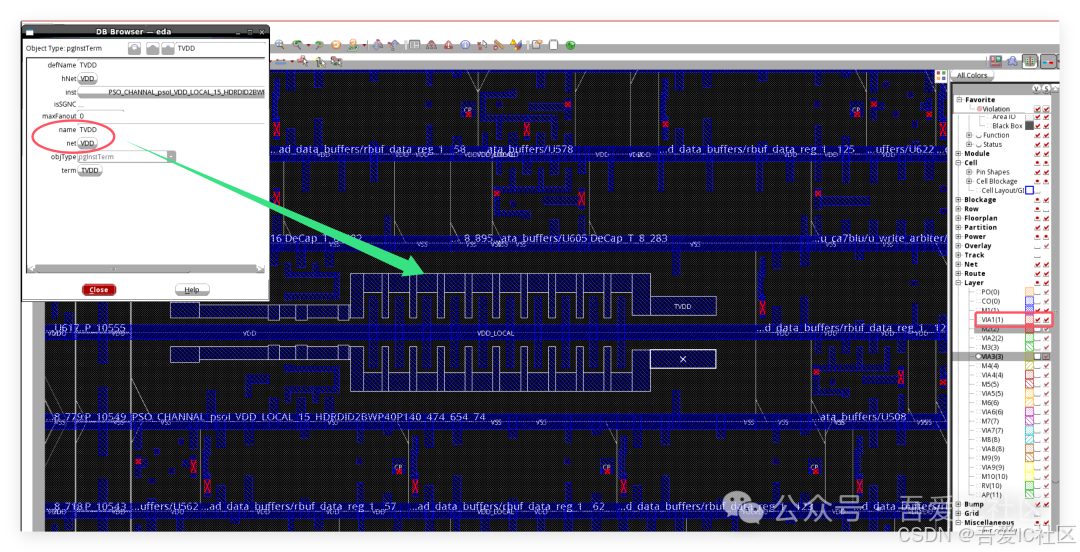

我们先来看看UnConnPin这类DRC Violation。通过高亮可以快速定位到Power Switch Cell M1 TVDD Pin所在位置,而且发现这类pin是连接到global VDD net,但物理上却没有连接到VDD PG Stripe!所以这里报没有连接的pin是非常正常的。

同样open violation是出现在纵向M7 Stripe上,共有37条这样的PG Stripe。由于每个M7 VDD是孤立存在的,所有这里工具会报open。但是我们直播课也介绍了这类open是假错。最新的T28nm后端训练营采用的是1P7M metal stack,模块级的M7已经是最高层的layer,后续想通过Calibre LVS检查,我们需要在PR database中添加上横向的AP VDD和VSS。

下面接着来看看这个学员跑完calibre drc检查后遇到的DRC Violation。

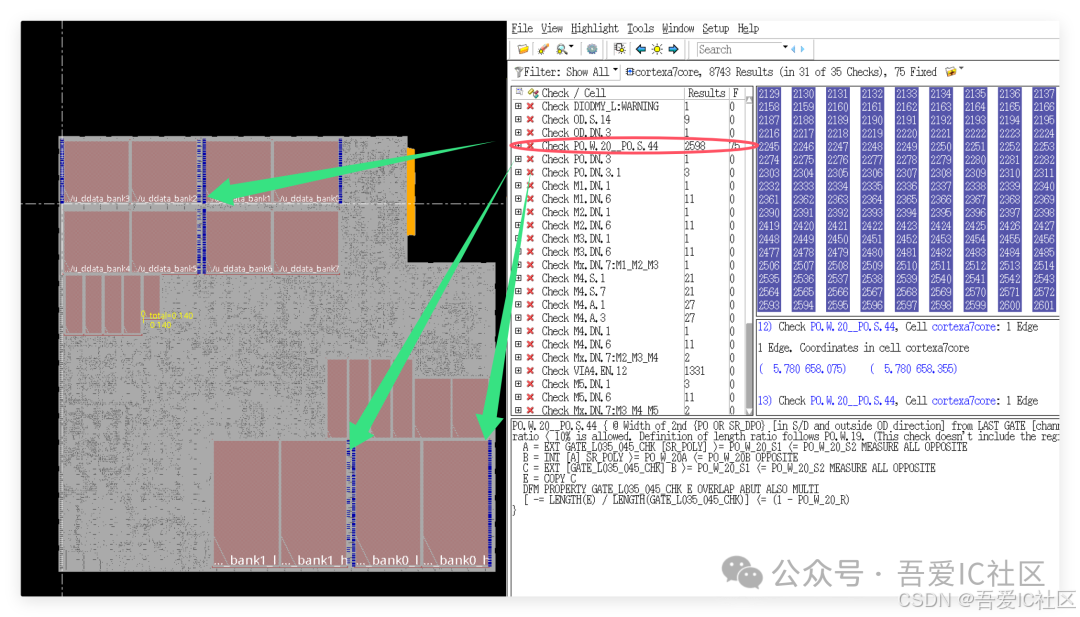

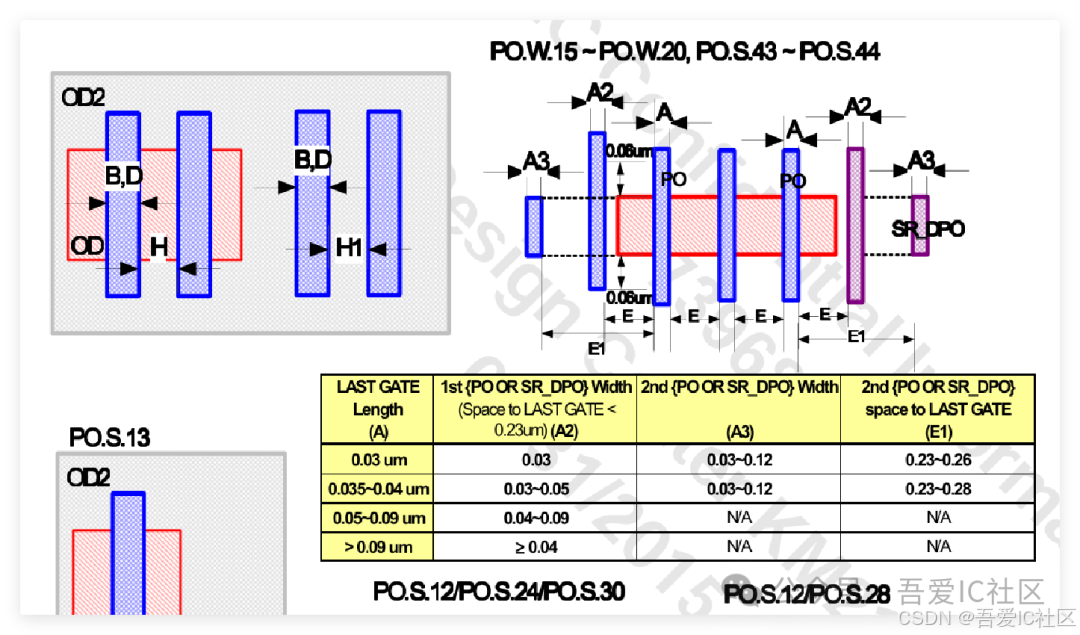

1)PO.W.20_PO.S.44

这类DRC Violation是属于base layer drc。一般是由于cell摆放有问题,或者filler插得有问题,又或者endcap cell(boundary cell)类型有问题。

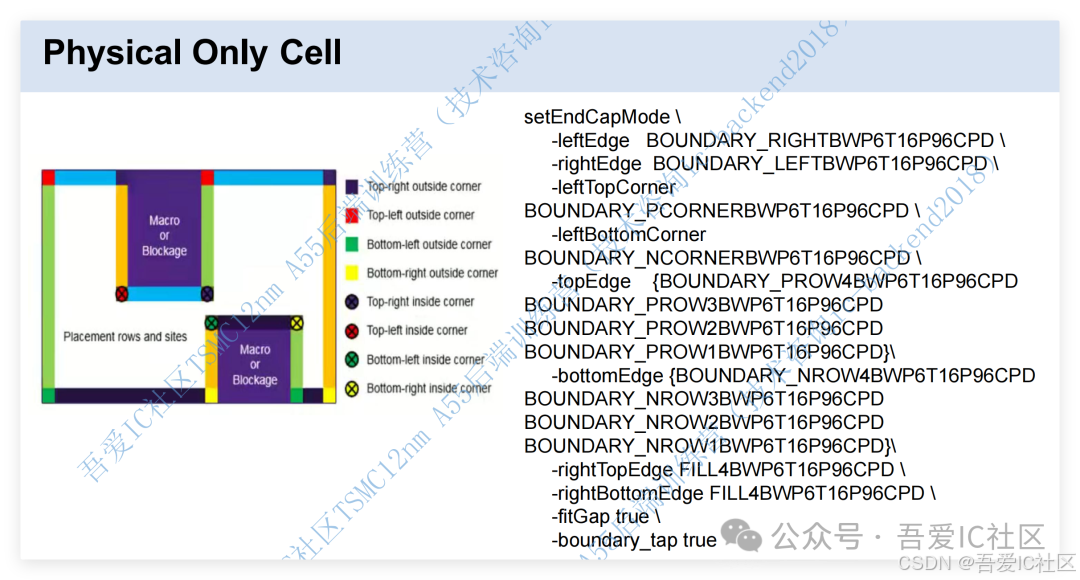

在咱们社区T12nm低功耗A55训练营项目中,各个corner的endcap类型都是不一样的。如果使用错了就会报出base layer drc violation。

遇到这类DRC Violation,一般需要借助foundary提供的design manual来debug找出问题。

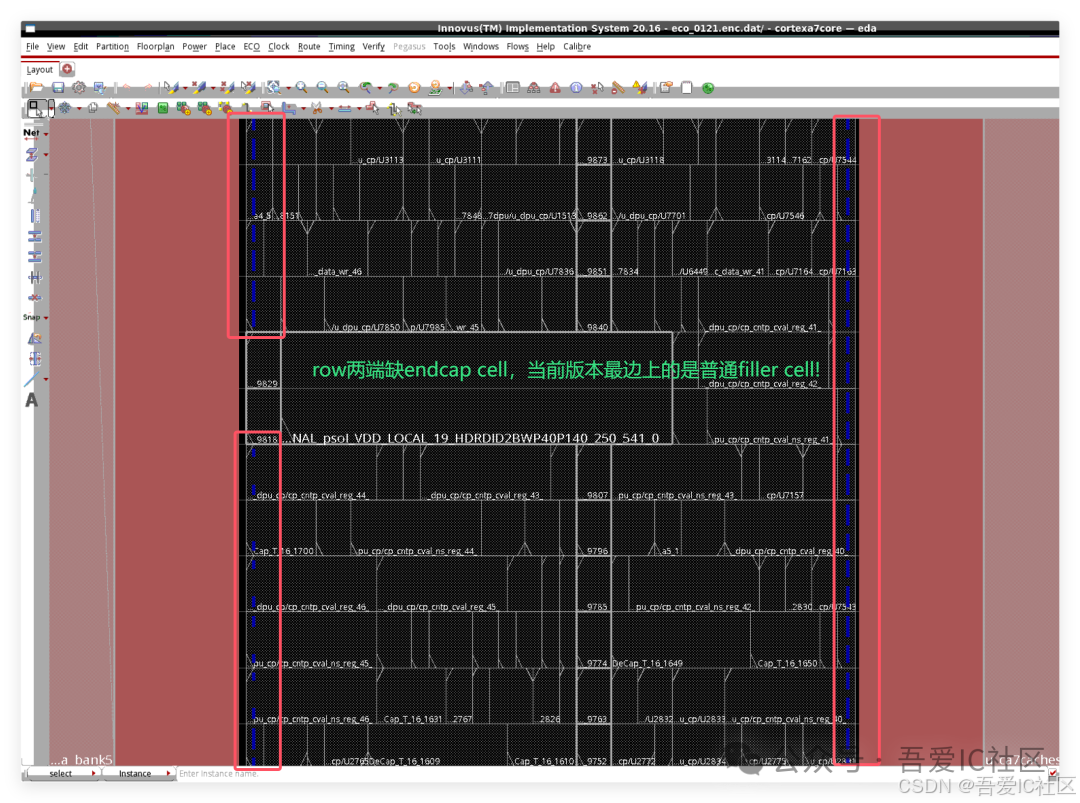

高亮后可以发现当前设计之所以出现这类violation是因为row两端没有插endcap cell!个别点是插了endcap cell,但是endcap左侧或右侧又插了filler cell(等效于row两端是加了普通filler)!

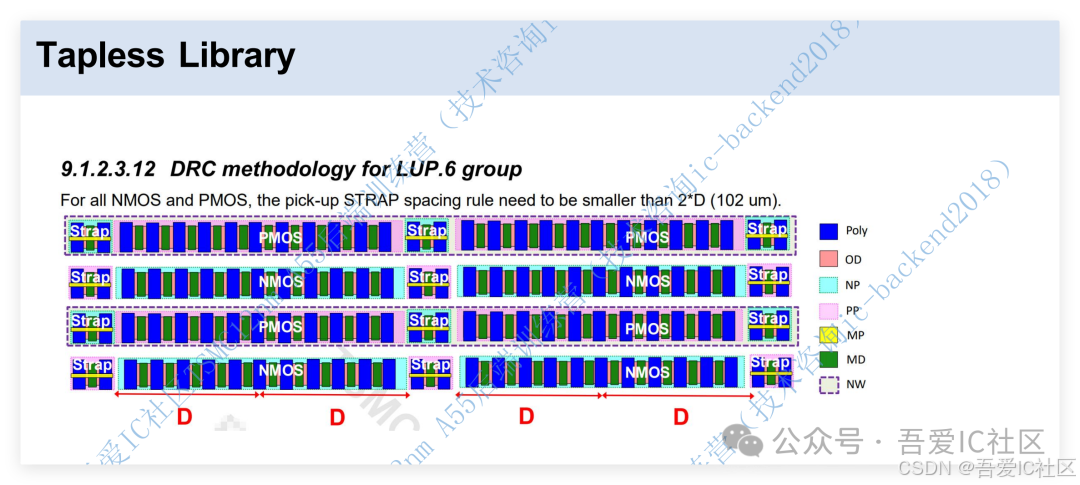

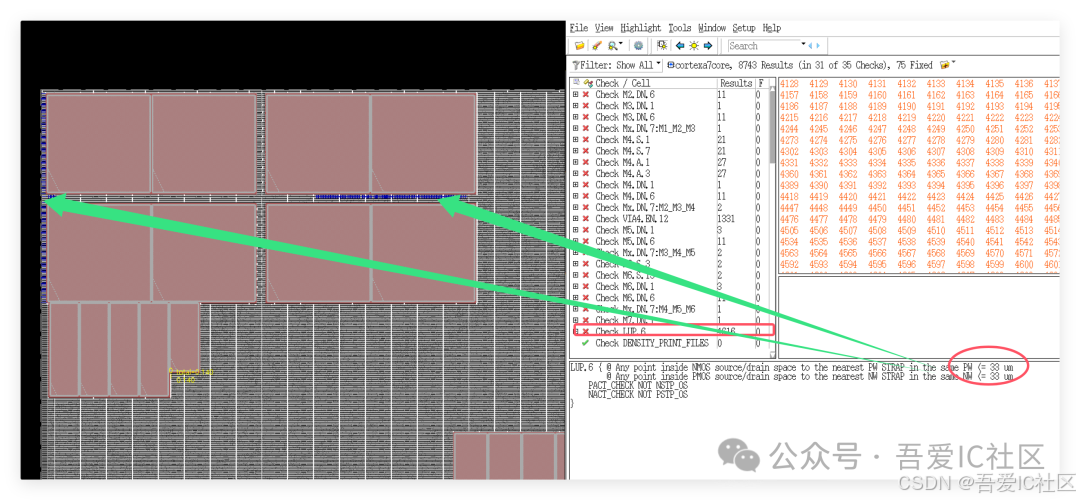

2)LUP.6

TSMC工艺LUP.6 Violation我们在讲tapless标准单元库就反复强调我们拿到一个新工艺一定要去查看design manual中LUP.6这个规则的图解。

这条规则告诉用户tapcell应该按照多少距离来摆放。如果间距过大就会导致某些标准单元找不到well接触(nwell连接到VDD,psub连接到VSS)!

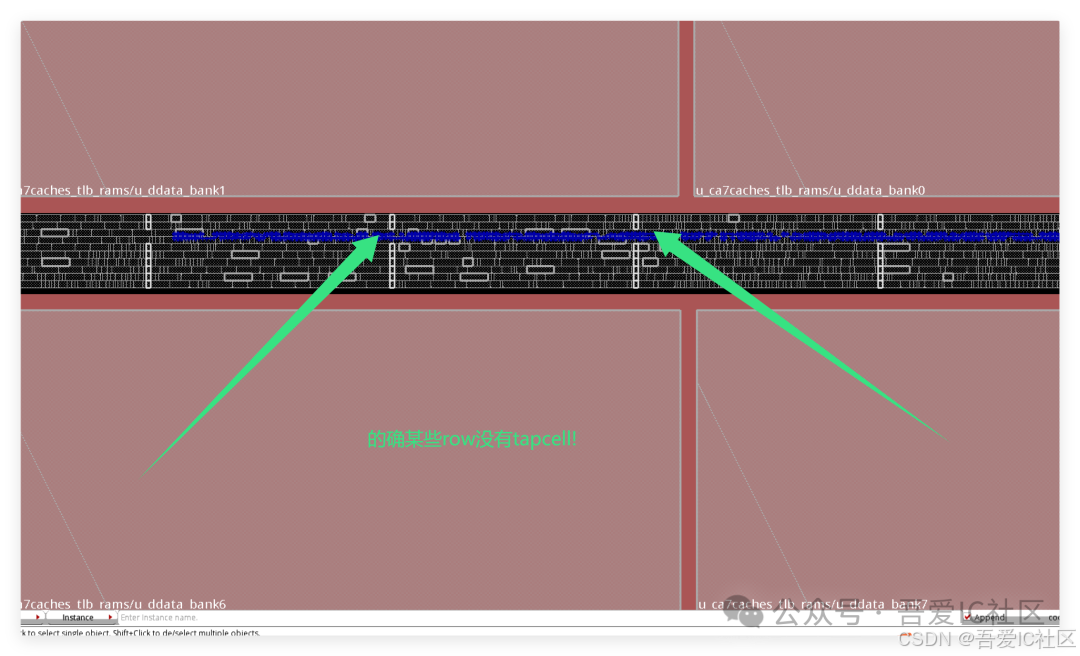

通过高亮这类tapcell和高亮这类LUP.6 DRC Violation,我们发现在最左边纵向channel和横向的一个channel缺少了tap cell!

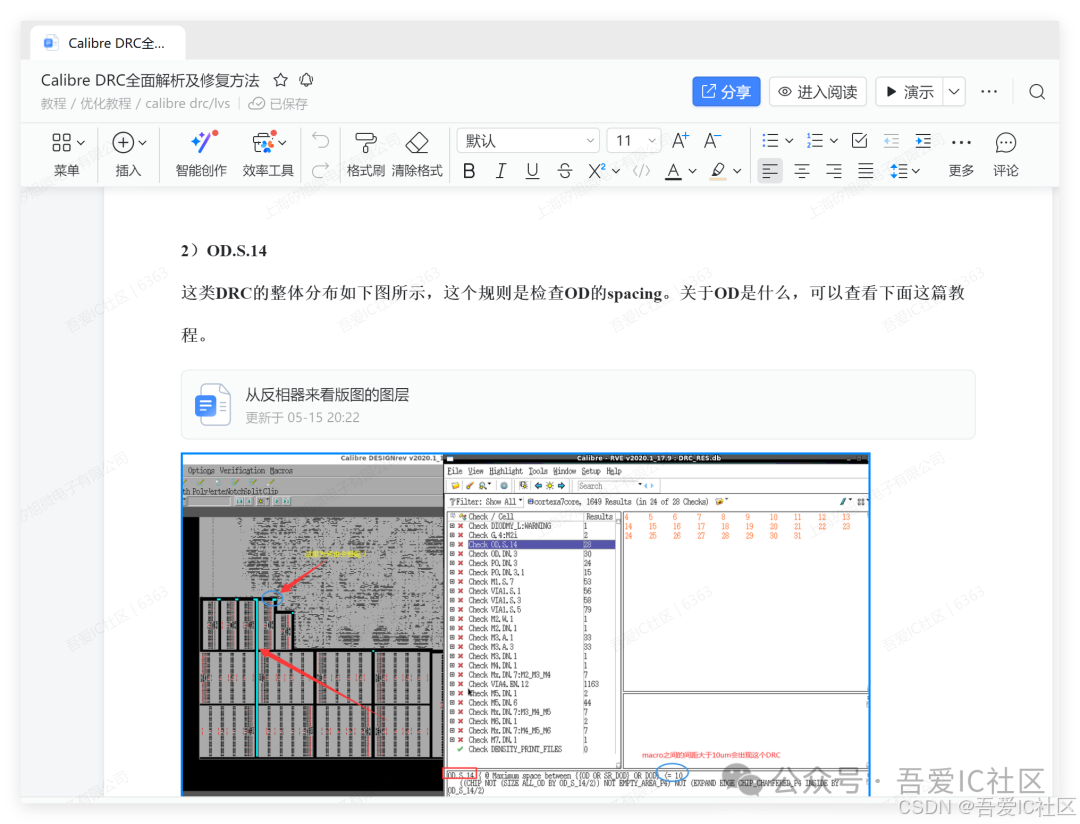

3)OD.S.14

4)M4.*

M4相关的DRC Violation跟之前Innovus分析得到的结果类似。均出现在memory m3出pin附近!

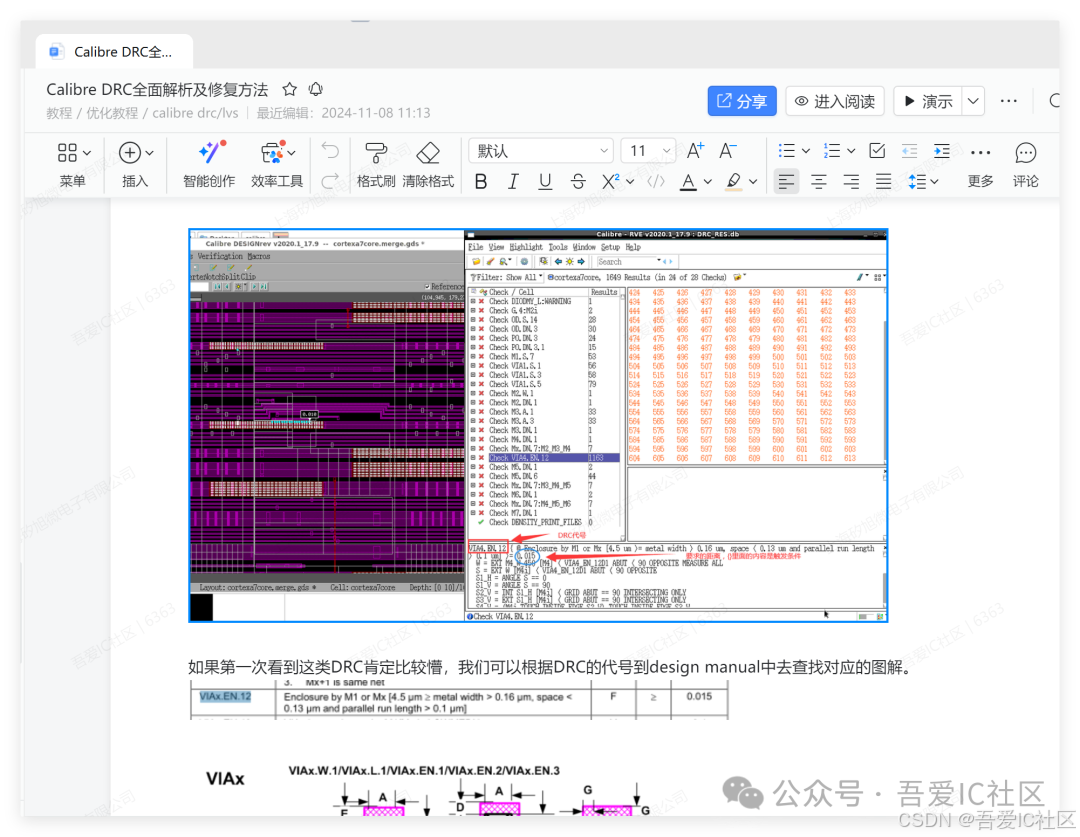

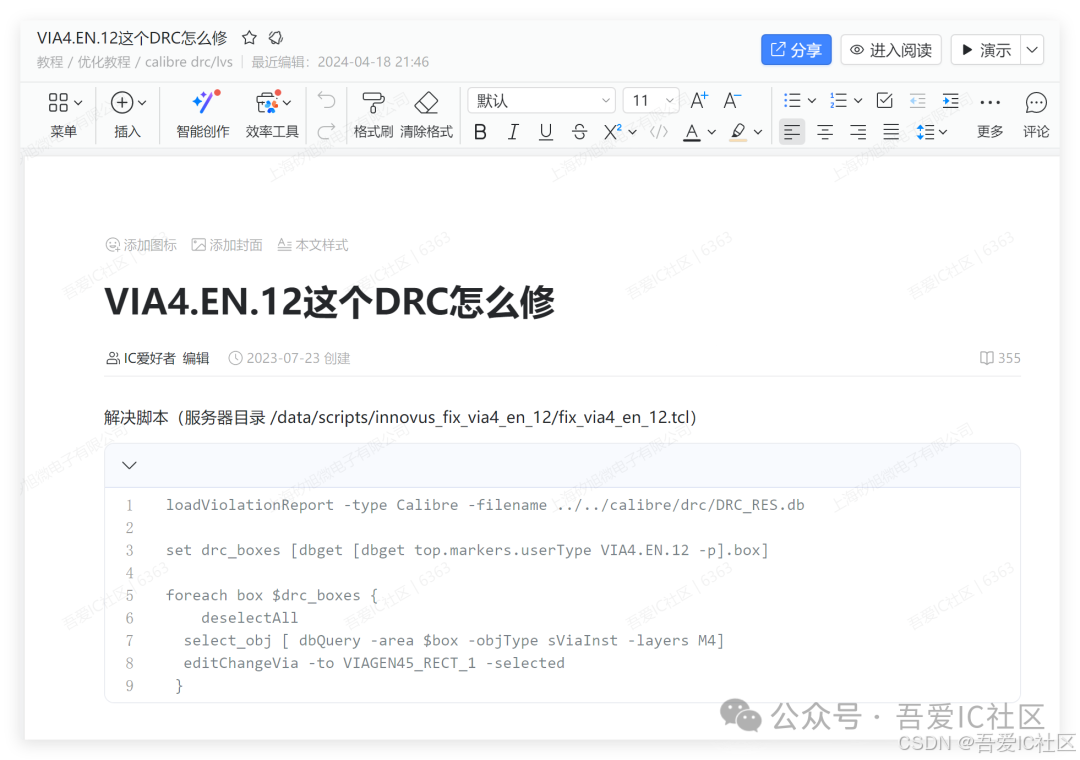

5)VIA4.EN.12

1730

1730

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?