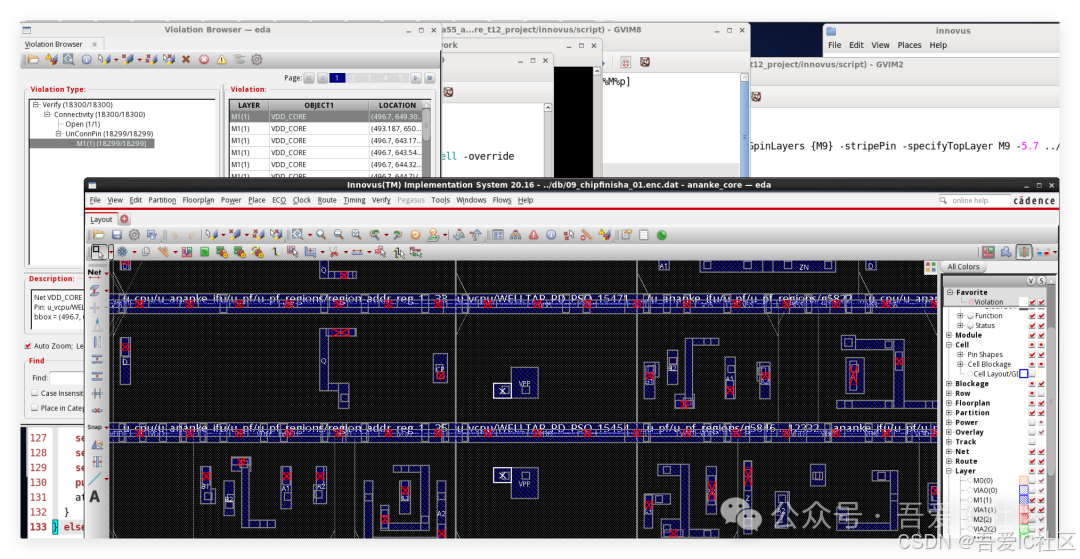

Q1:为了更高效过掉Calibre LVS,我们要求学员在chipfinish阶段需要先做Online LVS检查。该学员在做verifyConnectivity检查发现设计中存在大量的M1 VDD_CORE Un-Connect Pin的violation,具体violation如下图所示。

根据Violation Browser可以很容易定位到这些violation都是出现在我们A55项目Tapcell上的M1 VPP Pin(Secondary PG Pin),而且的确这个M1 Pin没有和VDD_CORE有物理通路(缺VIA1)。

而我们项目的Secondary PG Pin走线是在powerplan阶段就做好的,为何这里会缺VIA1呢?

经过debug发现,powerplan.enc.dat中的确也有VIA1。但这个学员听咱们直播课一直强调powerplan做完后一定要做PG Connectivity检查并写GDS到Calibre 进行DRC检查这件事情,于是就开始插filler和添加dual power rail M1和M2之间的VIA1。

这个行为本身也没有问题,而且这个学员也记得这个加过dual power rail VIA1的项目数据仅仅是拿来验证PG连接性检查,但他在想不就一个VIA1嘛,我可以通过命令来批量删除。删除后仍然可以继续使用这个database来接着做后续其他流程。

set box [dbGet top.fPlan.box]

set via1_list [dbQuery -layers 1 -objType sViaInst -areas $box]

dbDeleteObj $via1_list

但他没想到的是设计中除了power rail上存在 special net VIA1,Tapcell的Secondary Pin也有VIA1,而且也是special route的类型。

routePGPinUseSignalRoute -nets VDD_CORE -pattern trunk -maxFanout 8 -nonDefaultRule vddl_rule}

setAttribute -net VDD_CORE -skip_Routing trueconvertNetToSNet -net VDD_CORE

</

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?