本次笔记内容:

P9 计算机组成原理(09)

P10 计算机组成原理(10)

本节课对应幻灯片:组成原理15 AM2901,第1页起。

前面把运算器的功能讲过了,接下来讲如何应用这些功能?

我们讲以一个具体的运算器芯片为例 AM2901 。

首先是复习前面讲过的内容,并且介绍一点概述知识,包括:

硬件系统的功能部件(五大部件)

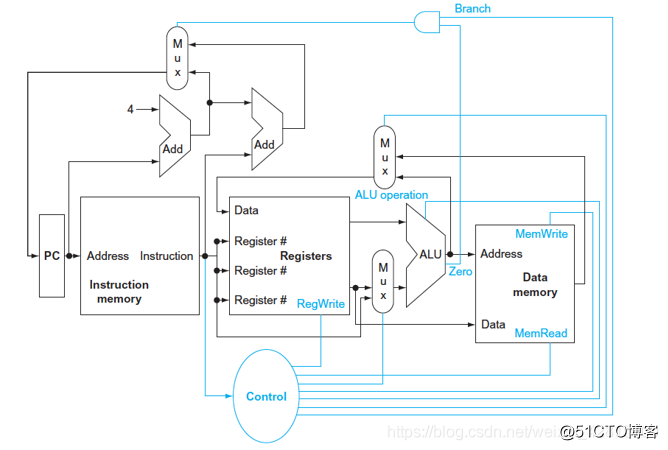

CPU示例

P4 CPU示例

上述一个CPU中:

CPU由运算器(核心是寄存器和ALU)和控制器组成;

运算器的数据通路包括图中下部;

上面的一部分,从PC开始,属于控制器。

数据通路包括:指令从哪来(有可能来自于存储器,存放在内存当中);指令存储器要有一个寄存器(这个指令在哪);PC就是存储指令的地址的东西;

控制器得到指令,根据操作码,得出“完成什么指令”,然后控制数据通路中剩下的部分完成工作;

所以最重要的是操作码与源操作数。把这些东西给操作部件,结果有可能送回寄存器组,也可能送到数据通路中。

P5 运算器的基本功能

运算器是计算机系统中执行数据运算、处理的功能部件,类似于一个工厂中的生产加工车间, 由ALU和寄存器组等组成。

类似工厂流水线,寄存器相当于小仓库、小车间。

完成算术、逻辑运算,产生运算结果:ALU执行+、—、× 、÷、∧、∨、¬

并给出运算结果的状态信息:C,Z,V,S

暂存运算所用操作数:寄存器组、立即数、数据总线

暂存运算的中间结果:寄存器组、Q寄存器、移位线路

输出运算结果:寄存器组、数据总线运算器的首要功能是完成对数据的算术和逻辑运算,由其内部的一个被称之为算术与逻辑运算部件(英文缩写为ALU)承担,它在给出运算结果的同时, 还给出结果的某些特征,如溢出否,有无进位,结果是否为零、为负等,这些结果特征信息通常被保存在几个特定的触发器中。要保证 ALU 正常运行,必须向它指明应该执行的某种运算功能。

运算器的第二项功能,是暂存将参加运算的数据和中间结果,由其内部的一组寄存器承担。因为这些寄存器可以被汇编程序员直接访问与使用, 故通称通用寄存器,以区别于那些计算机内部设置的、不能为汇编程序员访问的专用寄存器。为了向 ALU提供正确的数据来源,必须指明使用通用寄存器组中的哪1个或2个寄存器。

为了用硬件线路完成乘除指令运算, 运算器内一般还有一个能自行左右移位的专用寄存器,通称乘商寄存器。由于该寄存器属于内部专用,汇编程序员不能访问,许多计算机组成原理教材和技术资料中不大提及此线路。

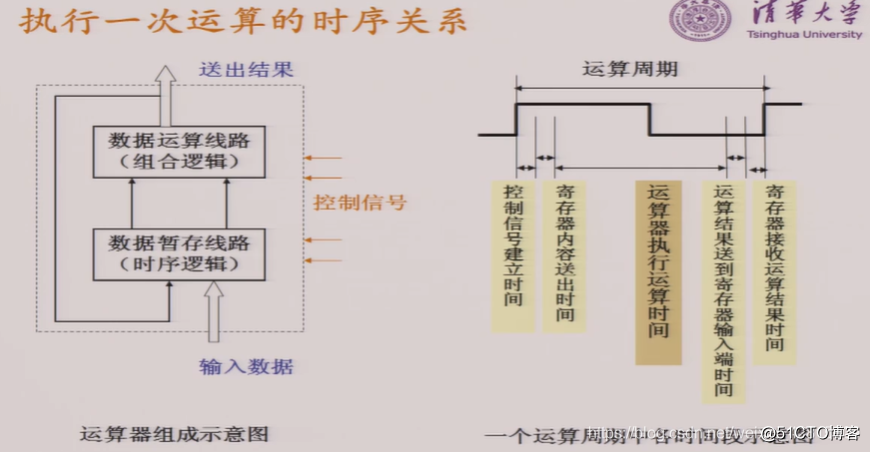

执行一次运算的时序关系

组合逻辑和时序逻辑区别:

输出是否与当前输入关联(时序逻辑有时钟)。

要考虑时间:

控制器的延迟要考虑;

控制信号会送给寄存器组,寄存器内容送出时间(延迟)需要考虑;

ALU运算时间;

运算结果送出需要时间。

因此,如何设定一个周期?如何设置主频?是值得我们思考的地方。

P13 两种运算器

运算器通常包括定点运算器和浮点运算器两种类型:

定点运算器:完成对整数类型数据的算术运算、逻辑类型数据的逻辑运算

浮点运算器:完成对浮点类型数据的算术运算

P17 定点运算器功能与组成

今天主要介绍定点运算器。

通过几组多路选择器电路实现相互连接,以便数据传送:

完成算术与逻辑运算功能:算术逻辑单元(ALU)

暂存参加运算的数据和中间结果:通用寄存器组

乘除法运算的硬件线路支持 乘商寄存器(Q寄存器)

作为处理机内部数据通路(Data Path)的一部分。

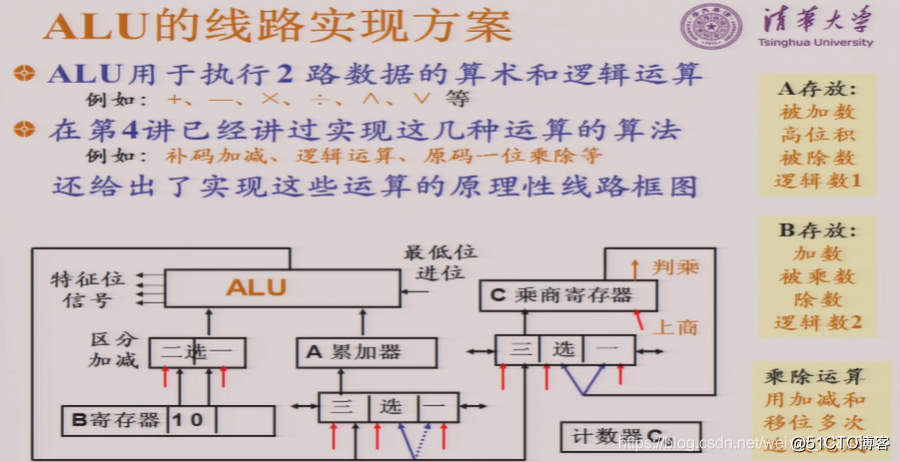

ALU的线路实现方案

由上节课内容为基础,可设计出上述 ALU 的线路。

P6-10 具体如何设计1位ALU电路

是对上节课的一个复习,具体见 P6-11。

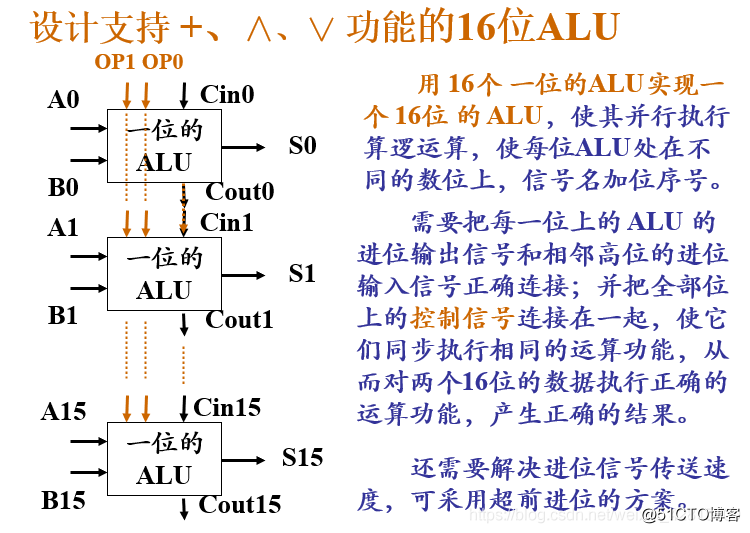

P11 设计实现16位ALU

单纯的连接可能会造成性能的损失(上节课所说),可以使用上节课所说的“超前进位”来提升。

Am2901

尽管现在已经比较少见,但是AM2901是一个很成功、很广泛的商用计算器。

这节课介绍一下这款经典的芯片。

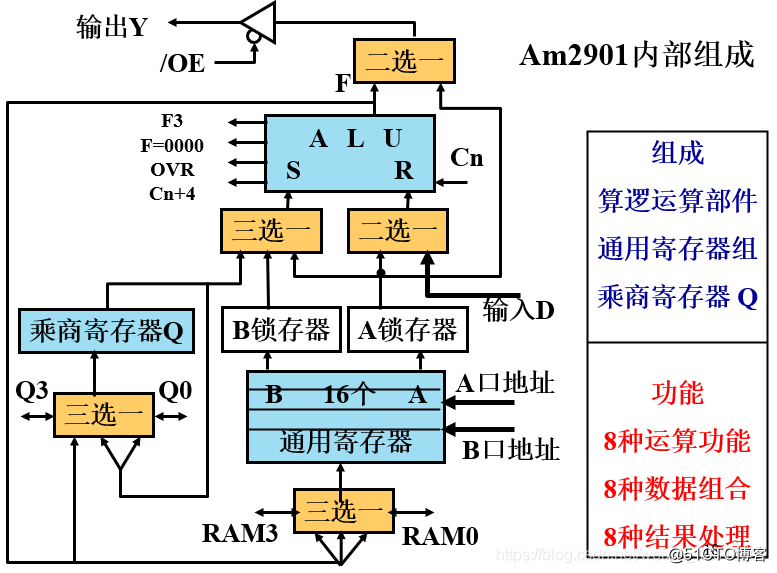

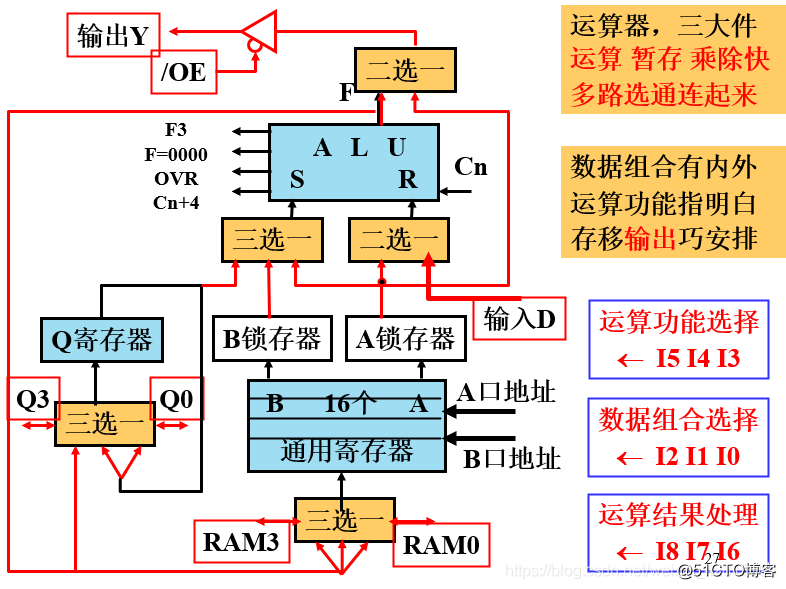

Am2901 的内部组成

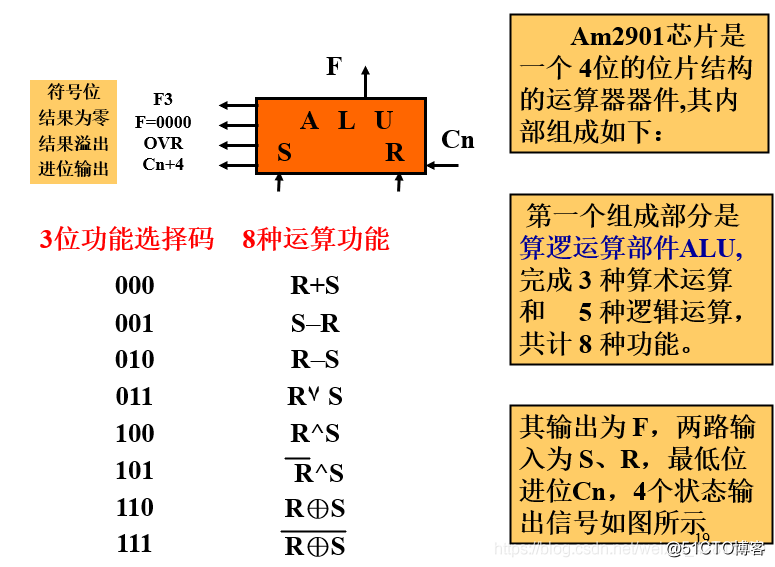

哪8种运算功能?算逻运算部件ALU

一种加法,两种减法,五种逻辑运算。

实现的功能很少,剩下的运算组合都交给软件了。

“该芯片的第一个组成成分是一个4位的算逻运算部件ALU,它的输出为F,两路输入分别用R和S标记,还有送入ALU最低位的进位信号Cn。它能实现R+S、S-R、R-S三种算术运算功能,和R∨S、R∧S、R∧S、R ∨S、R ∨S五种逻辑运算功能。在给出运算结果的同时,还送出向高位的进位输出信号Cn+4,溢出标志信号OVR,最高位的状态信号F3(可能用作符号位),以及运算结果为零的标志信号F=0000。”

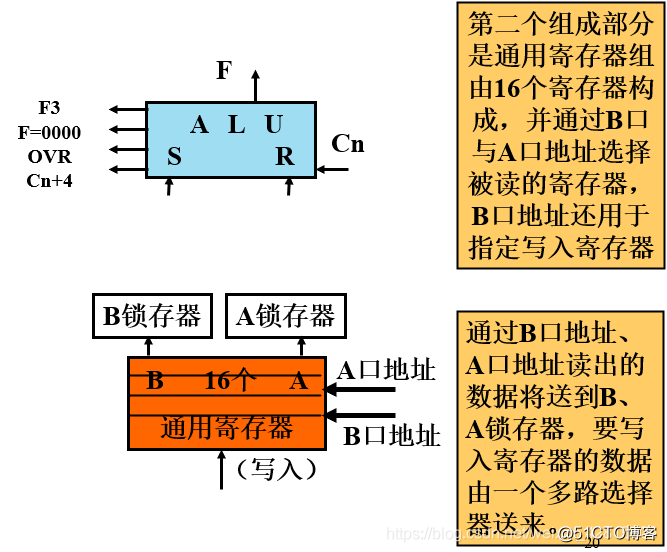

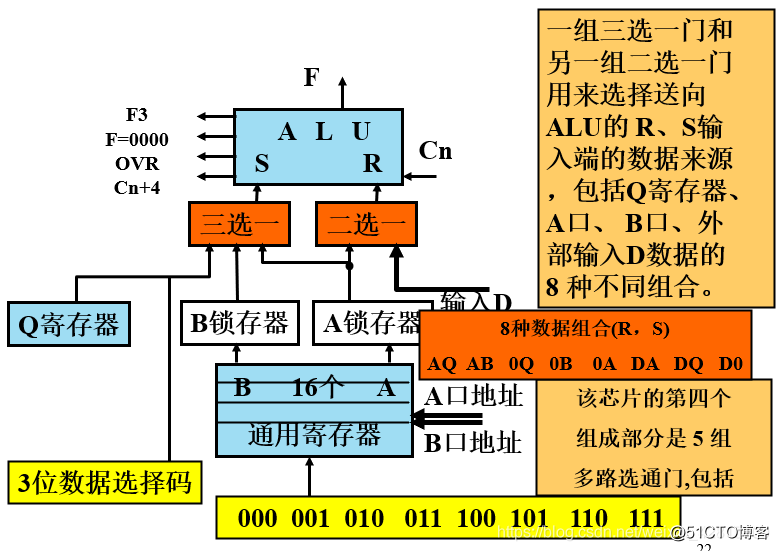

寄存器组

“该芯片的第二个组成成分是由16个4位的通用寄存器组成的寄存器组。它是一个用双端口(A口和B口)控制读出,单端口(B口)控制写入的部件。为了对其进行读写,需通过A地址(寄存器编号)、B地址(寄存器编号)指定被读写的寄存器。两路读出数据分辨用A口、B口标记,经锁存器线路可以送到ALU的R、S输入端的多路选择器,A口读出数据还可以用作该芯片的可选输出数据之一。寄存器组的写入数据由一组多路选择器给出,并由B地址选择写入的寄存器。 ”

为什么没有控制信号控制何时读写?

因为在一个周期里面,何时读,何时写都是固定的。

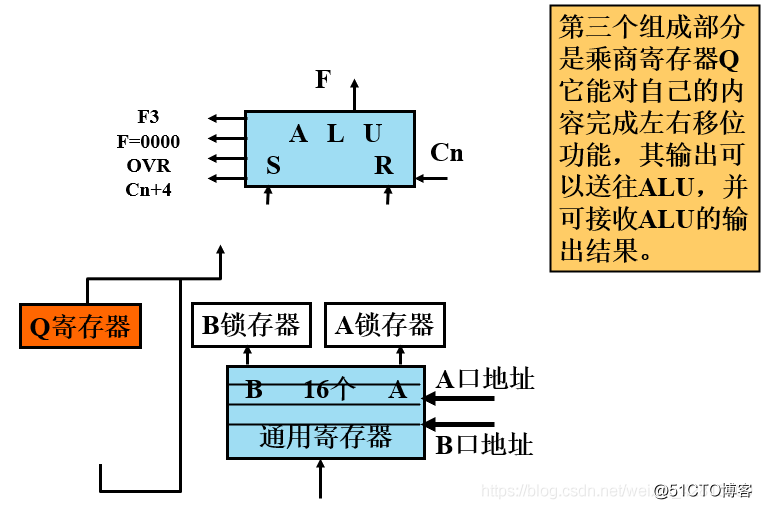

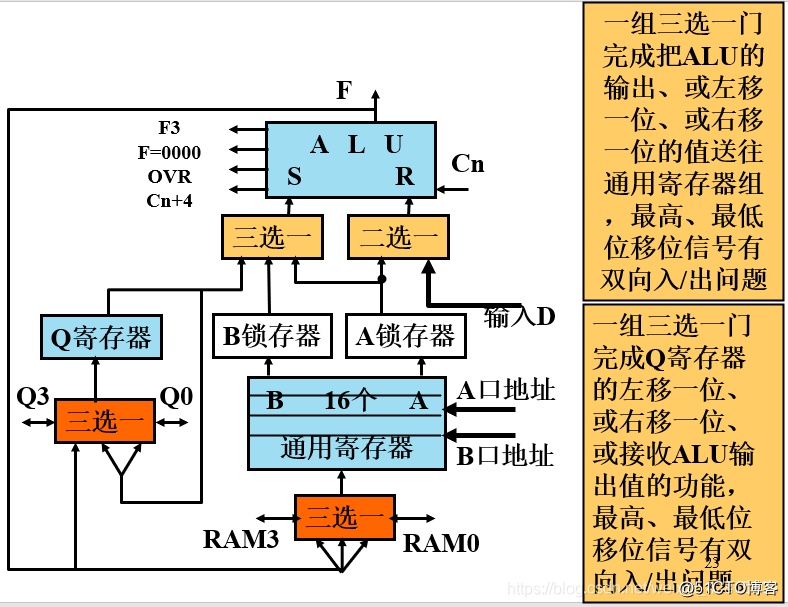

Q寄存器

“该芯片的第三个组成成分是一个4位的Q寄存器,主要用于实现硬件的乘法、除法指令,能对本身的内容完成左、右移位功能,能接收ALU的输出,输出送到ALU的S输入端。 ”

总线把上述三个核心部分连接

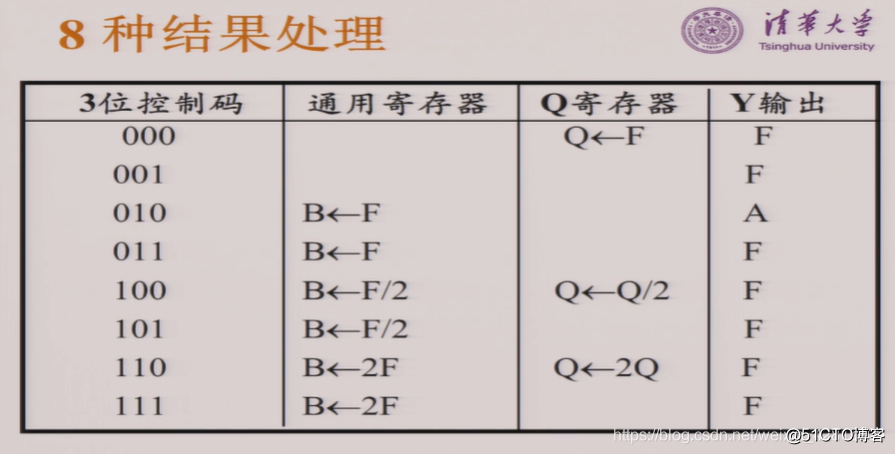

如上,有3位数据控制码。

其总的结构如下。两个三选一完成两个寄存器的控制。

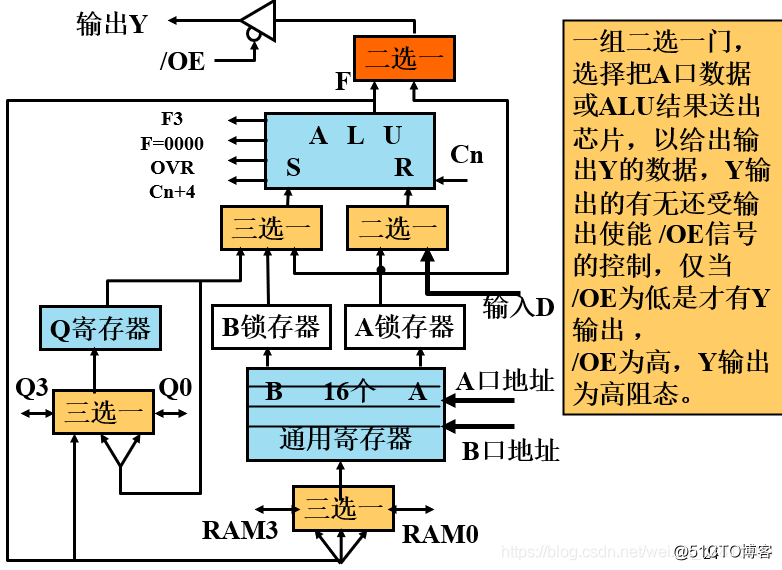

如下,一个二选一完成输出输出数据的控制。

运算器组成部分顺口溜

可以看出,三种功能都是通过三位控制码完成的,共9位控制码。

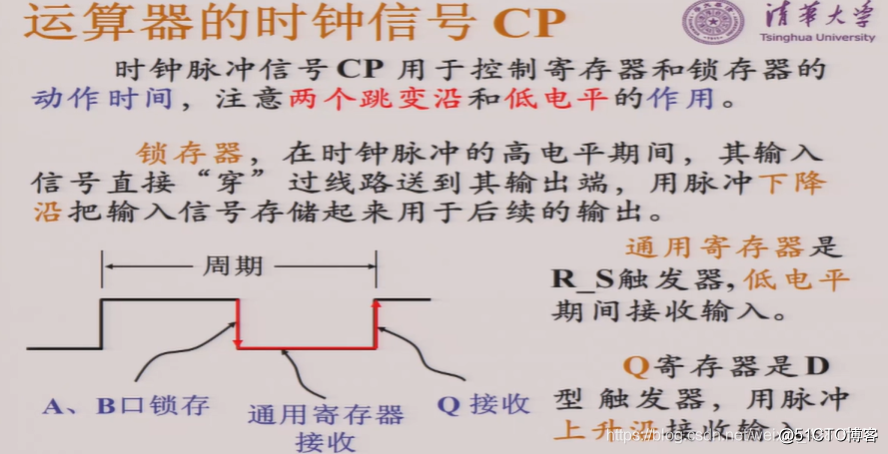

运算器的时钟信号CP

其始终与周期设计如上。各个固定任务始终遵循固定的周期与顺序。

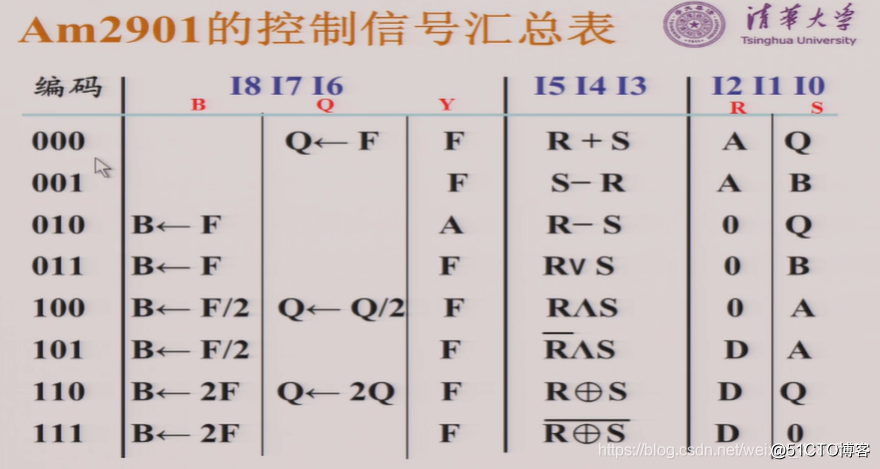

Am2901的控制信号汇总表

对于设计人员,这个表会在实践中烂熟于心。

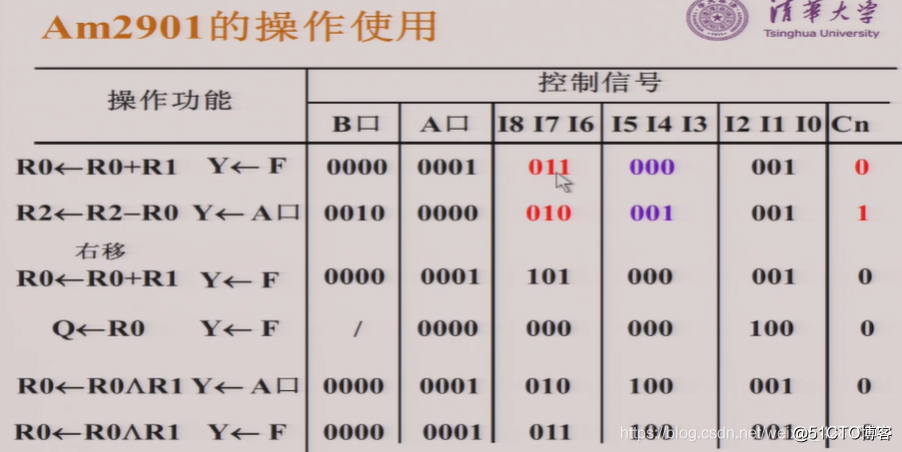

Am2901的操作使用

比如第一行:

可能对应汇编语言 ADD R0 R1 ;

其完成加法功能,根据控制信号汇总表,I5 I4 I3应该选择000;

数据来源于 A 和 B,根据控制信号汇总表,I2 I1 I0应该选择001;

如何知道 R1 和 R0 是 A 和 B 的?因为计算结果要写回到 R0 ,因此B口只能是R0,是0000,A口是对应R1 0001;

F要送回到 B 口去,不做移位,因此输出无所谓,根据控制信号汇总表,I8 I7 I6选择010和011都可以。

把这18位交给Am2901,其就会得到一个完整的任务描述,完成任务。

VHDL 硬件描述语言

VHDL具有强大的语言结构

系统硬件描述能力强、设计效率高

具有较高的抽象描述能力

可读性强,易于修改和发现错误公

移植性好

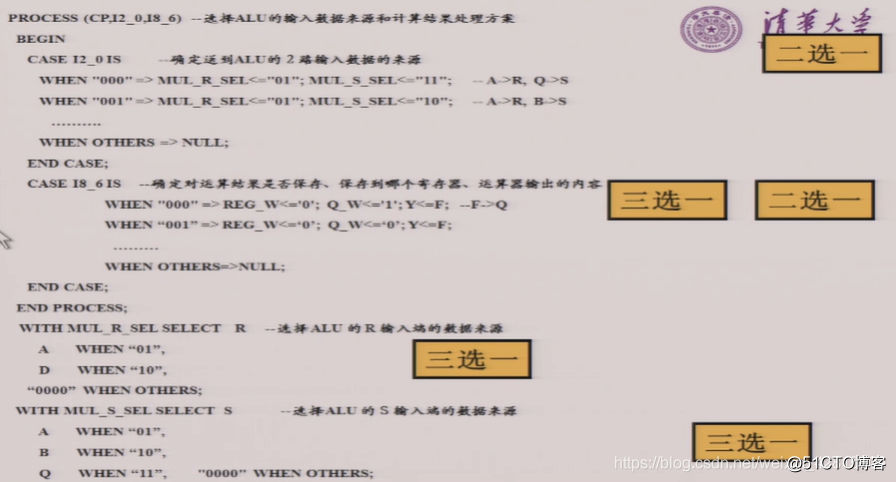

用VHDL设计Am2901:

逻辑设计:功能分析

设计描述:自顶向下设计方法,划分模块(ALU、Register Files(读/写)、A和B锁存器)

模拟仿真

硬件调试

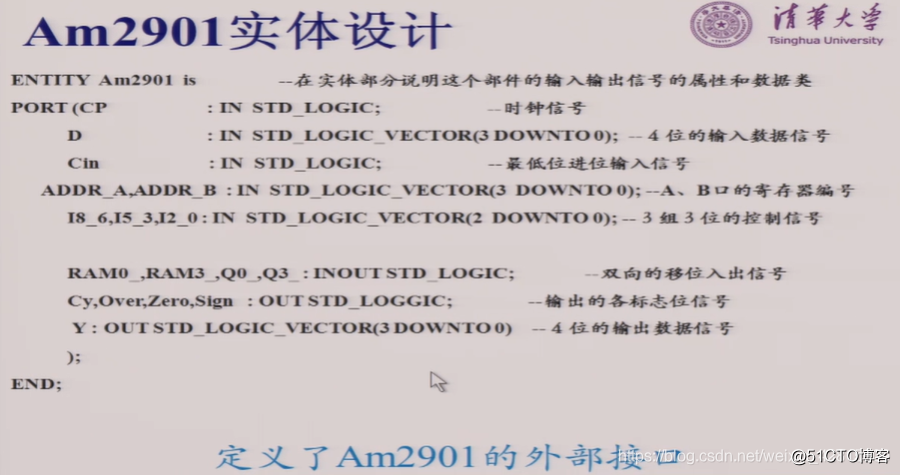

首先实体设计如下。

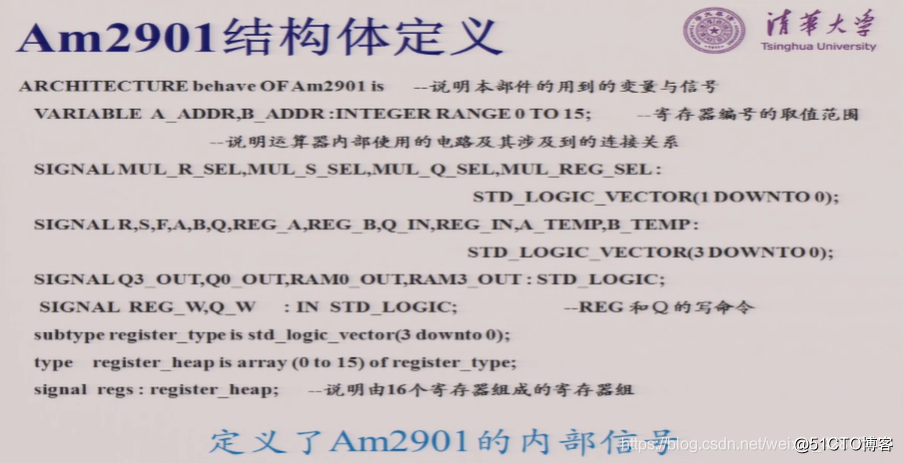

结构体定义如下。

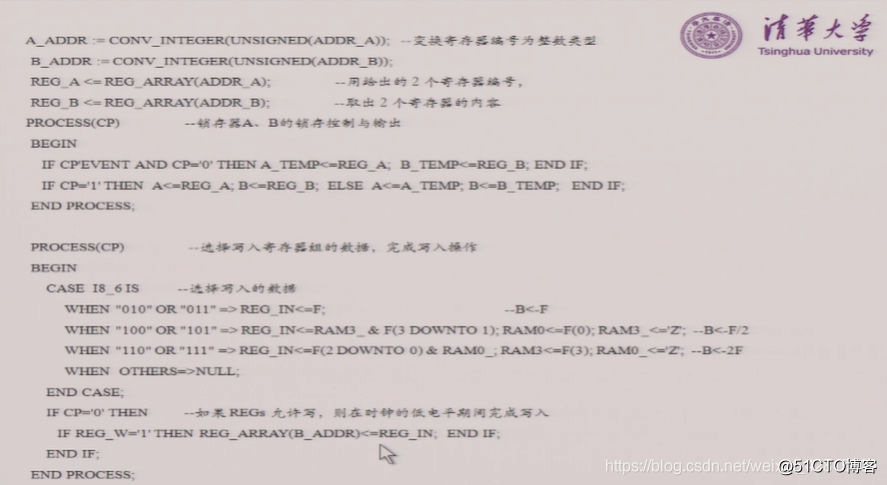

通用寄存器模块(A锁存器、B锁存器)如下。

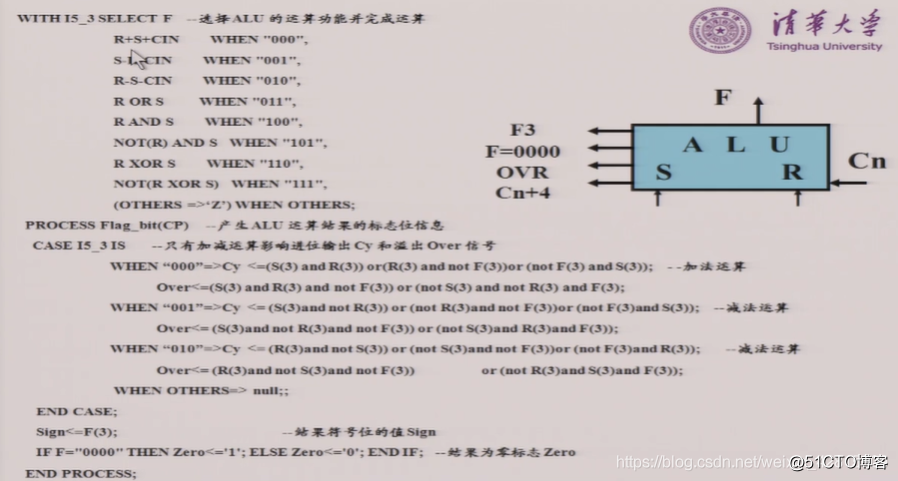

另外一个模块,ALU如下。

多路选通如下(只是举例,没有写完)。

小结

老的视频课程与2019的ppt有一点对不上,新的ppt没有讲VHDL。我截下的这些幻灯片比较有几年意义。

ppt中的这些内容,视频中没有涉及到(ppt的第35页起):

运算器最低位进位输入信号 Cin 的形成

运算器4位标志位信号的接收与记忆线路

移位时最高、最低位的移位输入信号设计

AM2901运算器详解

AM2901运算器详解

本文详细介绍了AM2901运算器的工作原理及其内部结构,包括算术逻辑单元(ALU)、通用寄存器组和乘商寄存器(Q寄存器)等关键部件。探讨了如何通过控制信号实现不同的算术和逻辑运算。

本文详细介绍了AM2901运算器的工作原理及其内部结构,包括算术逻辑单元(ALU)、通用寄存器组和乘商寄存器(Q寄存器)等关键部件。探讨了如何通过控制信号实现不同的算术和逻辑运算。

3586

3586

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?