1Hz ~~ 250MHz的感觉

做频率计,高频的,250M 左右没问题,再次测试,可是实验室没有20M以上的信号源给我用,怎么办办呢??

在嚎啕大哭的时候,难言,只能用FPGA产生频率给CPLD 来接收,250M没问题吧。

CLK_Deaign = Matlab_Keys + CLK_Generater;

在这个过程中发现了好多问题

(1) Matlab_Keys

(2) CLK_Generater: 两个PLL 不能同时由一个CLK供给时钟。

(3) 低频不能控制高频,否则没响应,就连选择器都有问题,因此 最好用最高时钟来控制

(4) Case语句可以这样写

case(Mode)

4'd0,4'd1,4'd2,4'd3,4'd4,4'd5,4'd6,4'd7,4'd8,4'd9,4'd10:

CLK_OUT = CLK_OUT_r;

。。。。。。。

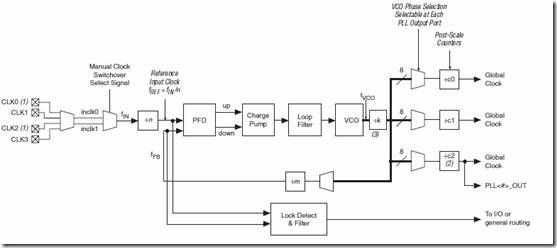

(5) PLL输出时钟,我选择性的输出,只能用组合逻辑,时序逻辑不行,没响应

always@(posedge CLOCK_50 or negedge RST_n)

begin

case(Mode)

4'd11: CLK_OUT <= CLK_50MHz;

4'd12: CLK_OUT <= CLK_100MHz;

4'd13: CLK_OUT <= CLK_150MHz;

4'd14: CLK_OUT <= CLK_200MHz;

4'd15: CLK_OUT <= CLK_250MHz;

default:CLK_OUT <= CLK_OUT;

endcase

end

这样是严重不行的,虽然只是简单的选择器,但是输出的时钟最低的50M和敏感时钟一样,另外的都比他高,造成无法控制

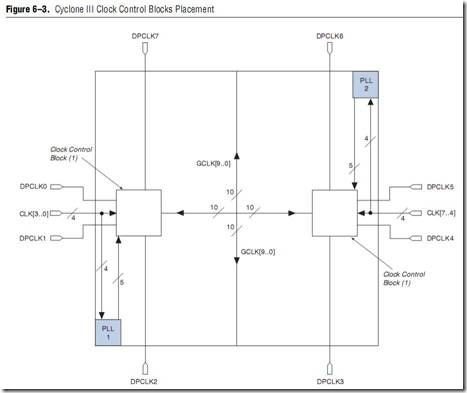

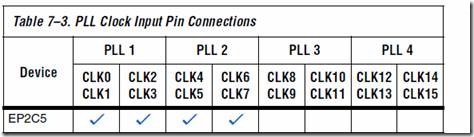

(6) 《深入浅出婉转FPGA》上有一章节说 FPGA全局时钟的事情,他说:

“Cyclone 系列旗舰基本都是2个PLL,除了EP1C3,Cyclone系列旗舰的全局时钟网络分配情况:PLL1只能由CLK0,CLK1供给,PLL2只能由CLK2,CLK3供给,否则,出错;PLL c0,c1只能作为内部时钟,e0只能最为外部时钟,否则出错”

我现在用的是CII 怎么可以输出呢???而且我用的是CLK0.CLK4,没问题

(7) 有一位高人告诉我,每个CLK都能作为输入,而且都能输出的,我自己测试出来也是这样的,所以,暂时相信我自己。

/*生成CLK_OUT 1~250MHz*/

always@*

begin

case(Mode)

4'd0,4'd1,4'd2,4'd3,4'd4,4'd5,4'd6,4'd7,4'd8,4'd9,4'd10:

CLK_OUT = CLK_OUT_r;

4'd11: CLK_OUT = CLK_50MHz;

4'd12: CLK_OUT = CLK_100MHz;

4'd13: CLK_OUT = CLK_150MHz;

4'd14: CLK_OUT = CLK_200MHz;

4'd15: CLK_OUT = CLK_250MHz;

endcase

end

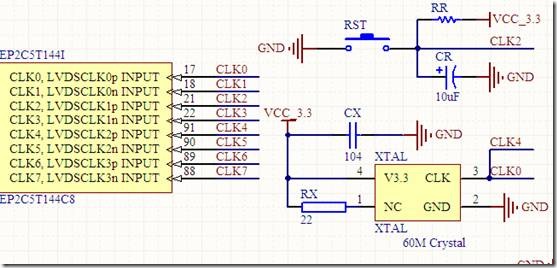

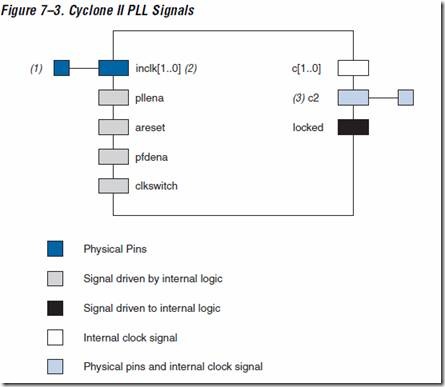

(8)  这是 CII 的DS上面的,意思貌似也是只能是CLK0,CLK1,CLK2,CLK3作为时钟输入,看起来好像是这样的,但是……

这是 CII 的DS上面的,意思貌似也是只能是CLK0,CLK1,CLK2,CLK3作为时钟输入,看起来好像是这样的,但是……

我PLL1 给的是CLK0, PLL2 给的是CLK4,我需要的效果都出来的,没出现问题啊!

(9) 完了 暂时就这么点想法了,到时候,在加。。

(10) 怪不得,我用的刚好是CLK0,CLK4,RP不错

好像pdf上是说,C0,C1内部时钟,c2外部时钟,但是我的工程用组合逻辑之后怎么都可以呢、??

http://blog.ednchina.com/wind330/198994/message.aspx

(12)未完待续

(13)

本文探讨了在FPGA设计中遇到的时钟信号生成问题,包括使用Matlab_Keys和CLK_Generater生成不同频率时钟信号的过程及遇到的问题。详细讨论了如何通过组合逻辑选择不同的时钟频率,并分享了一些关于全局时钟网络配置的经验。

本文探讨了在FPGA设计中遇到的时钟信号生成问题,包括使用Matlab_Keys和CLK_Generater生成不同频率时钟信号的过程及遇到的问题。详细讨论了如何通过组合逻辑选择不同的时钟频率,并分享了一些关于全局时钟网络配置的经验。

1854

1854

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?