1. 工艺模型的选择。以TSMC 180nm工艺为例,1.8V Normal devices 有TT,SS,FF,SF,FS共5种工艺Corner及Montel Carlo(MC)共6种可选用工艺角。在每种Corner中每种类型的管子又有两种类型,比如NMOS有nch和nch_mis两种,其中第nch是用MODEL定义的,而nch_mis是用SUBCKT定义的。做一般仿真(比如DC,AC,TRAN等)的时候,两个模型都可以使用。在做Montel Carlo仿真的时候如选用nch_mis器件,且corner选用TT,SS,FF,SF,FS,则只进行Devive-to-Device的mismatch分析,若corner选择MC,则可同时进行Die-to-Die和Devive-to-Device的分析)。在做Montel Carlo仿真的时候如选用nch、pch器件,且corner选用TT,SS,FF,SF,FS,实际上不能进行任何mismatch分析,因为此时器件的参数都不含分布函数,若corner选择MC,则可进行Die-to-Die的分析。具体进行什么分析,由下面一条中的设置决定。

2. Process,Mismatch和Process&Mismatch。Process仿真时在Analog Statistical Analysis中Analysis Variation可以有以上三种选项。选Process则Monte Carlo中每RUN一次的时候,Die to Die 的一些模型参数会重新随即选取,而Mismatch关联的一些参数保留相同,也就是说同一次RUN的电路中的相同类型的器件的所有参数将完全相同。反之,选Mismatch则每次RUN则只改变那些参数的值,而Die to Die相关的那些参数则完全相同。如果选择Process & Mismatch,则每次RUN的时候两种情况下的参数都重新取值。

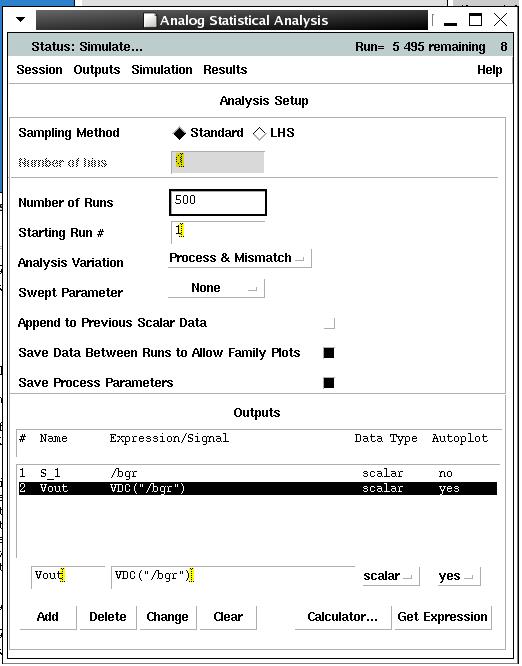

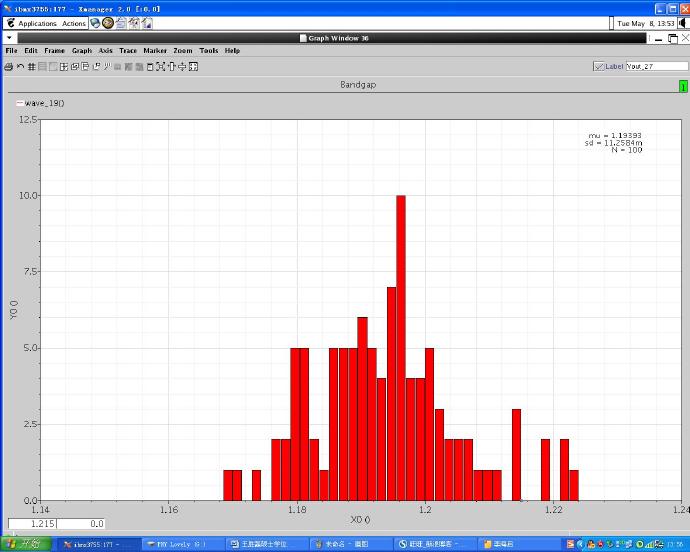

3.在对DC仿真进行Montel Carlo分析的时候会发现一些想要看的DC信息无法PLOT出来。比如在对放大器的失调电压进行仿真的时候需要用到上图所示Testbench,而在ADE中选择DC仿真,设置Save DC Operation Point而不做任何Sweep。一般在DC仿真时只要选择Vout就可将Vout信号Plot出来。但是如果接着进行Montel Carlo仿真会发现这样选择的信号(图1中/Vout)在Analog Statistical Analysis中Data Type显示为wave,无法Plot出来。这时候需要现在ADE中调用Calculator选择DC后选VDC(或Sweep_DC后选vs),再在Schematic中选中Vout信号,这样在Calculator中将是VDC("/VOUT") (或VS("/VOUT")),这样在之后进行Montel Carlo分析时,在Analog Statistical Analysis中Data Type显示为scalar,可以Plot出此信号的Histogram图出来。

4. Montel Carlo分析需要相应的带Montel Carlo参数的模型支持,如1所述。如果Analysis Variation选择了Process,而所用器件的模型中没有定义Die to Die的相关参数,则无法进行。另外不同EDA工具对高斯函数的格式定义有区别的。比如在Simetrix中就用GAUSS(tol)表示一个平均值(Mean)为1,标准偏差(Standard Deviation)为tol/3的高斯过程,也就是说公差(Tolerance)为tol的3 Sigma的高斯分布(3 Sigma Gaussian distribution)。而在Hspice中则有GAUSS(nominal_cal, rel_variation, num_sigma)和AGAUSS(nominal_cal, abs_variation, num_sigma)两个函数可用。Simetrix中的GAUSS(tol)=Hspice中的GAUSS(1,1*tol,3)=Hspice中的AGAUSS(1,tol,3)。

(原文地址:http://blog.sina.com.cn/s/blog_7affefaf01011kyd.html)

本文详细介绍了CMOS工艺模型的选择方法,包括TSMC180nm工艺下不同Corner的选择及其对MontelCarlo分析的影响。探讨了如何在不同仿真条件下进行Die-to-Die和Device-to-Device的mismatch分析,并解决了DC仿真中信号无法正确Plot的问题。

本文详细介绍了CMOS工艺模型的选择方法,包括TSMC180nm工艺下不同Corner的选择及其对MontelCarlo分析的影响。探讨了如何在不同仿真条件下进行Die-to-Die和Device-to-Device的mismatch分析,并解决了DC仿真中信号无法正确Plot的问题。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?