入门FPGA之vivado的使用

FPGA的设计流程

- 设计规划

- 波形绘制

- 代码编写

- 代码编译

- 逻辑仿真

- 波形对比

- 绑定管脚

- 分析综合/布局布线

- 上板验证

入门vivado

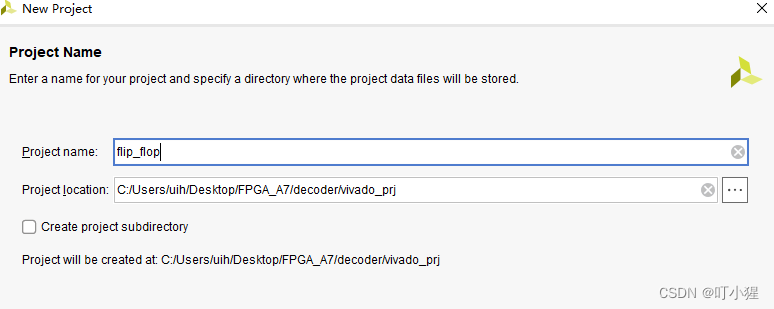

1. 创建工程的文件夹(工程:创建一个触发器电路)

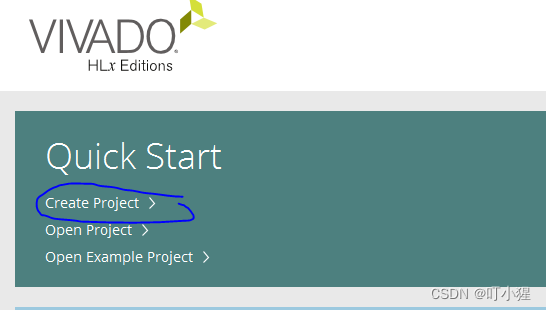

2. 打开vivado

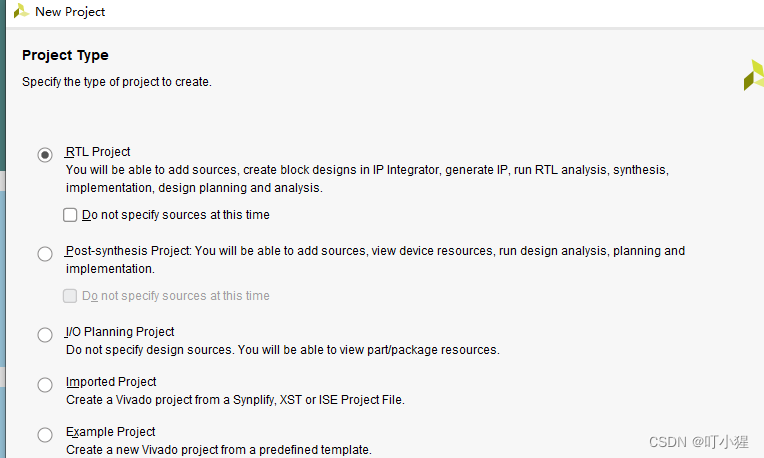

跳过添加源代码和约束文件的步骤

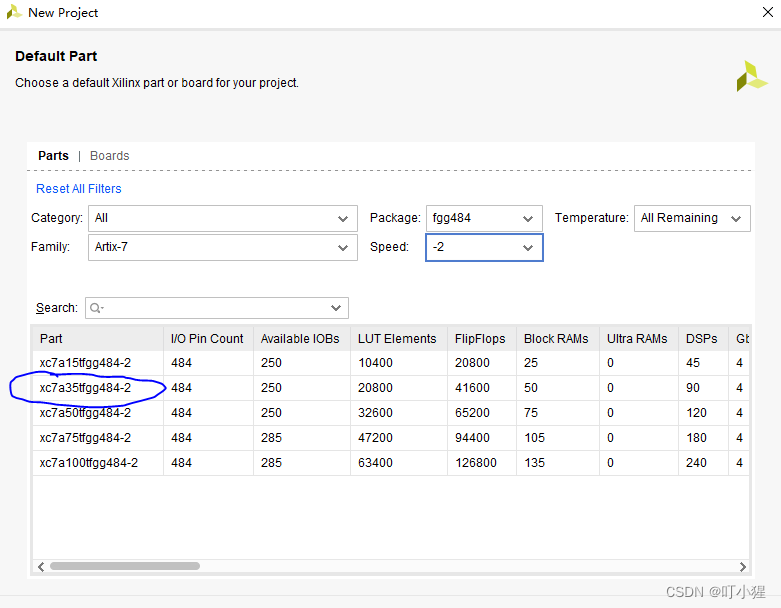

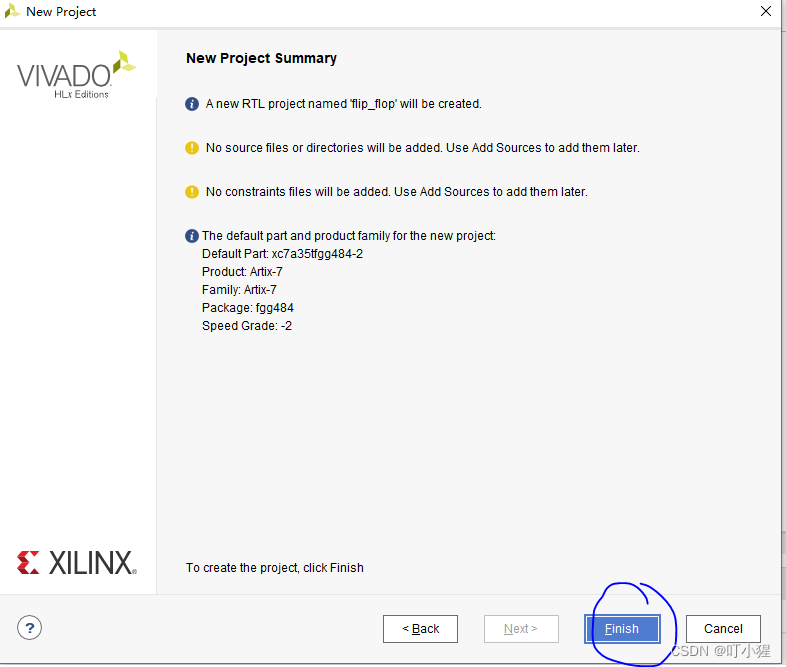

选择相应的芯片型号

检查无误后,点击Finish

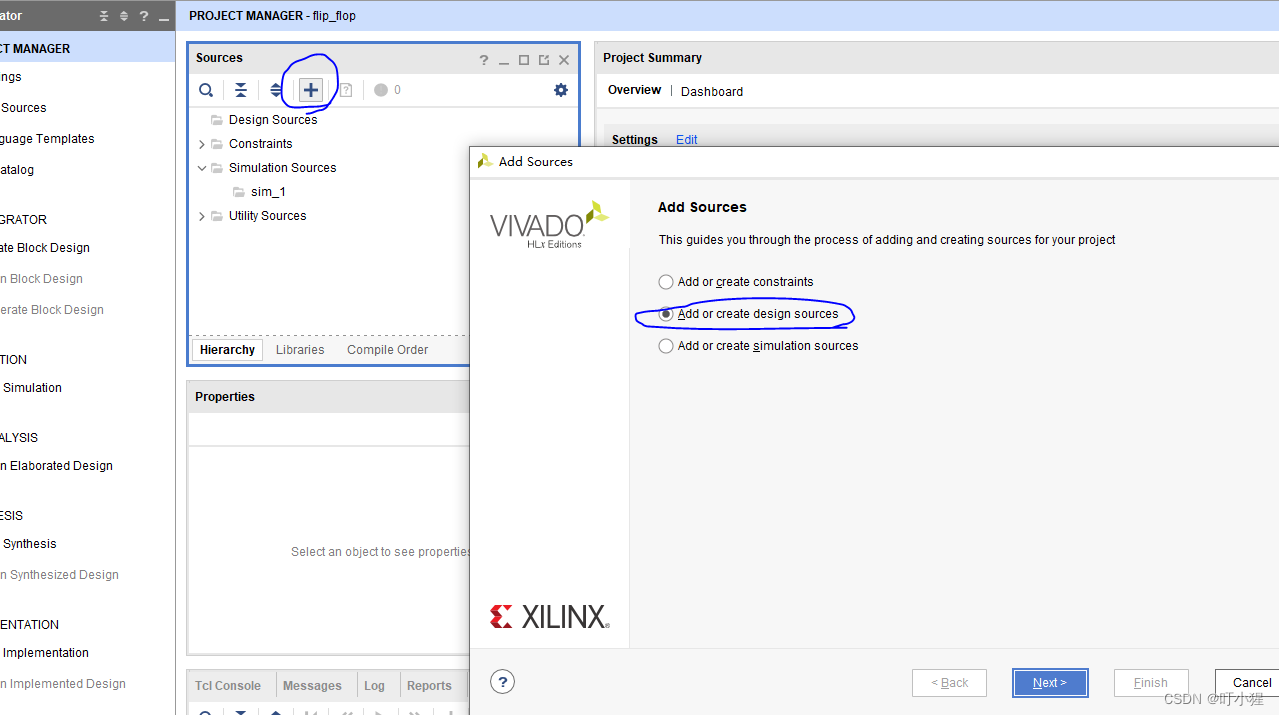

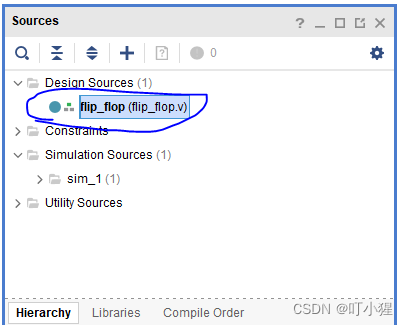

添加源文件,如下:

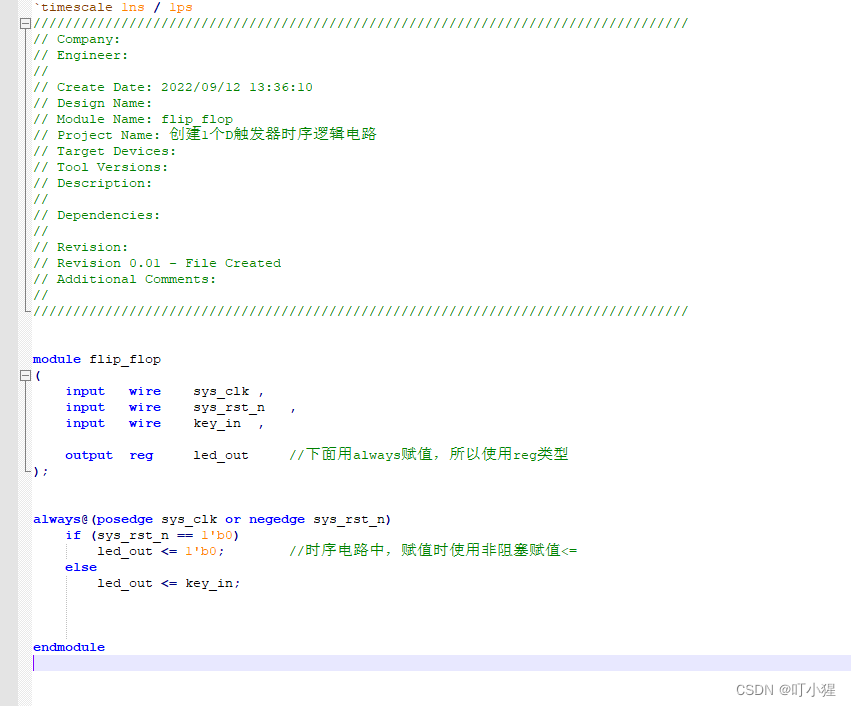

双击flip_flop.v文件开始编辑源代码(这里已经关联了notpad++编辑器)

编辑完源代码后点击保存

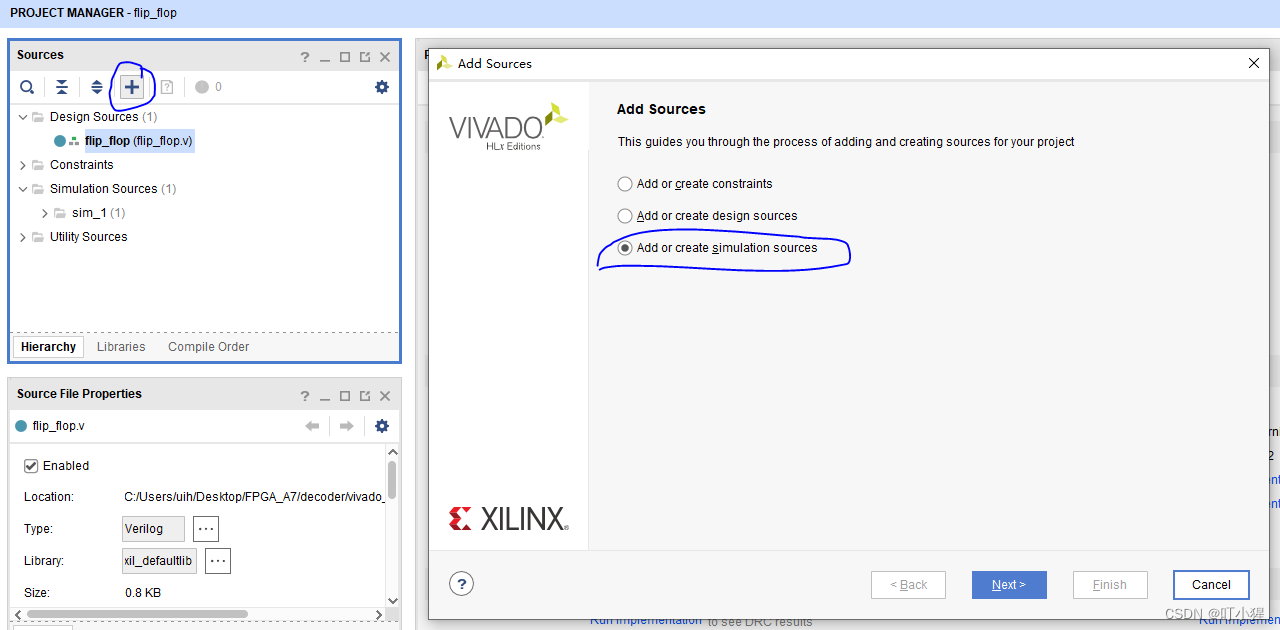

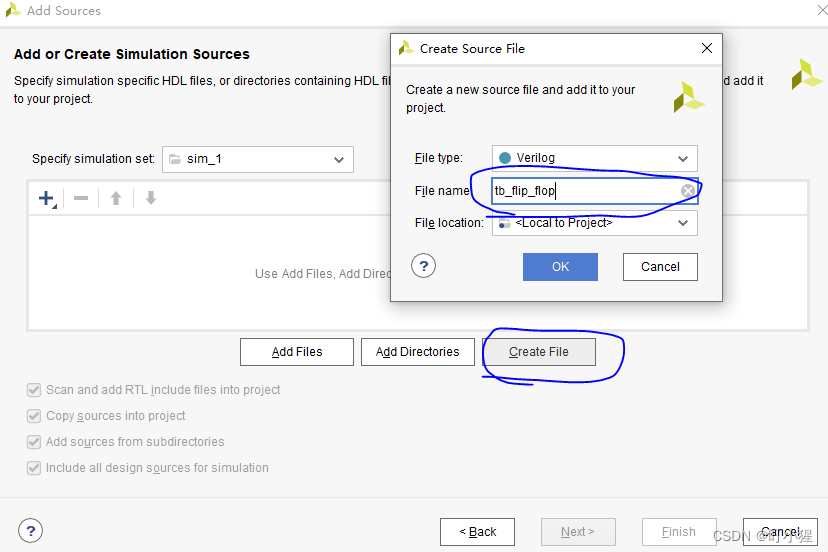

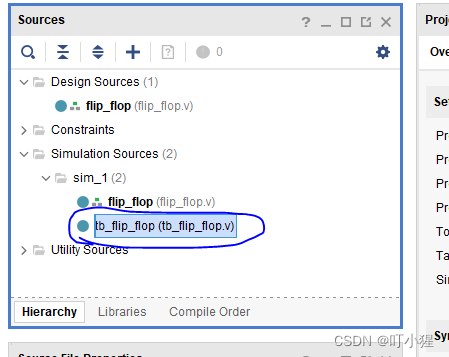

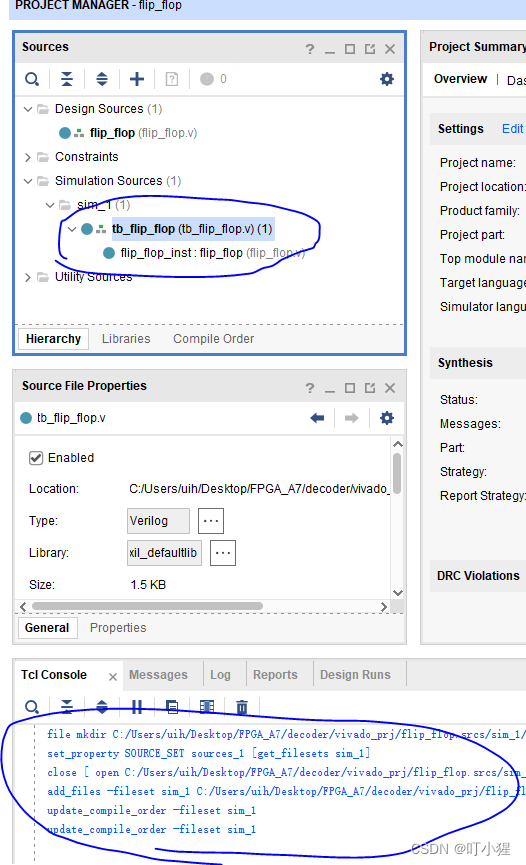

添加仿真文件

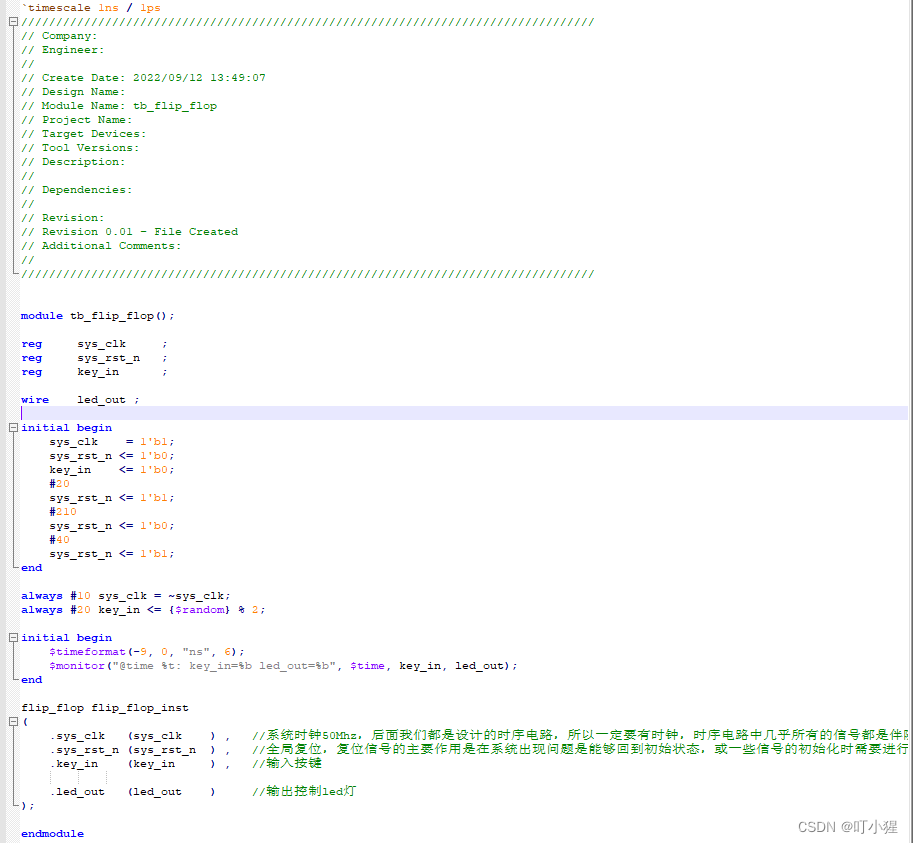

双击tb_flip_flop.v文件,开始编辑仿真代码testbench

仿真代码testbench如下,保存:

vivado自动编译,无异常

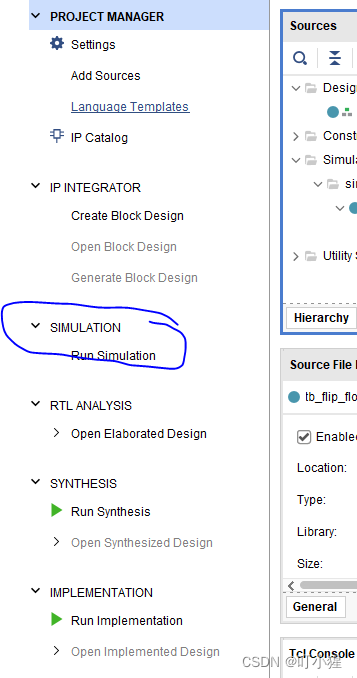

点击Run simulation

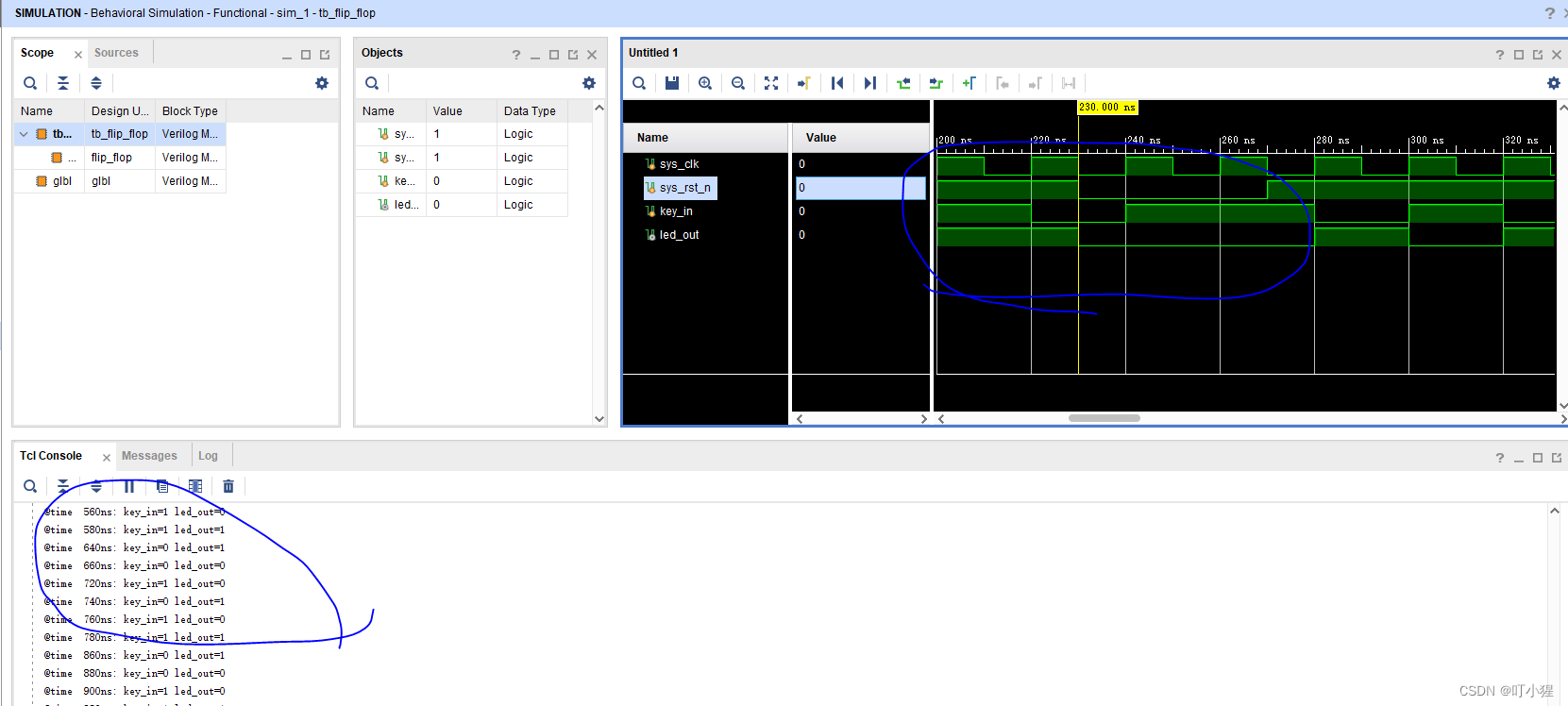

仿真结果无问题,如下:

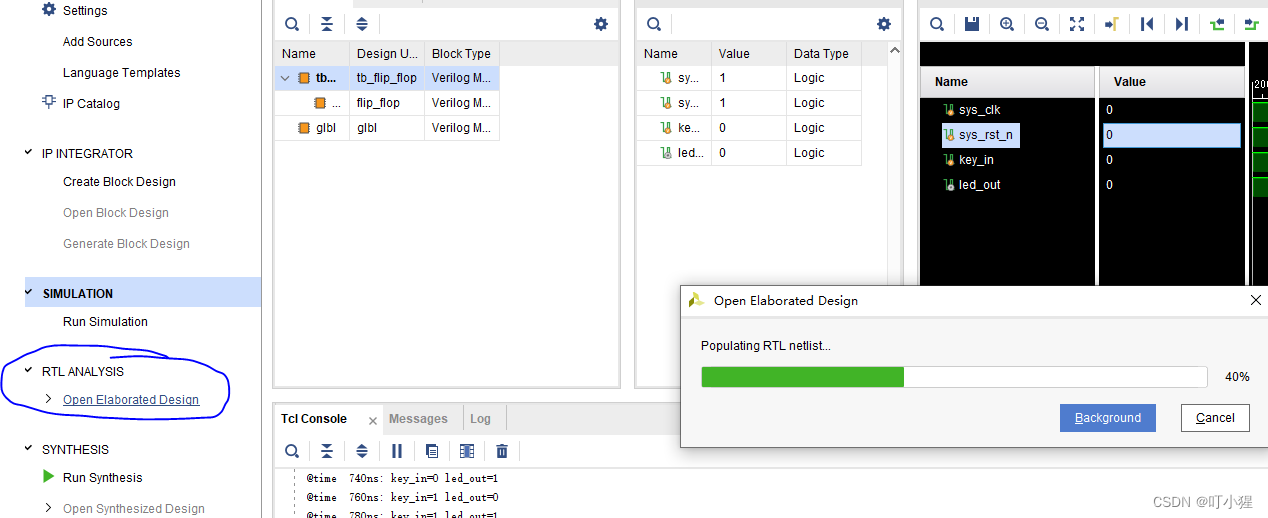

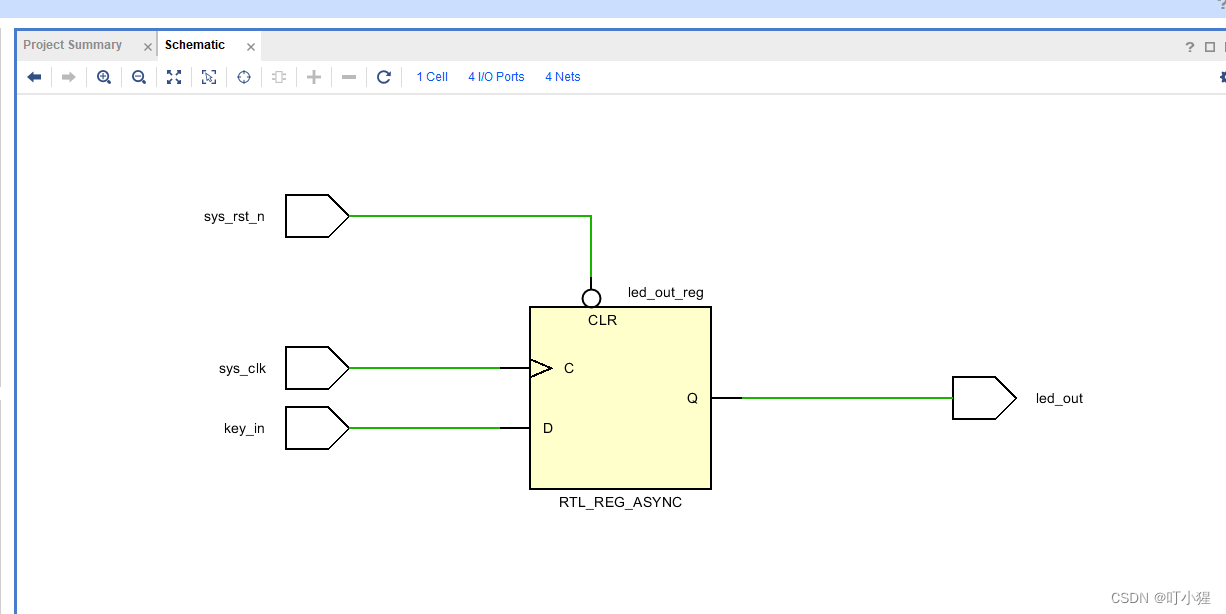

点击RTL分析

电路如下图所示。

(如果要硬件模拟的话,可以点击图中的I/O Ports,分配好硬件管脚后(其实就是xdc文件,也可以软件编辑),生成bitstream文件后再烧录到硬件上,即可),【这个D触发器的例子不太好硬件实现,下面以流水灯来实现代码烧录】

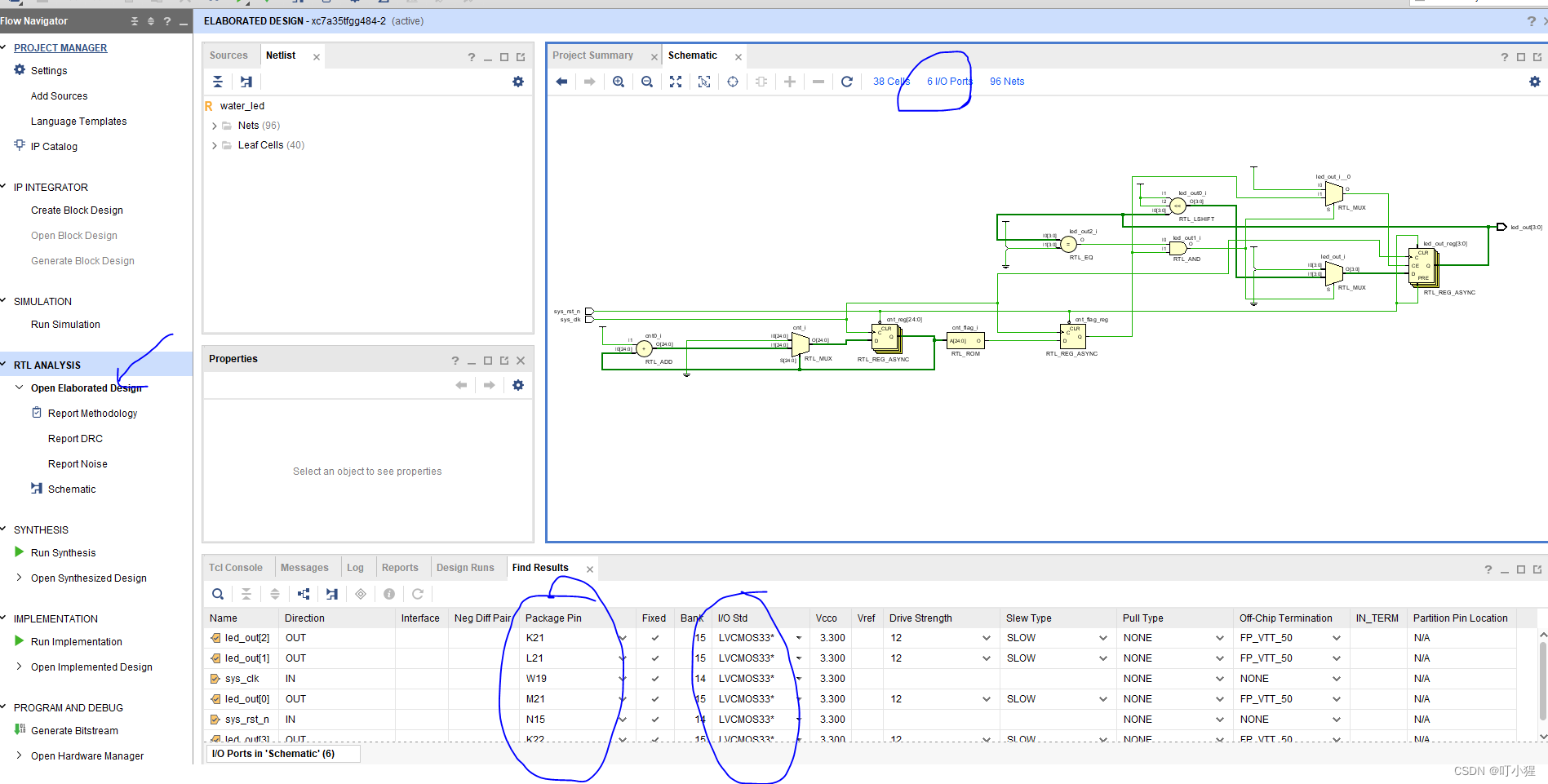

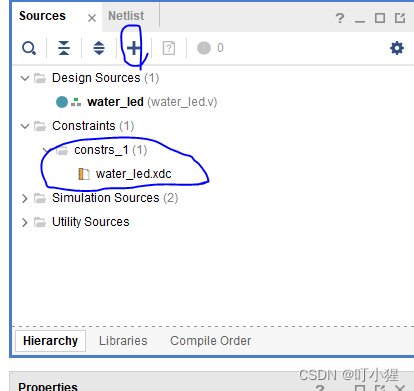

点击在RTL分析里的I/O Ports,绑定管脚,并按下CTRL+S保存成.xdc文件【或者直接在约束文件中添加xdc文件】

或者,直接添加xdc文件,以绑定管脚

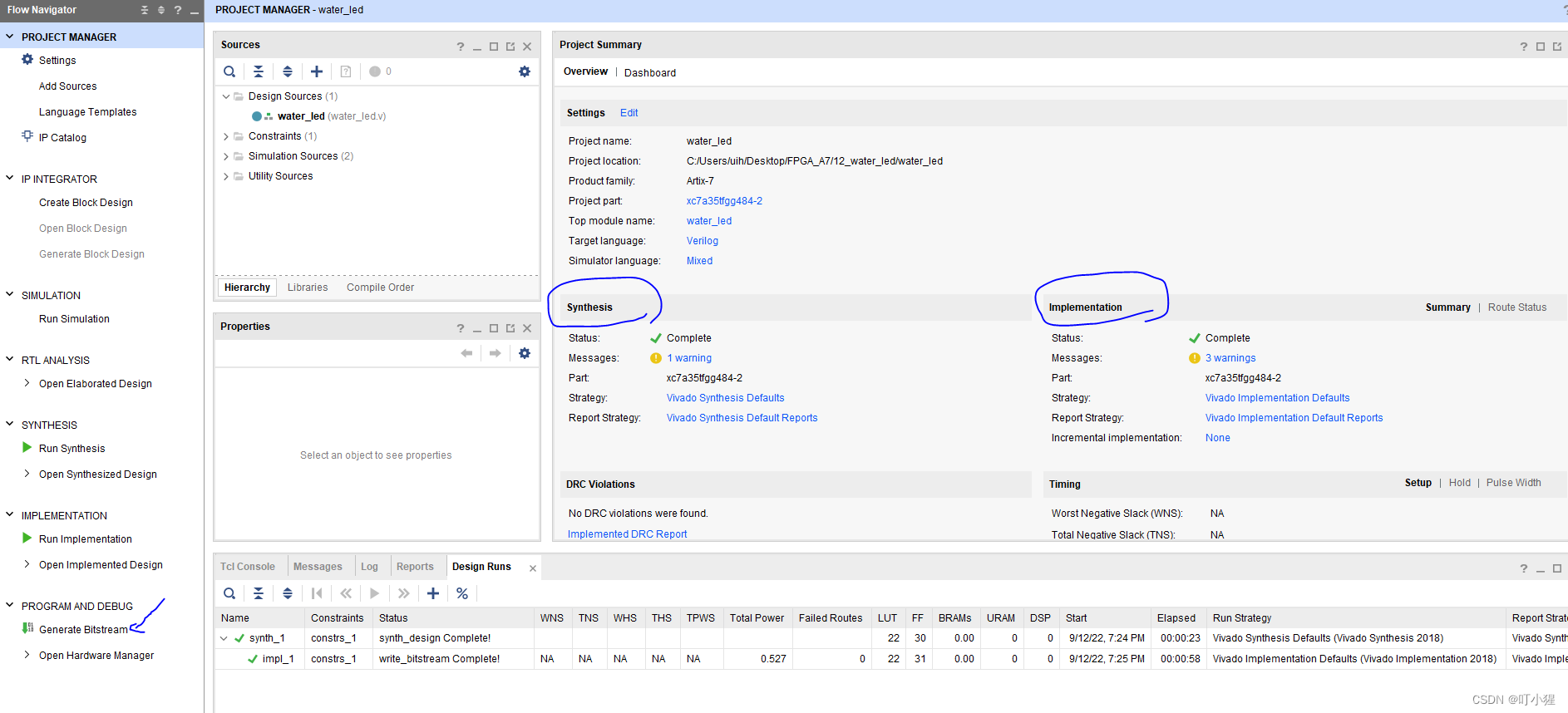

生成bitstream文件(时间较慢,耐心等待右上角的缓存)

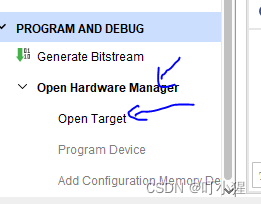

烧入文件,选择open Target -->auto connect

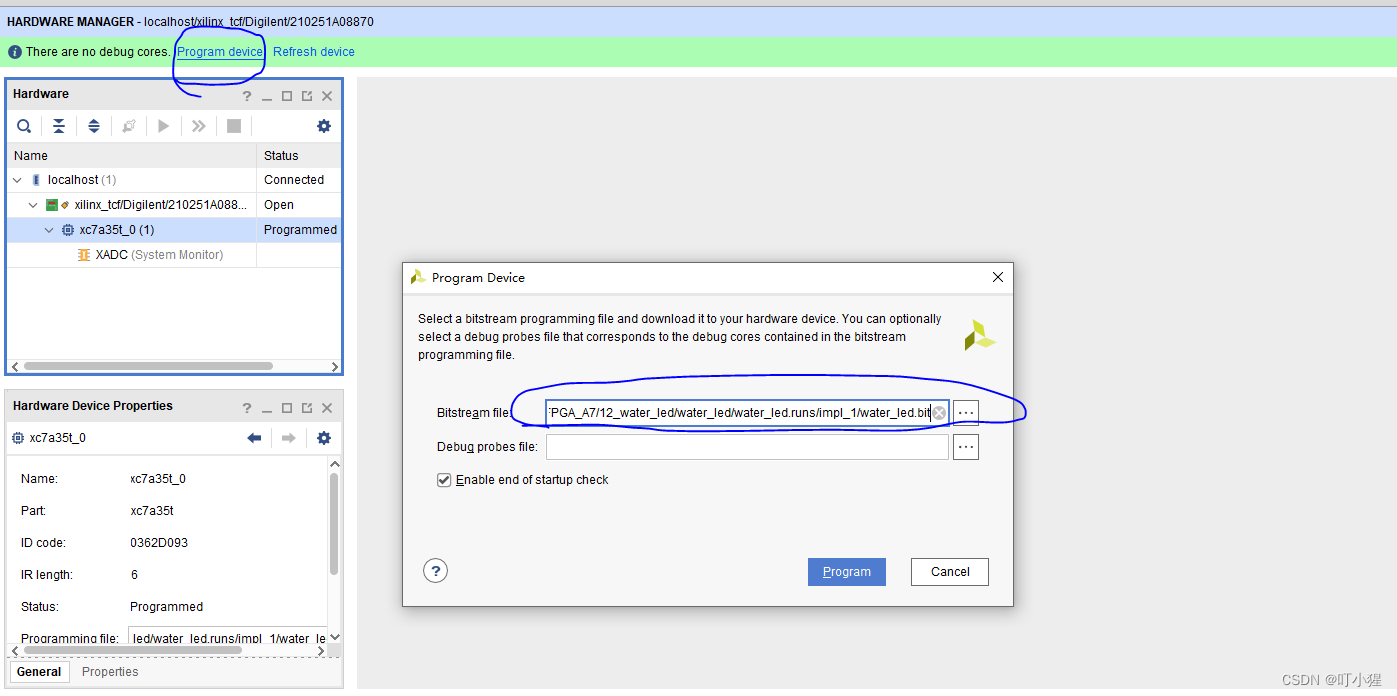

点击Program device,弹出的框中选择对应的.bit文件,并烧录

注意,FPGA芯片掉电数据会丢失,可以将数据烧录进Flash上,将Flash作为FPGA芯片的上电配置器件,将上电程序固化在Flash中,上电后FPGA芯片读取到Flash中存储的程序进行运行,做到程序断电不丢失

烧录文件在开发板上掉电不丢失的方法

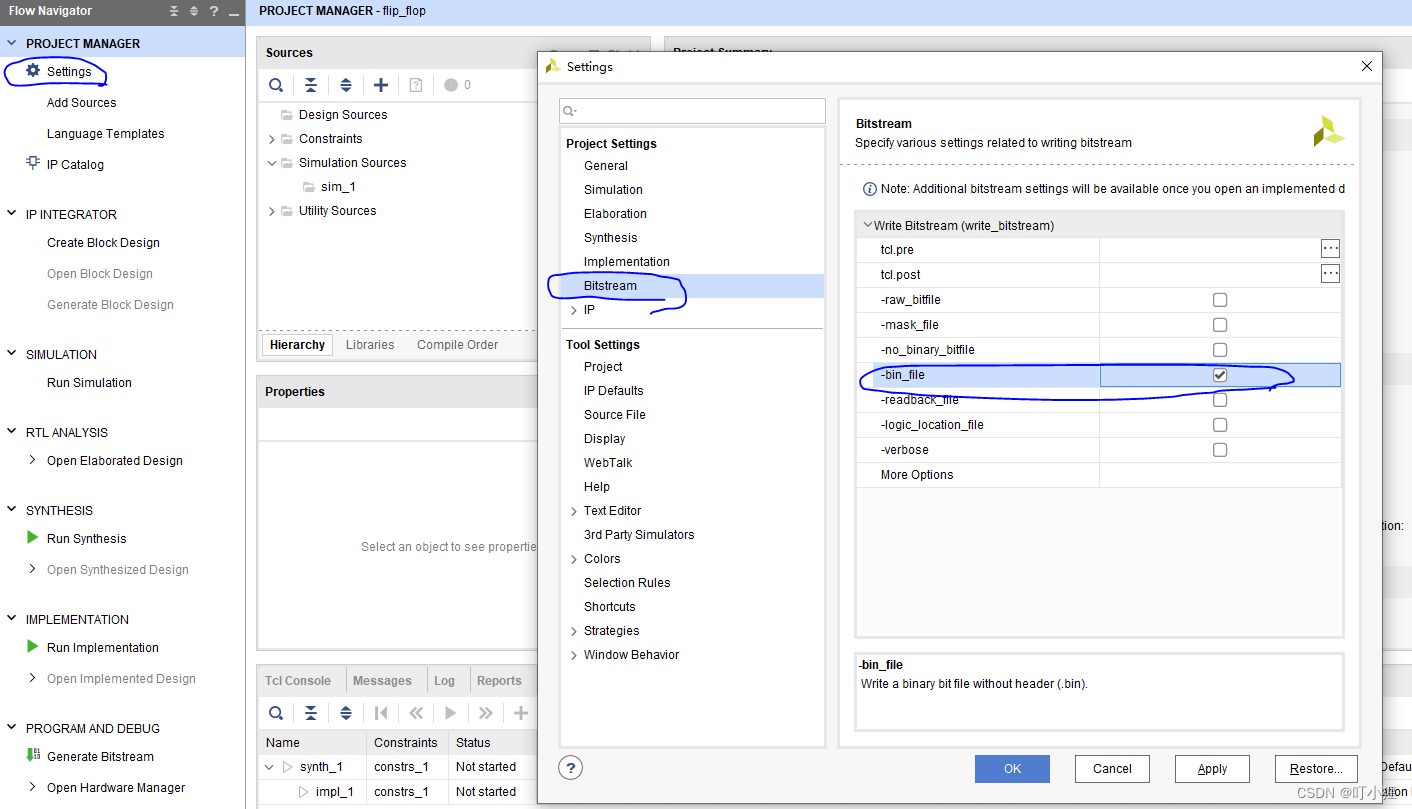

在settings中勾选 生成bin文件

重新生成bitstream,此时会同时生成bin文件

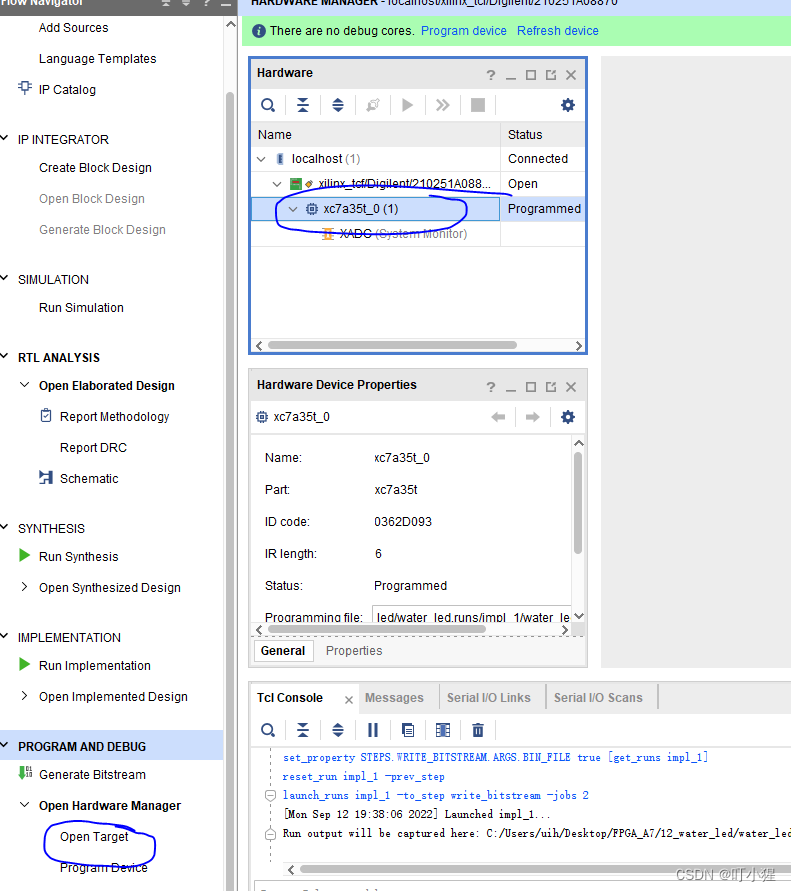

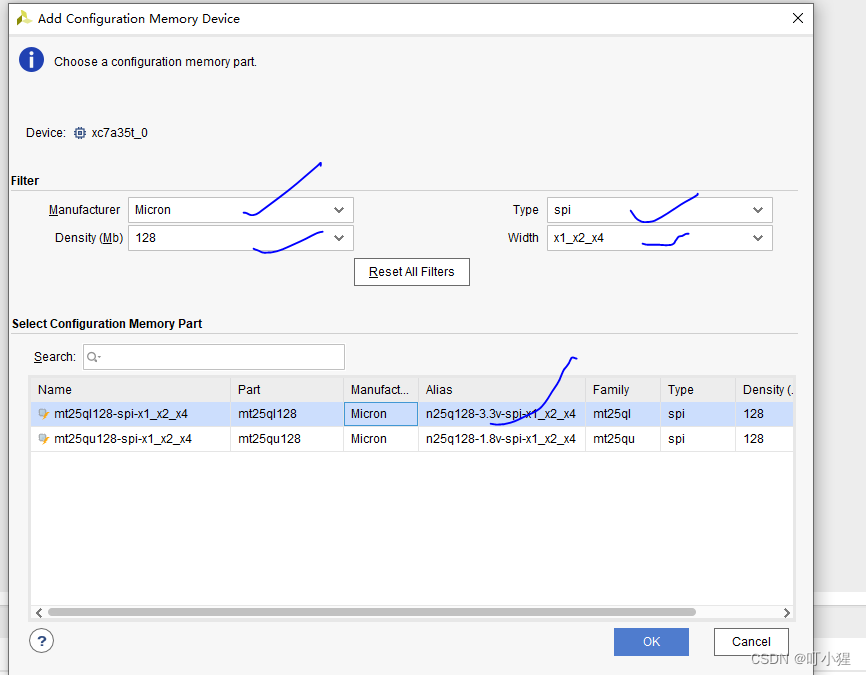

在open target中的Hardware栏中,右击芯片型号(这里是xc7a35t),选择add configuration memeory device

在弹框中配置相应的参数

弹出如下弹框,点OK

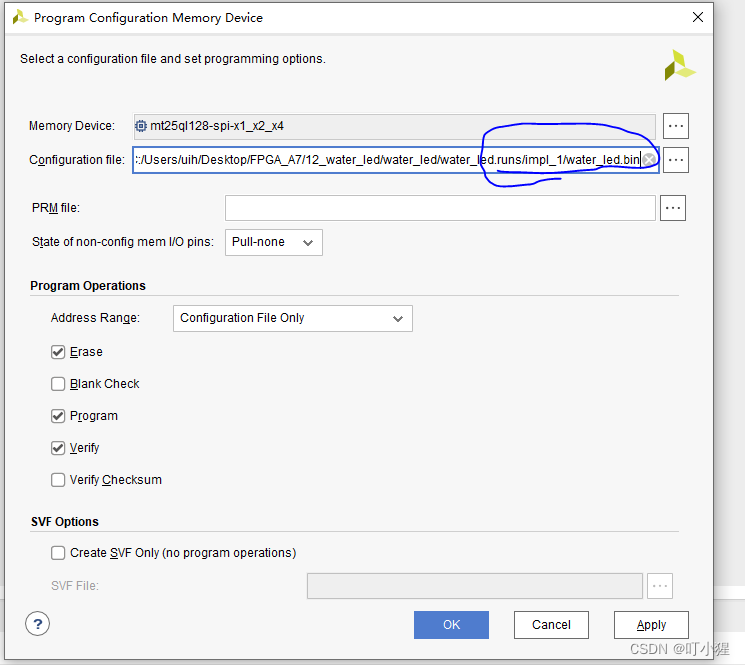

选择生成的bin文件(在xxx.runs/impl_1文件夹下)

烧录成功,需要在开发板上手动复位【复位按键】,流水灯就实现了

本文详细介绍了FPGA设计流程,从规划、代码编写到硬件烧录,特别强调了如何在Vivado中操作。通过实例展示了如何创建工程、编写D触发器代码、进行仿真验证,并解释了如何绑定管脚、生成bitstream文件。此外,还讨论了如何使FPGA设计在掉电后仍能保持,即通过烧录到Flash实现程序的断电不丢失。

本文详细介绍了FPGA设计流程,从规划、代码编写到硬件烧录,特别强调了如何在Vivado中操作。通过实例展示了如何创建工程、编写D触发器代码、进行仿真验证,并解释了如何绑定管脚、生成bitstream文件。此外,还讨论了如何使FPGA设计在掉电后仍能保持,即通过烧录到Flash实现程序的断电不丢失。

3091

3091

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?