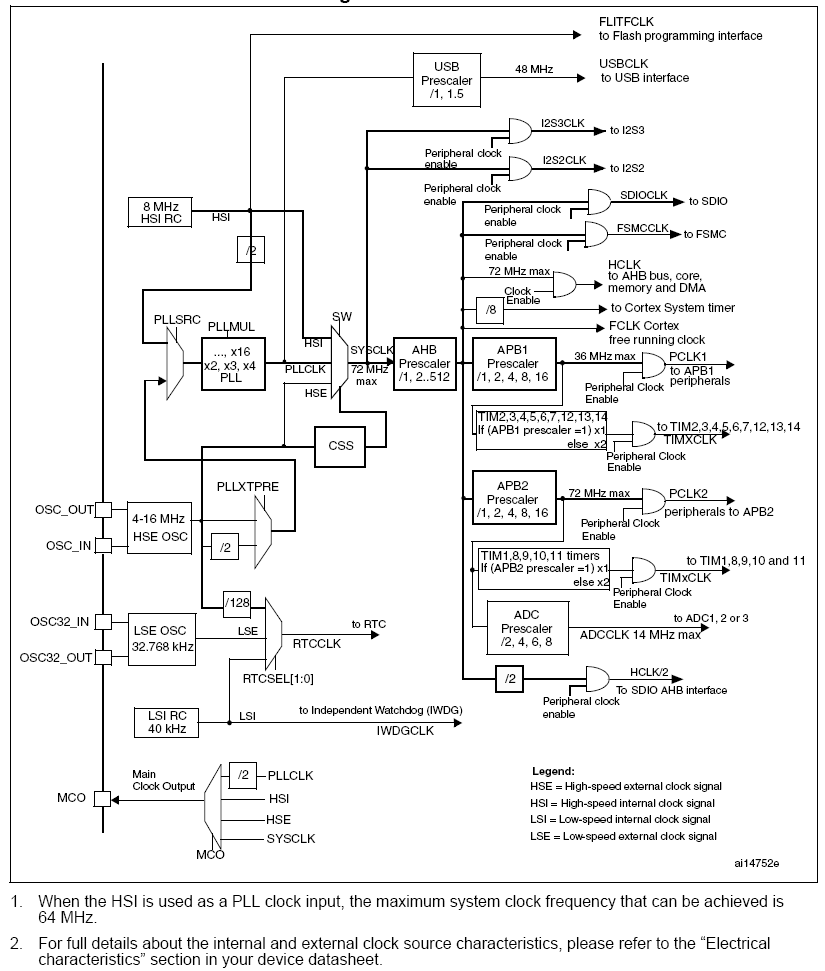

开发板用的是8Mhz晶振,即HSE=8,000,000

f103最大支持72Mhz,即SYSCLK=PLLCLK=72Mhz,HSE=8M,所以PLLM=9即可。

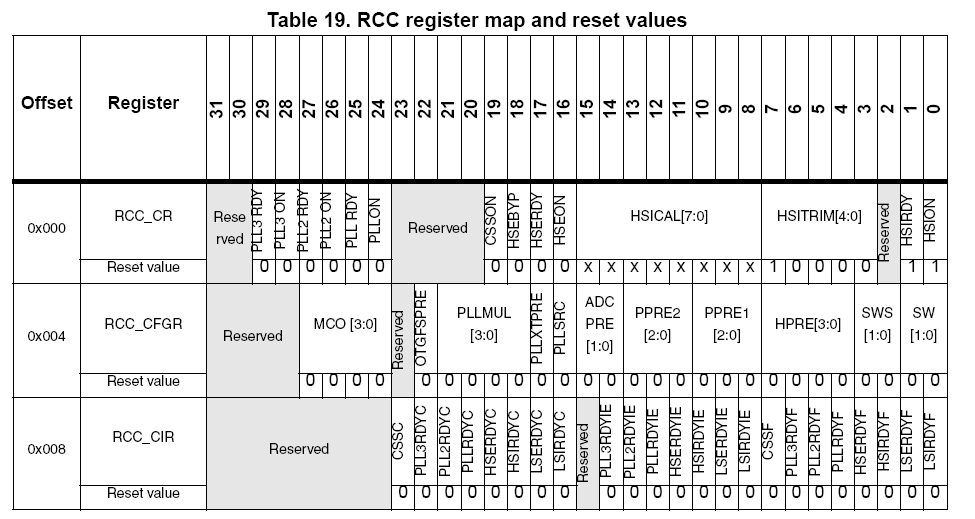

/* HCLK = SYSCLK */ RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1; /* PCLK2 = HCLK */ RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1; /* PCLK1 = HCLK */ RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2; /* PLL configuration: PLLCLK = HSE * 9 = 72 MHz */ RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL)); RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);

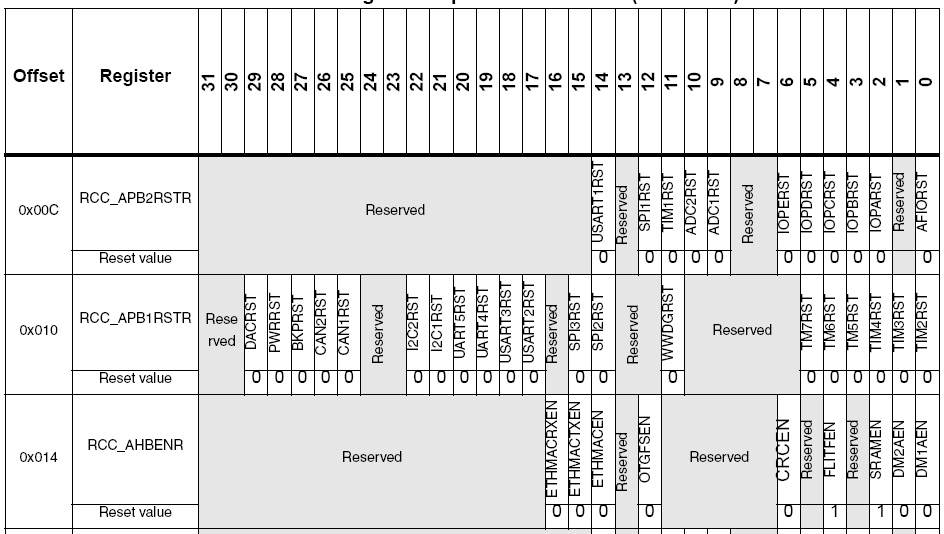

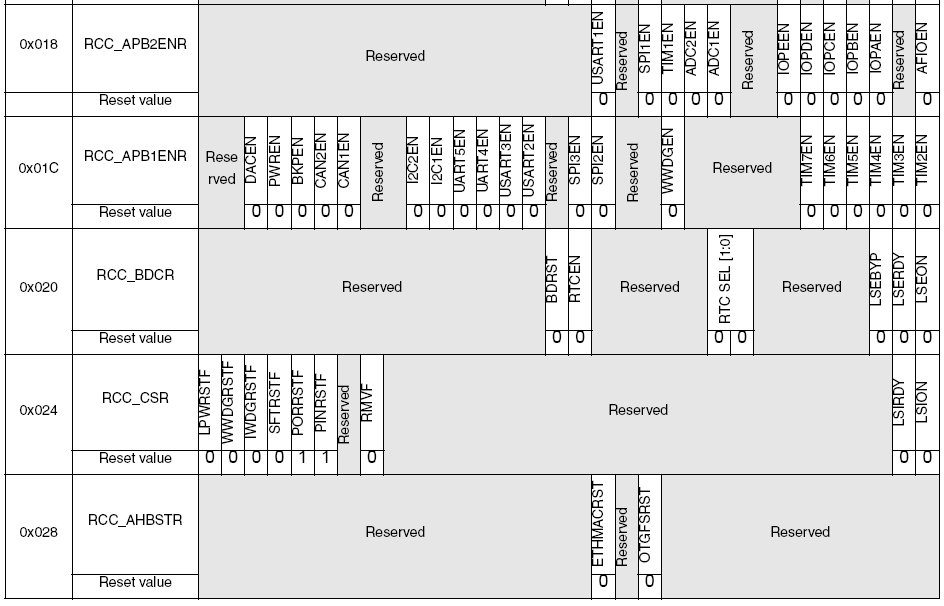

本文介绍如何通过配置STM32的PLL来实现72MHz的系统时钟频率。使用8MHz的外部晶振作为时钟源,通过PLL倍频至72MHz,并设置AHB、APB2和APB1预分频器,确保外设得到正确的时钟频率。

本文介绍如何通过配置STM32的PLL来实现72MHz的系统时钟频率。使用8MHz的外部晶振作为时钟源,通过PLL倍频至72MHz,并设置AHB、APB2和APB1预分频器,确保外设得到正确的时钟频率。

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?