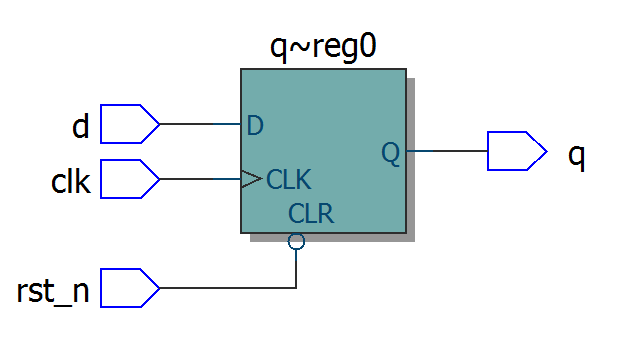

module D_Flip_Flop(

clk,rst_n,d,q);

input clk;

input rst_n;

input d;

output reg q;

always @(posedge clk or negedge rst_n)

if(!rst_n)

q <= 1'b0;

else

q <= d;

endmodule

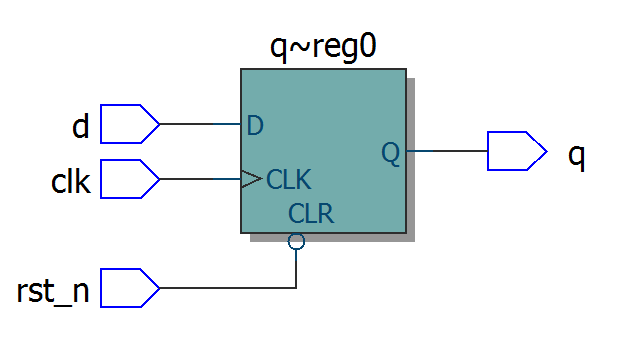

module D_Flip_Flop(

clk,rst_n,d,q);

input clk;

input rst_n;

input d;

output reg q;

always @(posedge clk or negedge rst_n)

if(!rst_n)

q <= 1'b0;

else

q <= d;

endmodule

转载于:https://www.cnblogs.com/bixiaopengblog/p/6202324.html

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?