低功耗三元SRAM的设计与分析

摘要

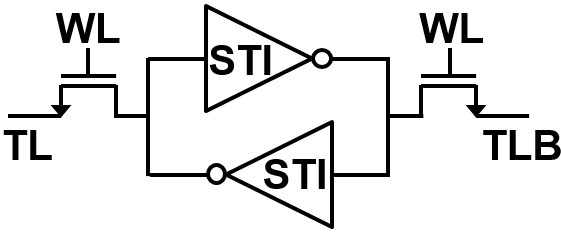

本文提出了一种三态反相器的设计,该反相器在输入电压低于VDD/2时使用较低的电流。当电源电压设置为1伏特时,以VDD/2作为输入电压的电压源所提供的电流从1.89µA减少到1.46µA,降幅达22.75%。通过将三态反相器背对背连接,构成一个用于存储三元位(trit)的存储单元,实现为三元SRAM单元。本文还首次验证了考虑噪声容限的读写方案。

一、引言

多值逻辑(MVL)系统可作为一种解决方案,以克服传统二进制逻辑系统在尺寸缩小方面所面临的挑战[1]。这一优势的产生是因为,与二进制逻辑系统相比,MVL系统使用逻辑门实现功能模块,从而减少了布线导线所需的硅面积以及功耗[2]。已有研究探讨了三进制电路MVL设计,如加法器和乘法器[3],[4]。研究人员已对利用传输晶体管合成三进制逻辑门的低功耗技术进行了研究[5]。为了实现诸如微处理器等三进制数字系统的完整性,强烈建议实现静态随机存取存储器等存储组件。

三元SRAM单元的结构和读写操作已设计完成[6],[7]。然而,[6]中的标准三态反相器(STI)具有三个电源:地、VDD/2和VDD,因此互连结构复杂,这种复杂性削弱了多电平逻辑系统减少布线导线数量的优势。此外,由于二极管连接的STI[4]在输入电压施加到VDD/2[5]时功耗显著,[4]中的三元SRAM单元存储能力不足。另外,[4],[6]未展示其读写方案的噪声容限,因此无法确保其操作稳定性。

本文提出了一种可存储三电平状态的低功耗三态SRAM单元,并提供了读写操作的操作方案。第二节阐述了静态传输接口(STI)的概念,并提出了STI的新设计。第三节定义了三元SRAM单元的读写方案及静态噪声容限(SNM)。第四节给出了三元SRAM单元的噪声容限和读写操作的仿真结果与分析。第五节提出了结论。

II. STI的设计与分析

在设计三元SRAM单元之前,应验证合适的STI操作,以确保使用背对背反相器的存储单元能够稳定工作。

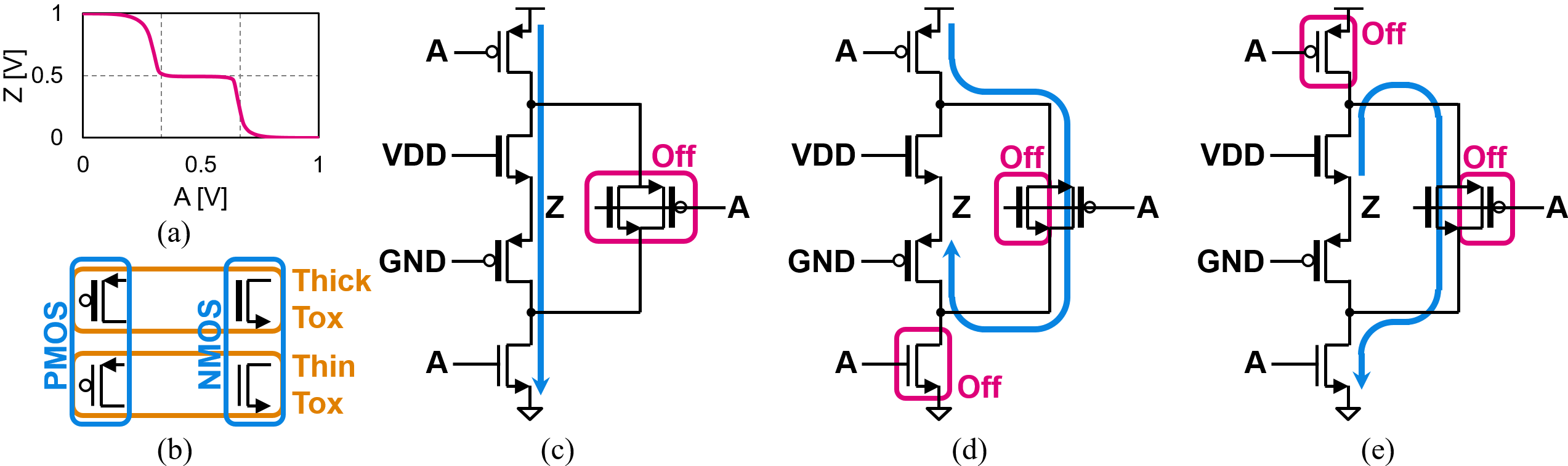

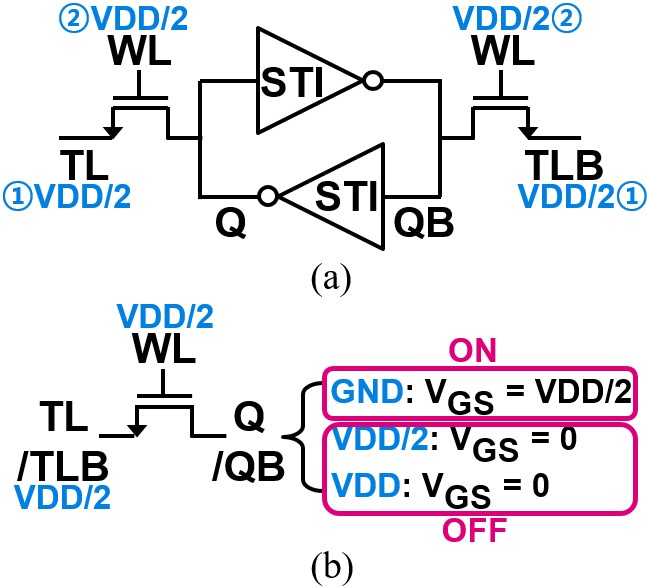

如图1所示。在三进制逻辑中,GND、VDD/2和VDD电压分别表示逻辑值0、1和2。在静态传输接口(STI)的逻辑运算中,输入情况0、1和2分别产生输出2、1和0。为了获得足够的噪声容限,静态传输接口应具有适当的电压传输特性(VTC)曲线,如图2a所示。

为了设计静态传输接口,采用多阈值CMOS技术来实现三元开关操作。随着栅氧化层厚度TOX的增加,阈值电压VTH也随之增加。如图2b所示,四种类型的晶体管被应用于静态传输接口的实现。具有较厚Tox的pmos仅在栅极电压为GND时发生切换,而具有较薄TOX的PMOS仅在栅极电压为GND或VDD/2时发生ON切换。NMOS的开关操作由TOX类似地确定。

静态传输接口的晶体管级原理图及其在三种输入情况下的操作分别为:输入电压为VDD/2=对应逻辑1(图2c),VDD=对应逻辑0(图2d),以及GND=对应逻辑2(图2e)。在图2c中,当输入为VDD/2时,栅极连接至输入节点(A)的厚TOX晶体管导通OFF;电流经过两个厚的TOX传输晶体管构成的电流路径,通过分压作用使输出电压为VDD/2。在图2d和图2e中,分别将GND和VDD作为输入电压,由蓝色线条标示的各电流路径通过上拉和下拉操作,使输出电压分别为VDD和GND。

三元逻辑电路实现的主要问题是当输出电压为VDD/2时的静态电流,因为电压源提供的电流会导致功耗。当STI的输出为VDD或GND时,上拉或下拉完全导通,因此不会产生静态电流,但如果STI的输出为VDD/2,则会有一些静态电流流动。因此,三元逻辑电路的设计应包括在输出为VDD/2时降低电流的方法。

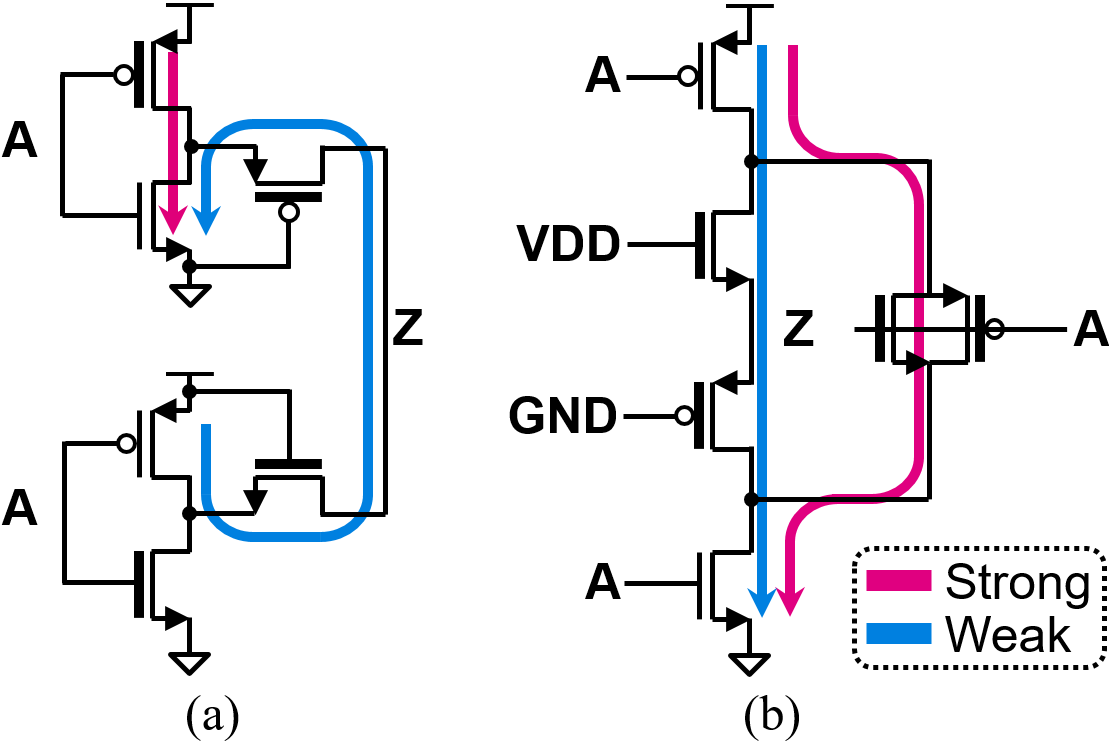

静态传输接口[5]的现有结构;(b) 提出的STI结构。对于这两种STI,厚‐TOX晶体管的宽长比均设为80/30[纳米/纳米],薄‐TOX晶体管的宽长比设为240/30[纳米/纳米]。)

静态传输接口[5]的现有结构;(b) 提出的STI结构。对于这两种STI,厚‐TOX晶体管的宽长比均设为80/30[纳米/纳米],薄‐TOX晶体管的宽长比设为240/30[纳米/纳米]。)

在[5]中,采用两个传输晶体管、一个厚‐TOX pmos和一个厚‐TOX NMOS来实现VDD/2的输出电压。当输入电压为VDD/2时,栅极连接到输入节点的厚晶体管理论上处于OFF关断状态。此外,两个厚‐TOX传输晶体管实际上表现为高电阻,并直接影响分压至VDD/2。因此,电压源提供的电流较小。然而,当栅极电压为VDD/2时,考虑到两种情况:厚‐TOX晶体管的关断电阻不够高,或处于亚阈值区,厚‐TOX晶体管并未完全关断OFF。因此,我们提出了一种方法,以在输出电压为VDD/2时降低电压源所提供的电流。

在图3a和图3b中,输入电压为VDD/2,厚‐TOX晶体管未完全关断,因此提供了两条路径,一条电流微弱流动,另一条电流强烈流动。通过如图3b所示,将栅极连接到输入节点的厚‐TOX晶体管进行移位,强电流路径经过的晶体管比图3a中的STI更多,具有更大的等效电阻。因此,通过将图3a中所示的现有STI结构修改为图3b中提出的结构,当输入电压为VDD/2时,电压源提供的电流得以减少。通过实施直流分析,该优点在第三节中得以验证。

三元SRAM单元的读/写方案和SNM

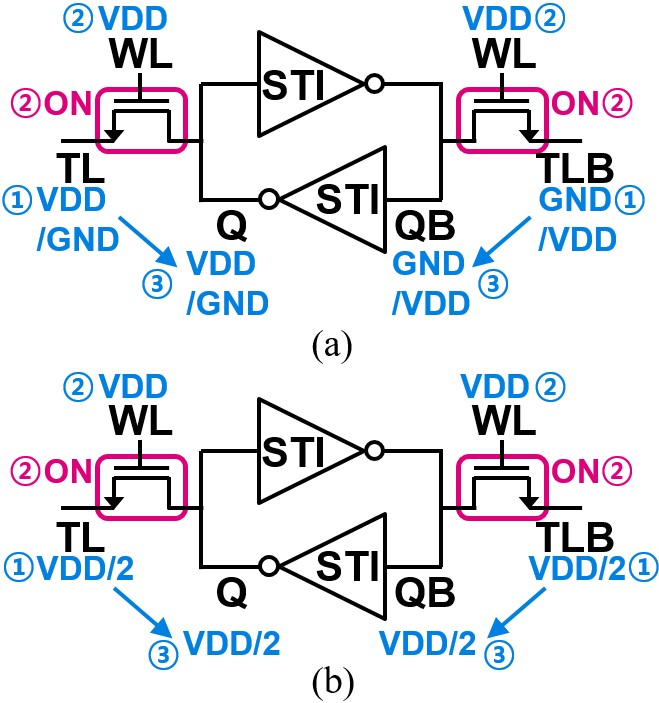

本节提出了三元SRAM单元的读写方案以及保持、读取和写入时的噪声容限。三元SRAM单元的写入方案如图4所示。如图4a所示,为了在节点Q处写入VDD/地,第一步是将三进制线(TL)设置为VDD/地,并将三进制反线(TLB)设置为地/VDD。此外,将字线(WL)设置为VDD以导通访问晶体管,强制节点Q为高/低电平,QB为低/高电平。图4a中所示的写入地/VDD的方法与6T‐SRAM单元的传统写入方案相同。然而,图4b所示的写入VDD/2的方法被添加到现有的写入方案[7]中。当VDD/2在节点Q写入时,TL和TLB均被设置为VDD/2,然后WL被设置为VDD,从而使节点Q和QB被感应至VDD/2。

表示将Q和QB都写为VDD/2的情况。)

表示将Q和QB都写为VDD/2的情况。)

图5a表示三元SRAM单元的读取方案。首先,TL和TLB都被预充电至VDD/2。然后,将WL设置为VDD/2,而不是VDD,以防止存储的数据翻转。如图5b所示,为了使访问晶体管导通,VGS应大于VTH。因此,只有当Q/QB=GND时,电流才会通过访问晶体管从TL/TLB流向Q/QB,从而使TL/TLB放电至地。假设Q和QB存储的是VDD/2,则TL和TLB均不会放电。

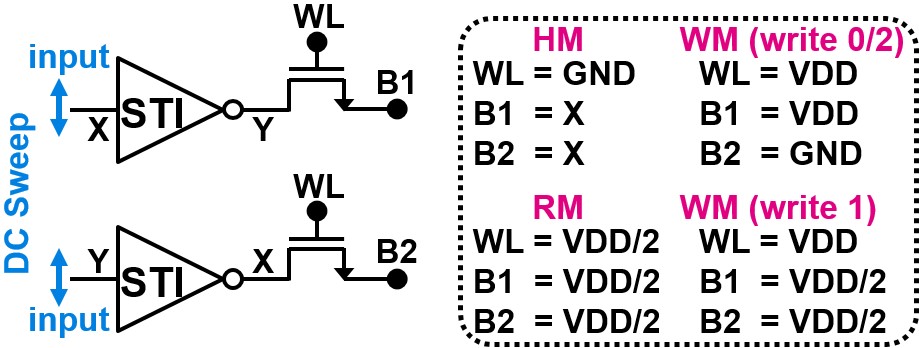

三元SRAM单元的保持、读取和写操作的稳定性应得到保证,因此需要测量三个SNM(即保持裕度(HM)、读取裕度(RM)和写入裕度(WM))。如图6所示,已设计相应电路,并确定了用于测量HM、RM和WM的各节点所需电压电平。在完成图6所示的“置位”操作后,可通过直流分析和蝴蝶曲线方法来测量HM、RM和WM。

IV. 仿真结果与分析

本节演示了通过应用图6中的方法可以获得每个裕度。同时,验证了写入方案,并证明了读取方案的可行性。采用三星28nm技术进行了SPICE仿真。VDD设置为1.0V。

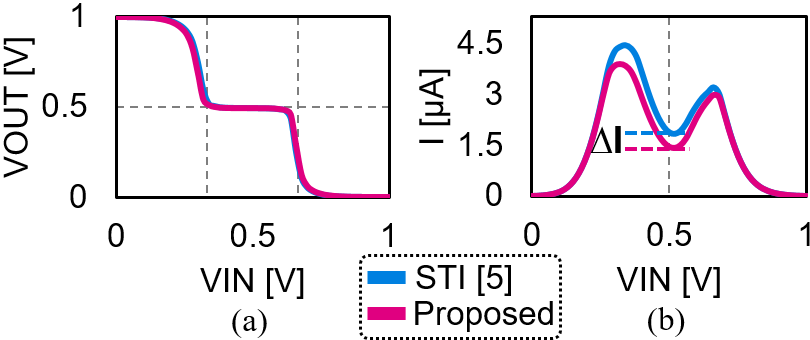

将提出的STI与图7所示的现有STI[5]进行了比较。在仿真中,当输入电压为VDD/2时,我们的设计(1.46µA)比现有设计减少了22.75%的电流,静态传输接口(1.89µA),而两个静态传输接口的VTC曲线相似。

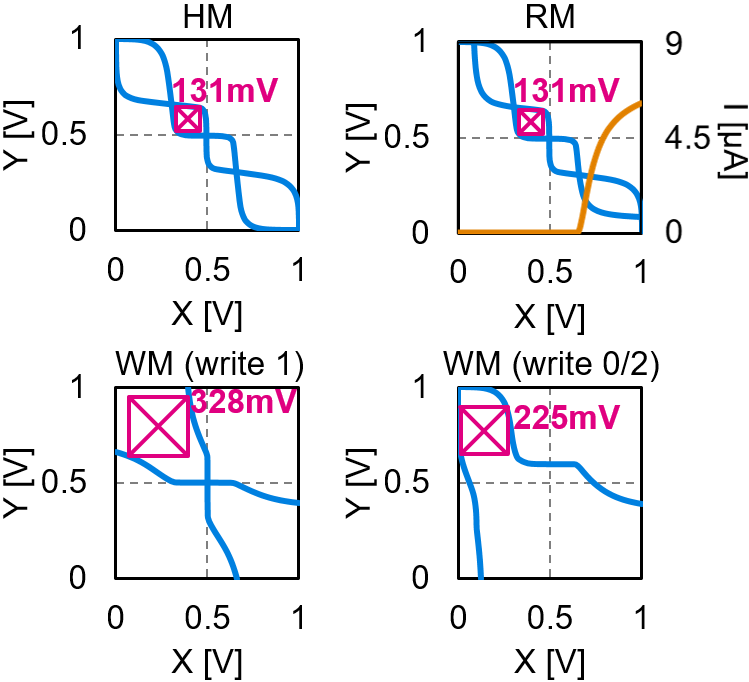

图8中测得的高噪声容限、恢复噪声容限和宽噪声容限验证了三元SRAM单元的数据存储稳定性以及所提出的读写方案的稳定性。此外,“保持”和“读取”操作具有相同的噪声裕度。因为在图6中对恢复噪声容限进行直流分析时,当将X/Y作为输入扫描,只有在Y/X存储为0时访问晶体管才会导通ON,这一点通过在图8中将节点X作为输入扫描时流经访问晶体管的电流曲线得到验证。另外,高噪声容限和恢复噪声容限是三个SNM中最低的,因此对于三元SRAM单元而言,“保持”和“读取”操作对噪声的容忍能力最弱。

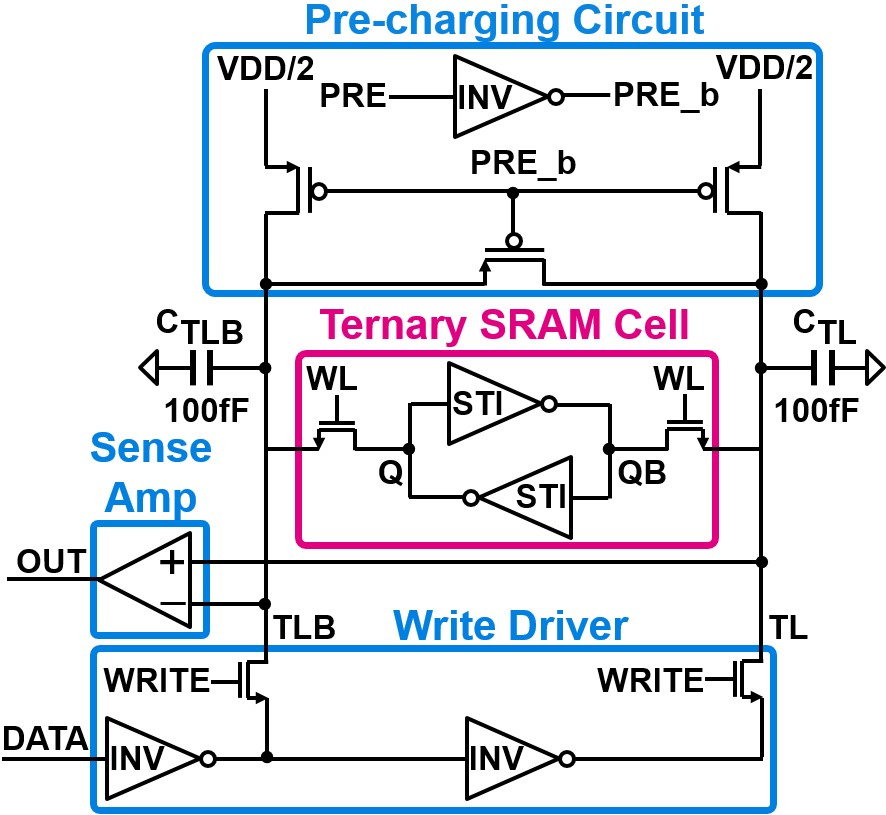

为了验证所提出的读写方案,设计了由预充电电路、三元SRAM单元和写驱动器组成的电路,如图9所示。当节点PRE变为1V时,预充电电路将VDD/2驱动至TL和TLB。此外,当节点WRITE设置为VDD后,将节点DATA施加到VDD/GND,写驱动器将TL驱动至VDD/GND,并将TLB驱动至GND/VDD。为了保持足够的噪声容限,预充电电路和写驱动器应足够强,使得TL和TLB不受三元SRAM单元驱动的影响。

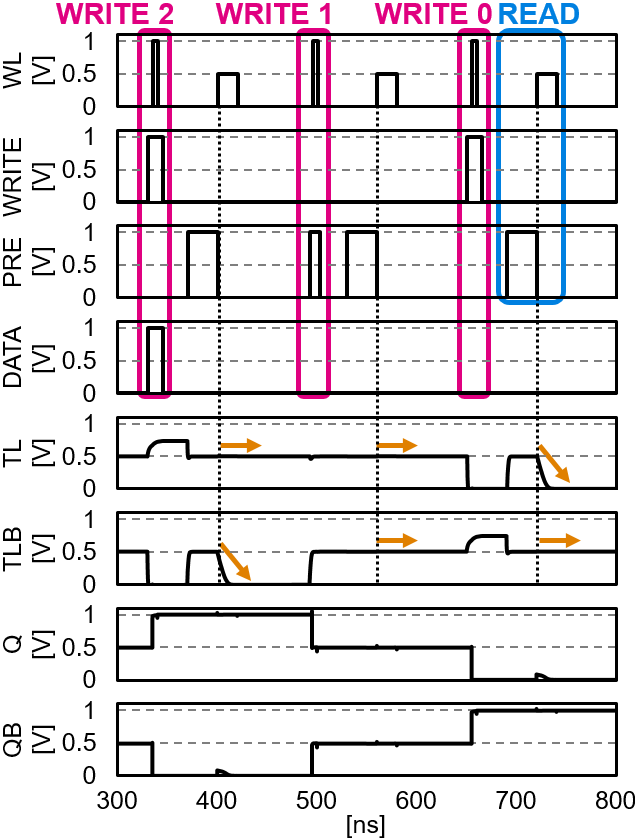

验证读写方案的仿真结果如图10所示。该写入方案可按照2、1、0的顺序在节点Q处写入。要在节点Q写入‘0/2’,需将VDD施加到节点WRITE以导通写驱动器,并将节点DATA设置为GND/VDD,从而将GND/VDD驱动至TL,将VDD/GND驱动至TLB。同时,WL被设为VDD;该设置使Q翻转为GND/VDD,QB翻转为VDD/GND。此外,要在节点Q写入‘1’,需将VDD施加到节点PRE,以在TL和TLB上驱动VDD/2。另外,在WL设置为VDD之后,Q和QB均变为VDD/2。

为了实现读操作,通过向节点PRE施加VDD来开启预充电电路;第一步将VDD/2预充电到TL和TLB。接着,将WL设置为VDD/2,如果Q/QB存储的是0,则TL/TLB会被放电。在访问晶体管导通后,可以通过检测TL与TLB之间的电压差来读取三元SRAM单元中存储的值:如果TL为GND/(VDD/2)/(VDD/2),而TLB为(VDD/2)/(VDD/2)/GND,则Q处存储的值分别为0/1/2。

V. 结论

本文提出了一种在输入电压小于VDD/2时消耗低电流的静态传输接口结构。此外,通过采用由两个背靠背STI构成的存储单元设计了一个三元SRAM单元,并提出了针对三元SRAM单元的读写方案。为了验证三元SRAM单元操作的稳定性,测量了三种类型的噪声容限,即高噪声容限、宽噪声容限和恢复噪声容限。对于三元SRAM单元,通过仿真包含预充电电路、三元SRAM单元和写驱动器的电路,实现了写操作并演示了“读”操作的可能性。

作为未来的工作,为了降低功耗,应改进方法以在三元静态随机存取存储器存储VDD/2时降低电流。同时,还需配合用于三元的感应电路,静态随机存取存储器读操作中,应采用使三元SRAM单元对工艺变化具有容忍度的技术。

3146

3146

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?