前言

FPGA在做版本管理时,如果手动输入版本时间那么很多人会忘,会导致这个版本管理形同虚设。所以xilinx很贴心设置了一个源语USR_ACCESS2,来获取bit生成的时间。然而很多人去使用USR_ACCESS2时却很难用起来,这是为什么呢?因为要使用USR_ACCESS2,得避开下文讲解的坑,也就是抓住关键点。

USR_ACCESS2简介

功能介绍

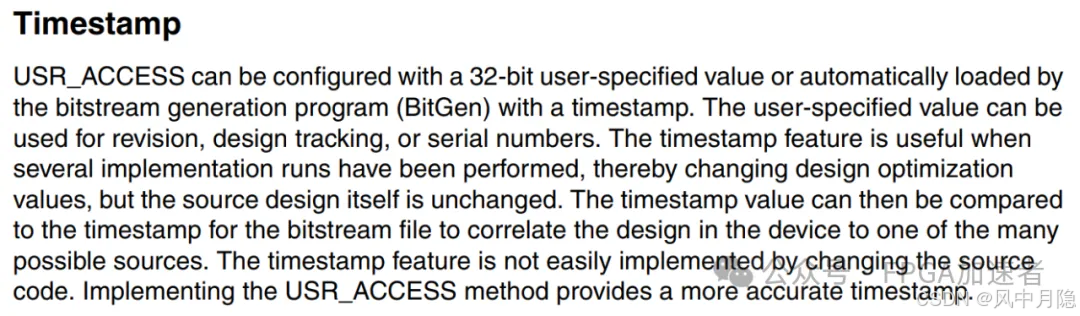

参考XAPP497可以知道 USR_ACCESS2是xilinx提供的一个可以自动获取vivado编译bit的版本时间的源语,如下介绍:

接口信号

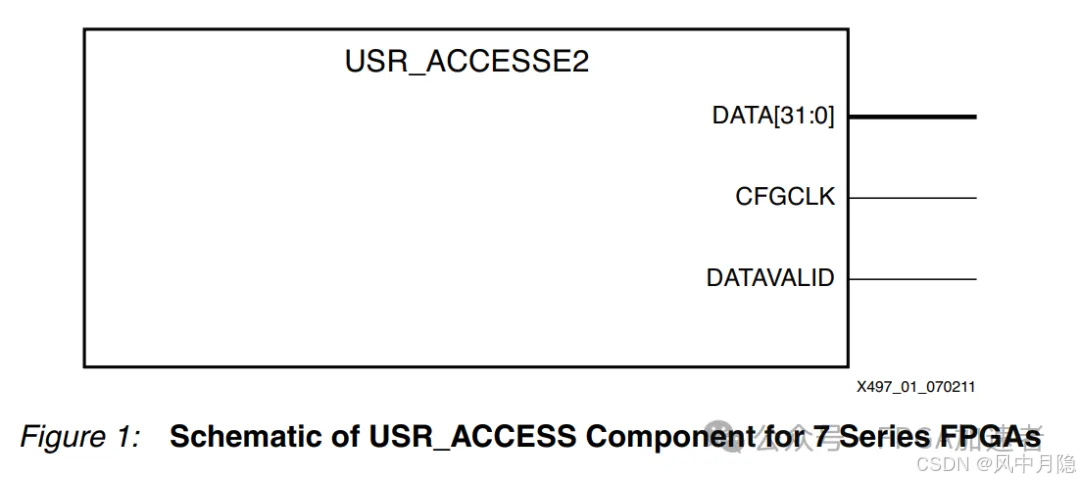

也可看到本源语接口简单如下所示:

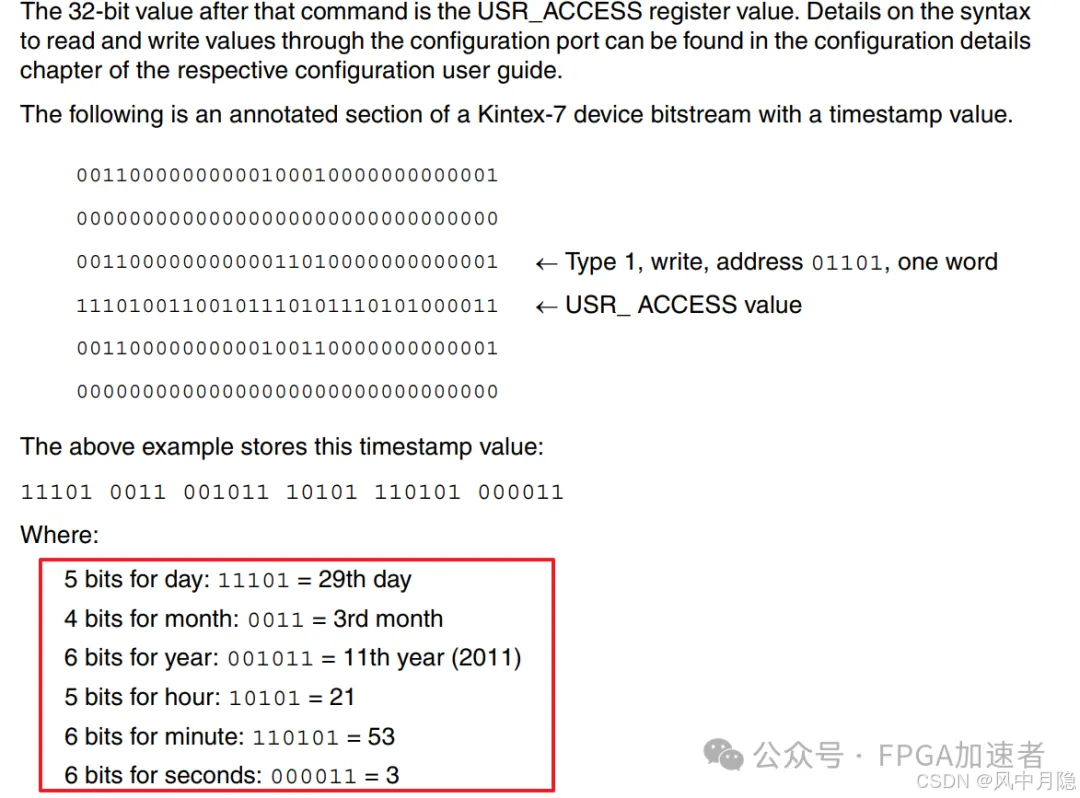

数据排列

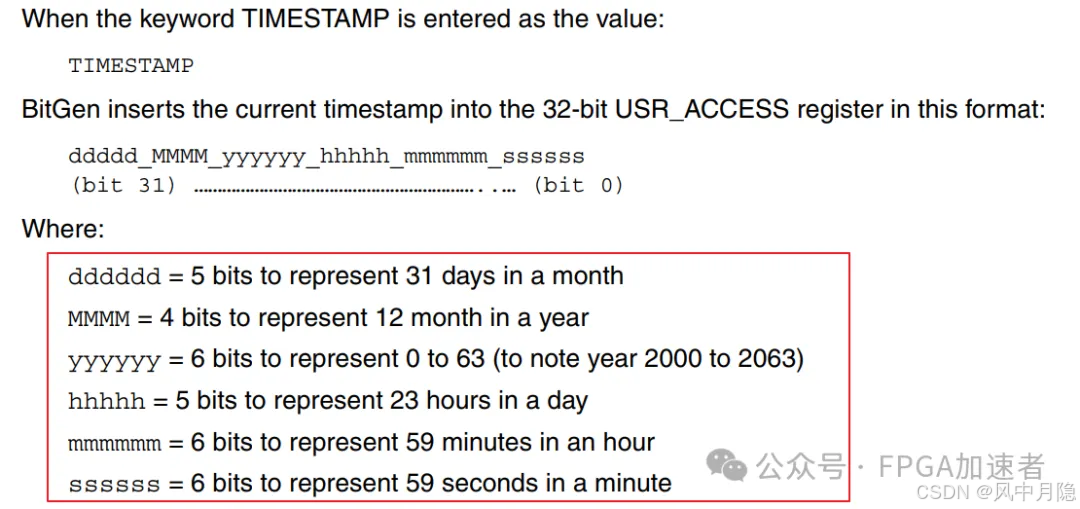

还可看到本源语的表示时间戳时的数据排列格式,如下所示:

案例解析

甚至给了示例:

关键点

1)USR_ACCESS2源语中的CFGCLK 时钟不能用来解析时间;

2)USR_ACCESS2源语中的DATAVALID 不能用来指示时间有效;

3)在xdc约束中需要以下约束;

set_property BITSTREAM.CONFIG.USR_ACCESS TIMESTAMP [current_design]

4)解析DATA中的时钟需要额外给一个固有的时钟;

5)源语中解析出来的数据是以十进制表示,而不是十六进制表示,这会导致想在fpga代码中连续表示年:月:日不好观看;

6)年的字段是6bit,只能表示0~63,默认是2000+year,所以要完整表示年的话,个人建议将解析出来的数值再加2000;

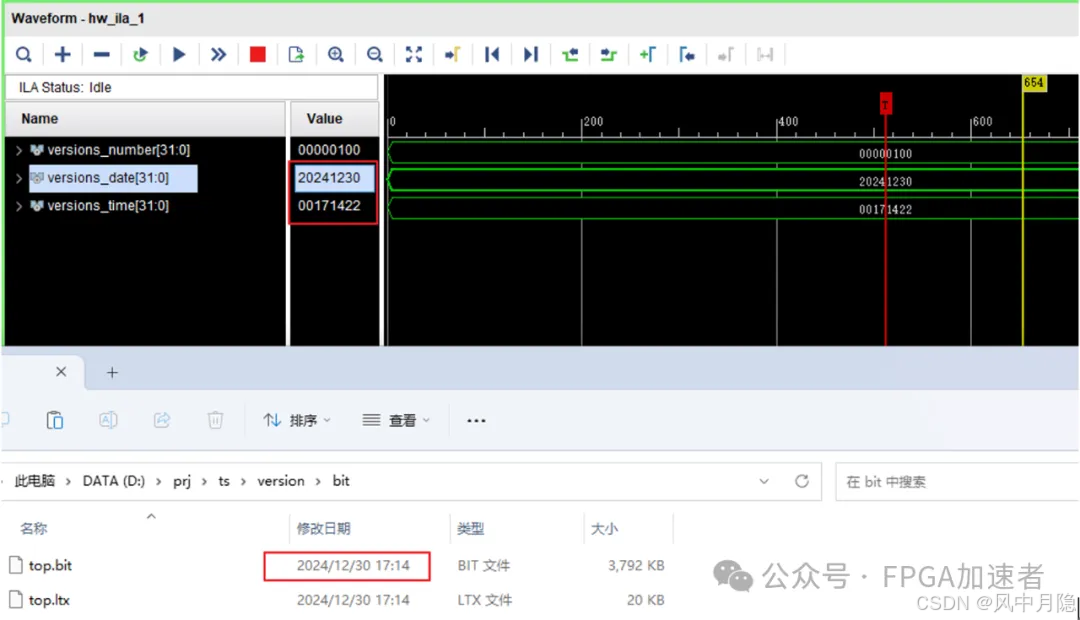

上板案例

由上图所知该代码的data与时间与bit生成的时间保持一致。

扩展知识

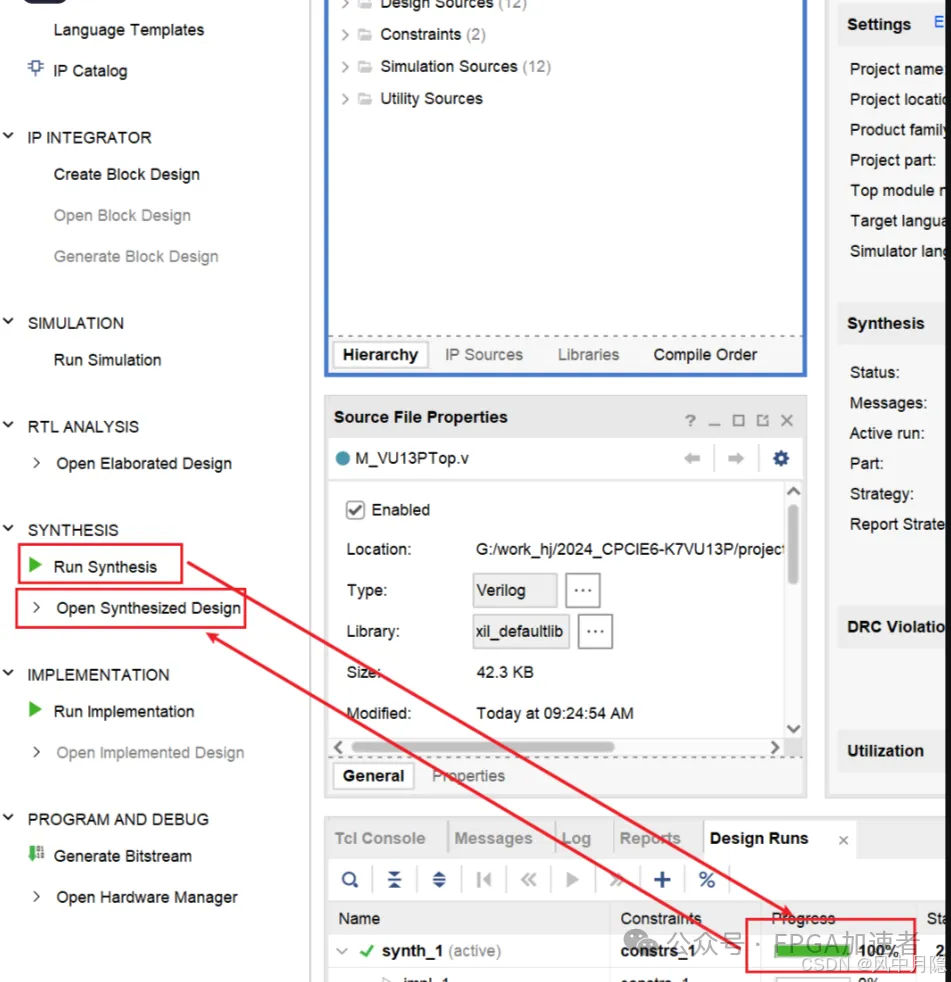

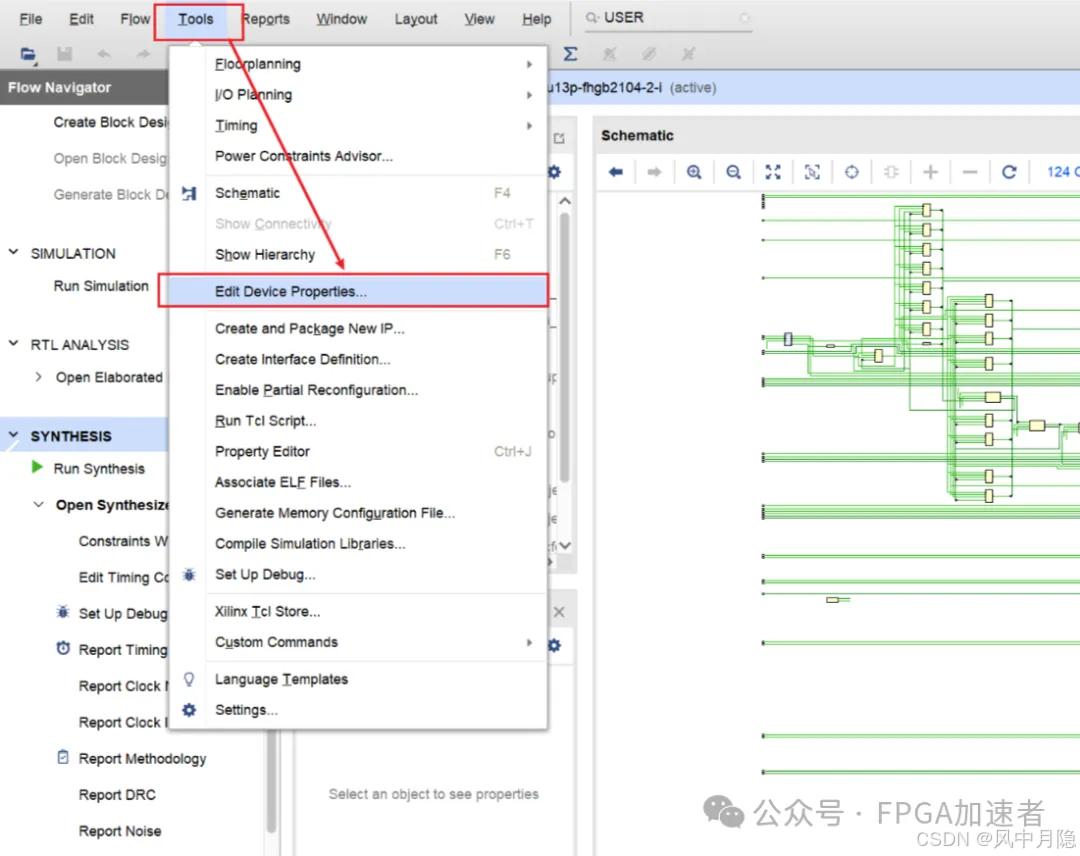

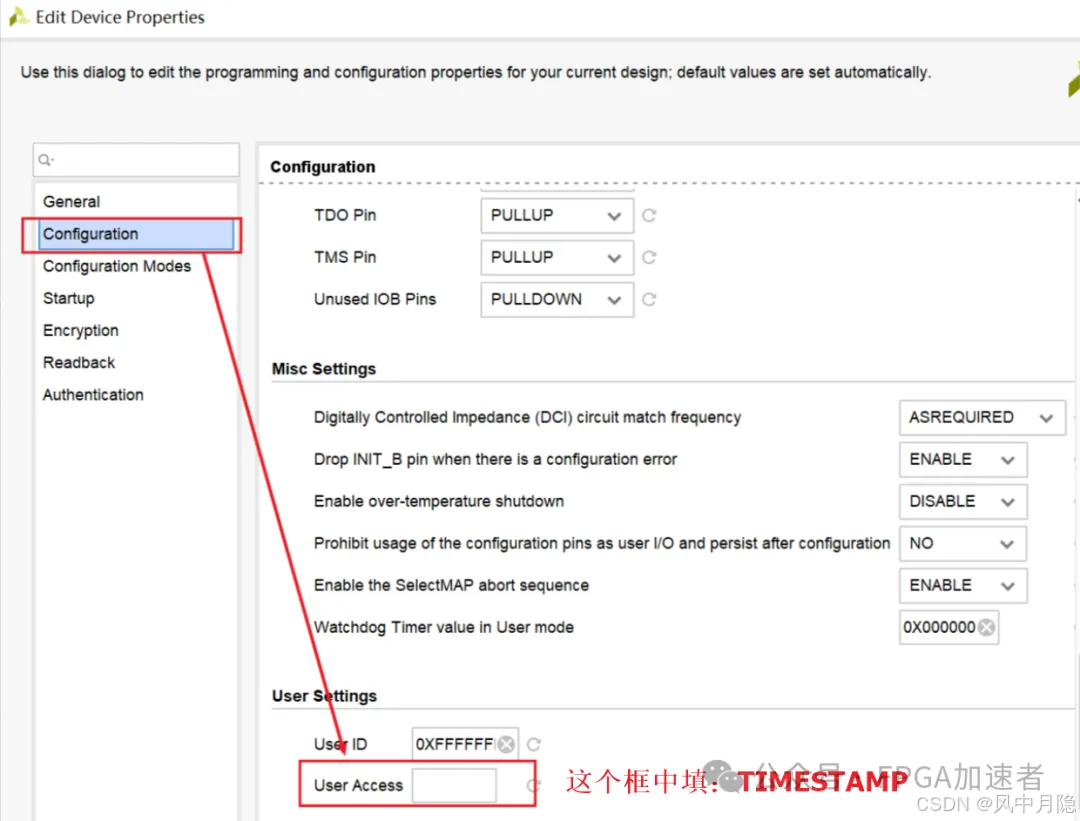

vivado工具生成约束

假如在xdc中加约束不管用时,可能是语法不对。那么这个时候建议使用vivado本身来生成这个约束。方法如下:

进制转换verilog代码

关注FPGA加速者公众号后

在后台回复:1 即可获取上板示例的代码。

在后台回复:2 即可获取xapp497。

可解析出时间版本,并转换为十六进制表示的代码。

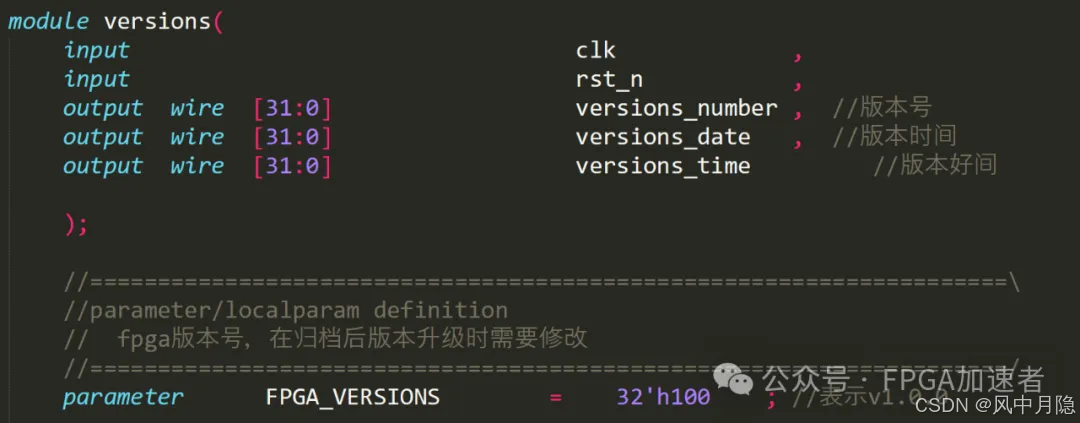

以下为代码端口示例:

文末疑问

不知道大家在弄这个FPGA自动生成bit版本时间的时候都遇到了哪些问题?

欢迎留言讨论!

如果本文对你有所帮助,欢迎点赞、转发、收藏、评论让更多人看到,赞赏支持就更好了。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?