IGBT发明者,新的目标

原创 导体行业观察 2024 年 09 月 23 日

IGBT 发明者 B. Jayant Baliga 因为发明 IGBT 获得了巨额奖金。在获奖采访中,B. Jayant Baliga 透露,一个名为 BiDFET 的器件是他们的新目标。现在我们将这个器件的介绍摘译如下。

以下为文章正文:

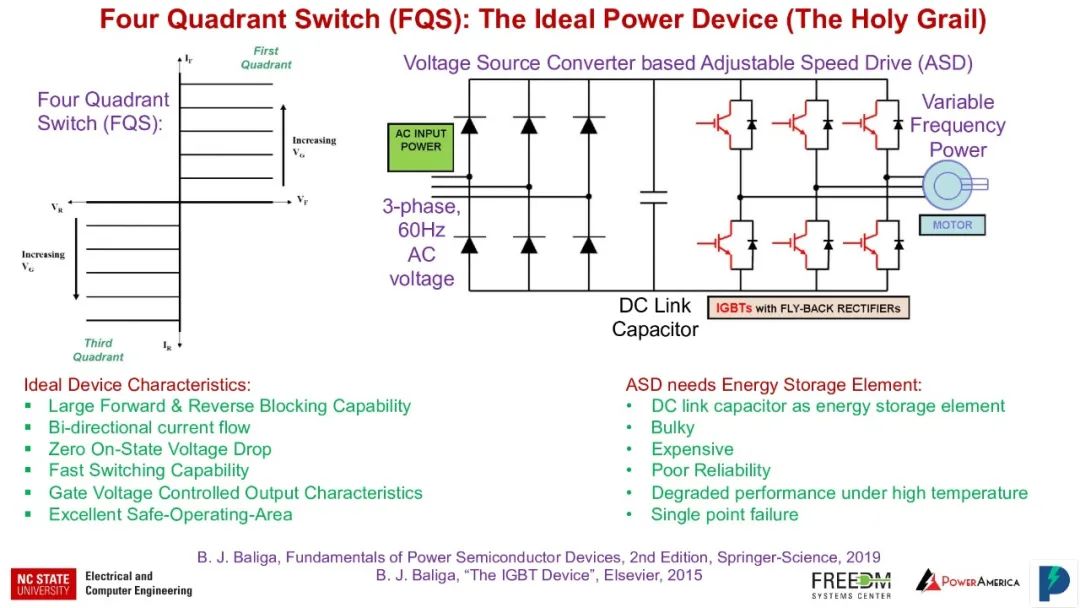

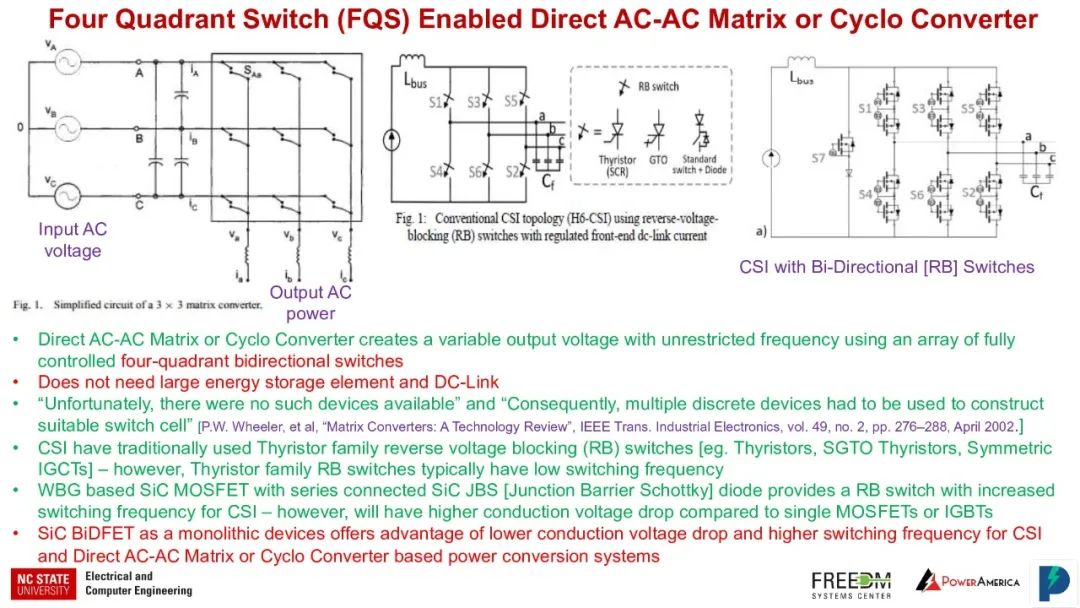

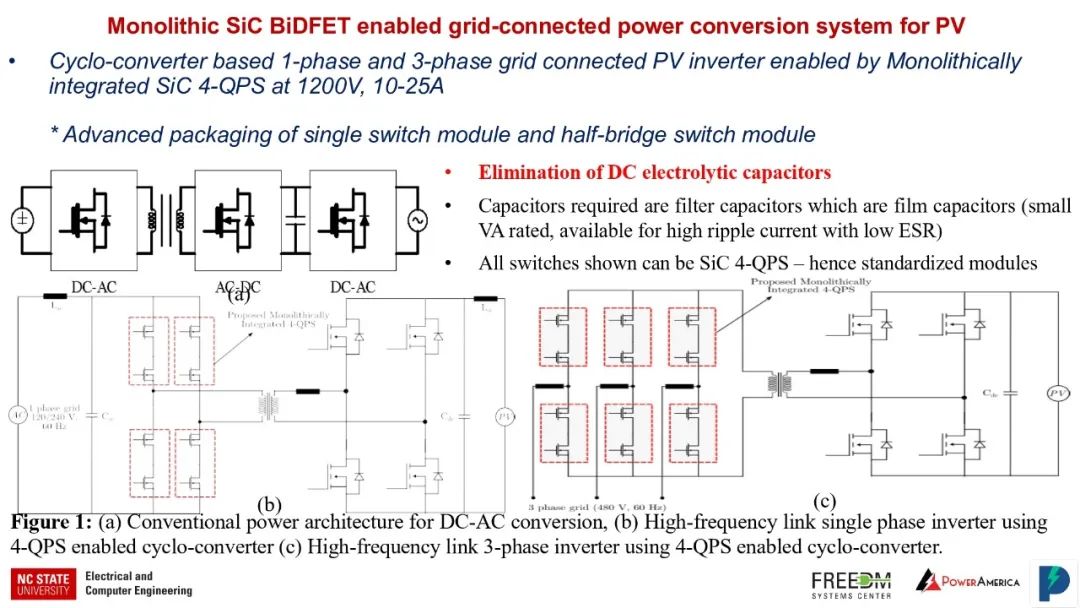

用于直接交流 - 交流转换的矩阵式转换器拓扑结构可省去带前端整流器的常用电压源逆变器 (VSI) 中使用的笨重且不可靠的直流链路电容器。由此产生的更紧凑、更高效的实施方案是光伏发电、电机驱动和储能系统等多种应用的理想解决方案。

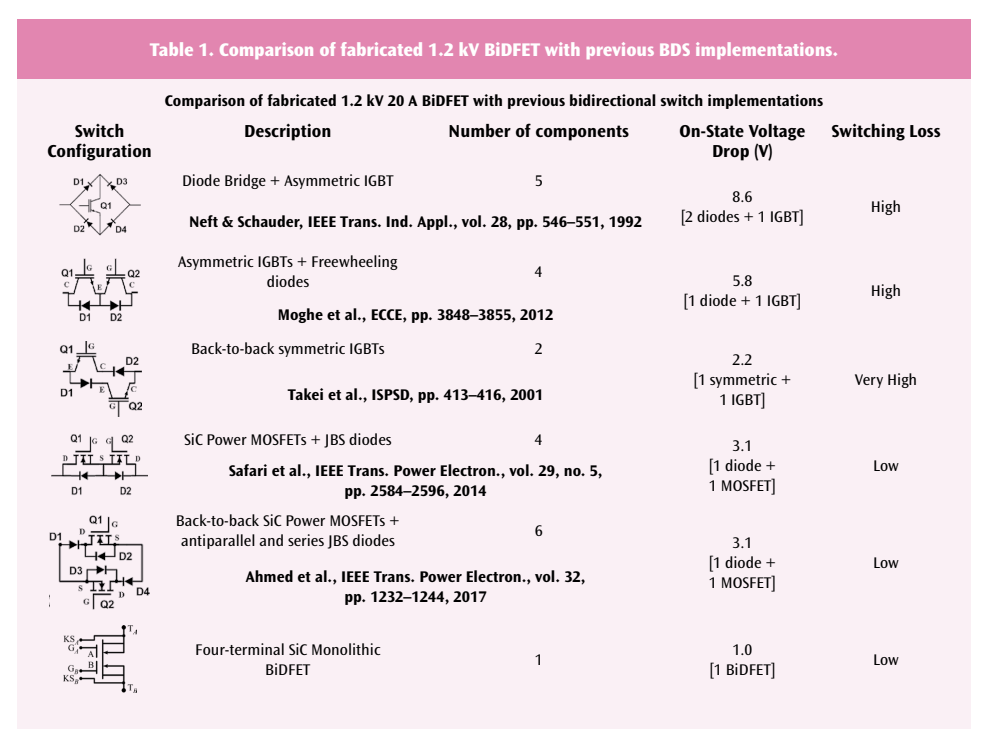

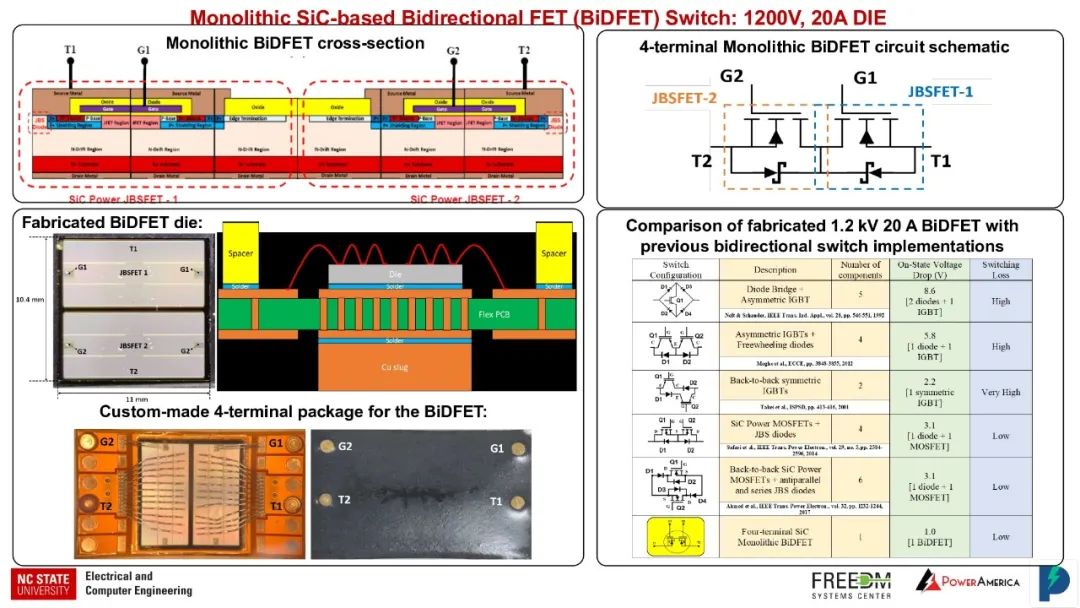

矩阵式转换器的发展一直受阻于缺乏商用双向电源开关,而这种开关能够在第一和第三象限阻断高电压,在两个象限以低压降承载导通电流,表现出较大的正向偏置安全工作区(FBSOA)和较低的开关功率损耗。因此,过去曾尝试过许多使用分立器件的实现方法,如表 1 所列。其中两种实施方案采用了常见的非对称闭锁 IGBT,还有两种方案采用了碳化硅功率 MOSFET。这些器件通常零件数量较多(4-6 个独立开关),在需要多个双向开关 (BDS) 的转换器中占据很大空间。它们的导通压降也很高,会降低效率。有一种方案利用对称闭锁 IGBT 实现了低零件数 (2),但其开关损耗高得令人无法接受。

第 1 代 BiDFET

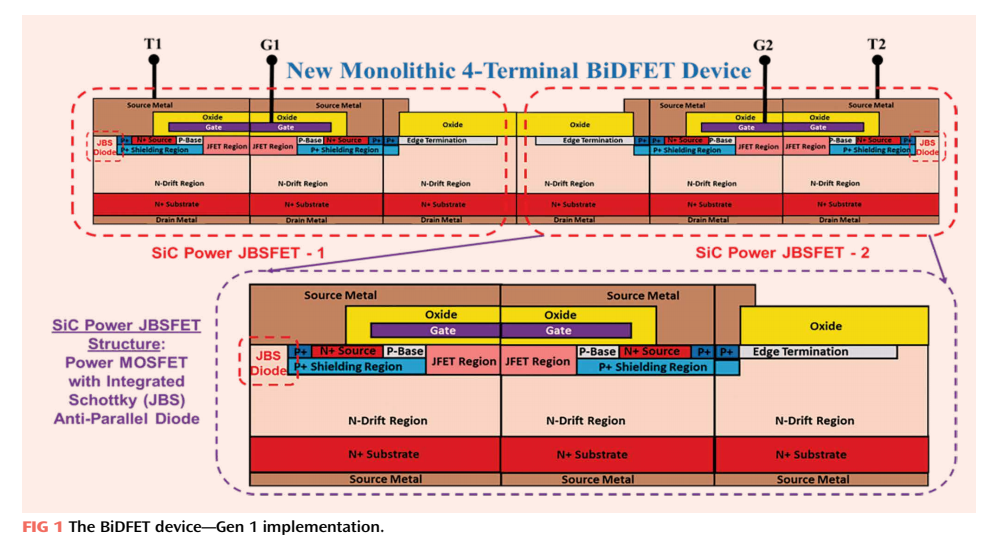

碳化硅(SiC)双向场效应晶体管(BiDFET)器件的提出[1]和开发,旨在为矩阵转换器创造一种导通压降和开关损耗都很低的单芯片四端双向器件。图 1 显示了 4 端子单片 SiC BiDFET Gen-1 器件的横截面。它在单个芯片中集成了两个相邻的 1.2 kV SiC JBSFET。JBSFET 是一种 MOSFET 结构,集成了一个 JBS 二极管,用于抑制第三象限体二极管的传导。JBSFET-1 和 JBSFET-2 的漏极通过公共 N+ 基底和背面金属化进行内部连接。

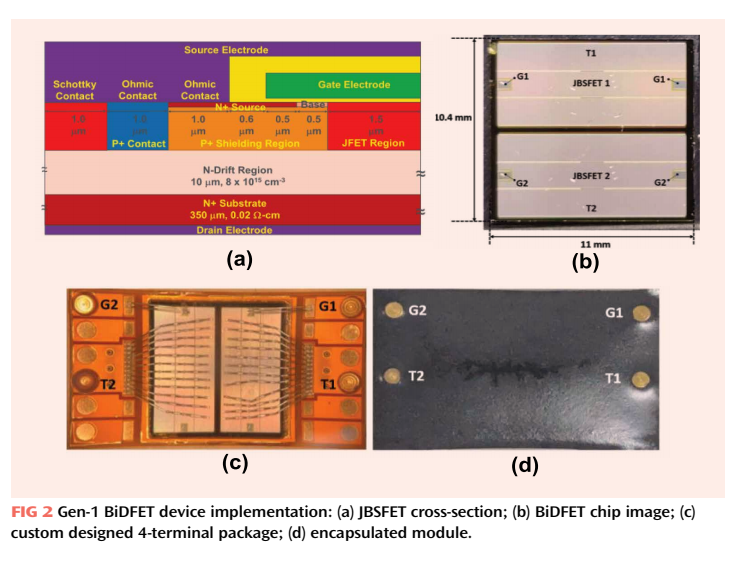

每个 JBSFET 单元都包含一个集成了 JBS 二极管的 MOSFET 部分。与典型的高压功率 MOSFET 一样,JBSFET 以垂直电流方式工作,确保有效区域内电流分布均匀。功率 MOSFET 本体二极管通过每个单元内集成的 JBS 二极管停用,以减少开关损耗并避免双极退化现象 [2]。两个 JBSFET 在每个象限都具有高电压阻断能力、低导通电阻、出色的 FBSOA 和快速开关性能。当栅极 G1 和 G2 与各自的端子 T1 和 T2 短接时,两个象限都能实现高电压阻断能力。当栅极偏压(通常为 20 V)施加到栅极 G1 和 G2 与端子 T1 和 T2 之间时,两个象限中都会产生导通电流,导通电阻较低。通过切换施加到 JBSFET1 的栅极偏压 G1,同时将栅极 G2 保持在导通栅极偏压状态,在第一象限进行功率切换。以同样的方式,通过切换施加到 JBSFET2 的栅极偏压 G2,并将栅极 G1 保持在导通栅极偏压状态,在第三象限执行功率开关。第一代(Gen-1)BiDFET 器件的设计采用了图 2(a)所示的 JBSFET 单元横截面。它的半单元宽度为 6.1 µm,以便在 MOSFET 单元内容纳 JBS 二极管。积放模式沟道的选择是为了获得 20 cm²/V-s 的迁移率,沟道长度为 0.5 µm,以尽量减少沟道电阻的影响。器件是在 n 型外延层上制造的,掺杂浓度为 8 × 1015 cm-3,厚度为 10 µm,利用混合-JTE 边缘终止技术 [8],实现了高于 1400 V 的阻断电压。

第 1 代 BiDFET 芯片的图像如图 2(b)所示,JBSFET1 位于顶部,JBSFET2 位于底部。芯片布局包含栅极母线,用于分配驱动电压,每个 JBSFET 有两个栅极焊盘,便于封装。由于 JBSFET 单元的特定导通电阻为 11.25 mΩ-cm²,因此选择了 0.45 cm²的有源面积,以实现 50 mΩ 的 BiDFET 总导通电阻。Gen-1 BiDFET 芯片尺寸为 1.04 cm × 1.10 cm。器件是在德克萨斯州 X-Fab 商业代工厂采用 NCSU PRESiCE 工艺技术制造的*[9]*。BiDFET 工艺技术与用于制造碳化硅功率 MOSFET 和 JBS 二极管的工艺技术类似,因此这些器件具有商业可行性。在晶圆级表征之后,第 1 代 BiDFET 芯片被安装在一个定制设计的模块中,如图 2(c)所示,在有源区有足够的导线键合,以将封装电阻降至 1 m`Ω 以下。图 2(d) 显示了封装后的 4 端子模块。

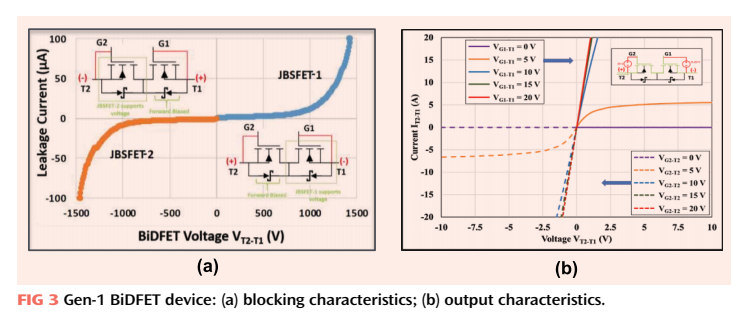

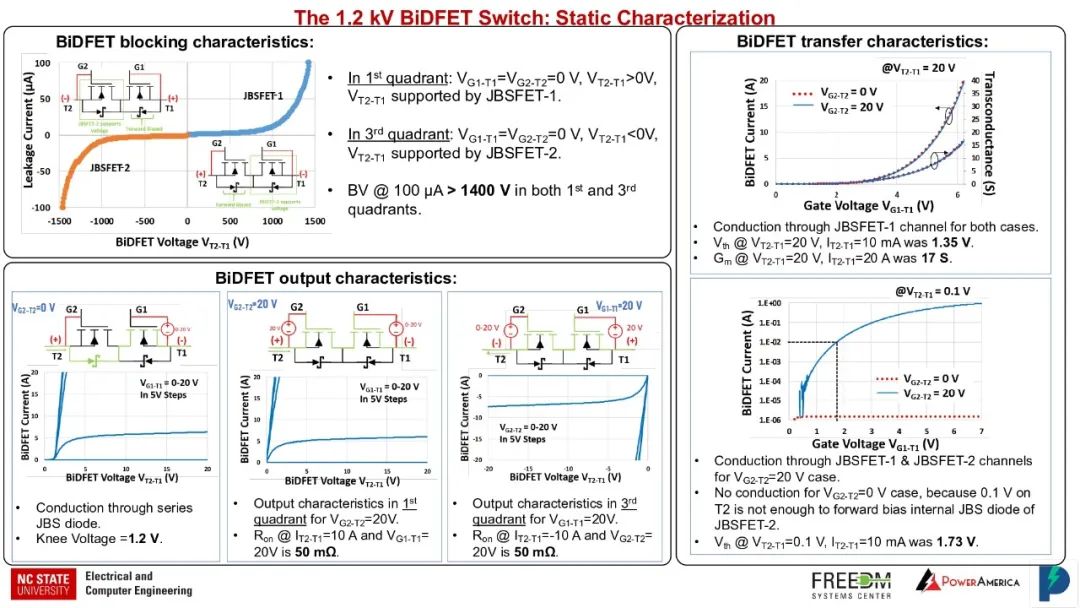

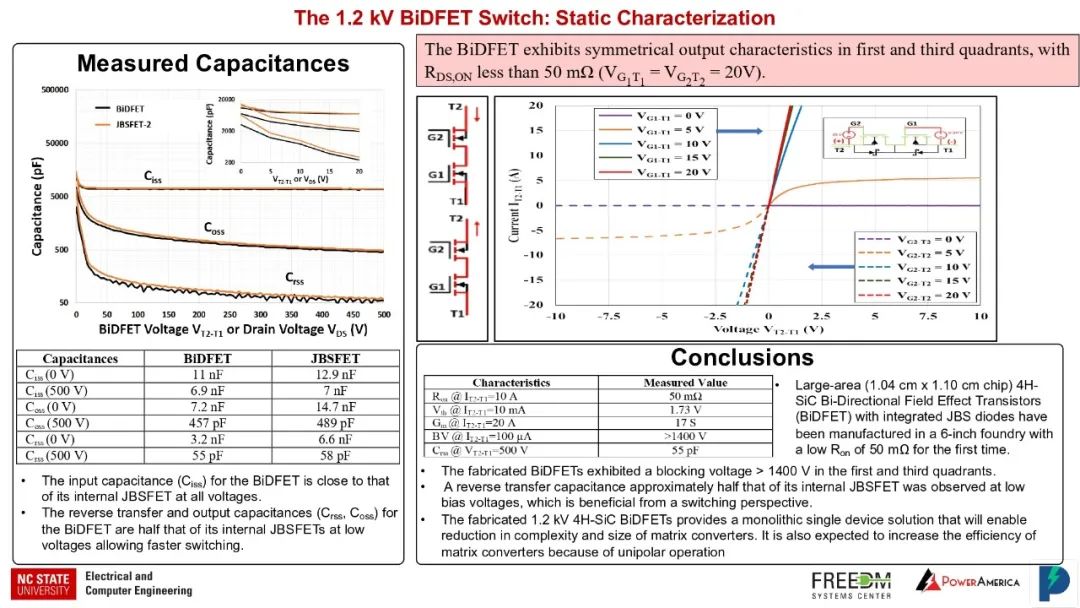

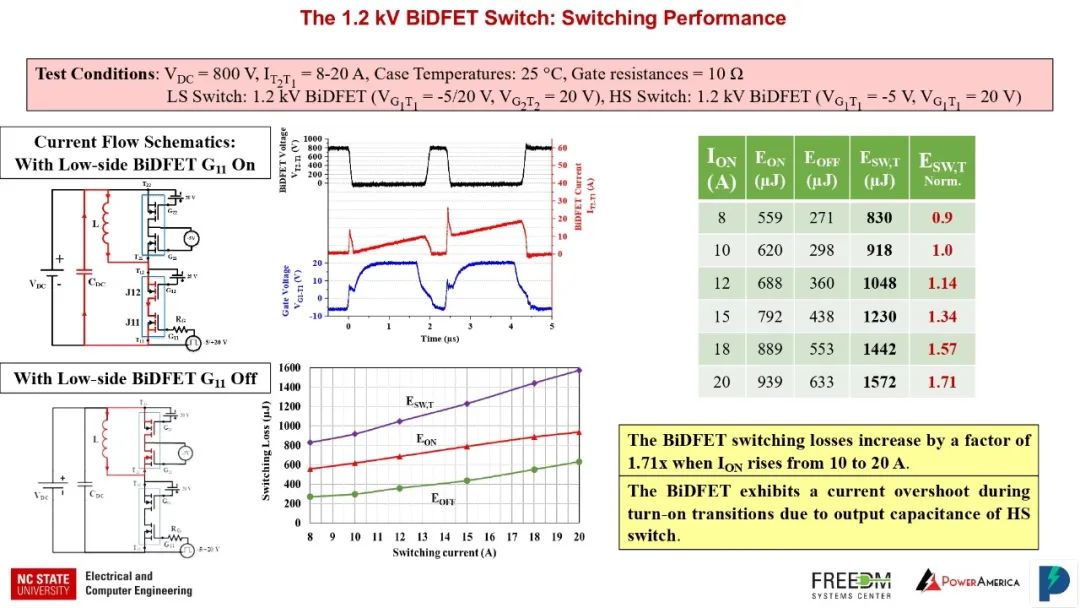

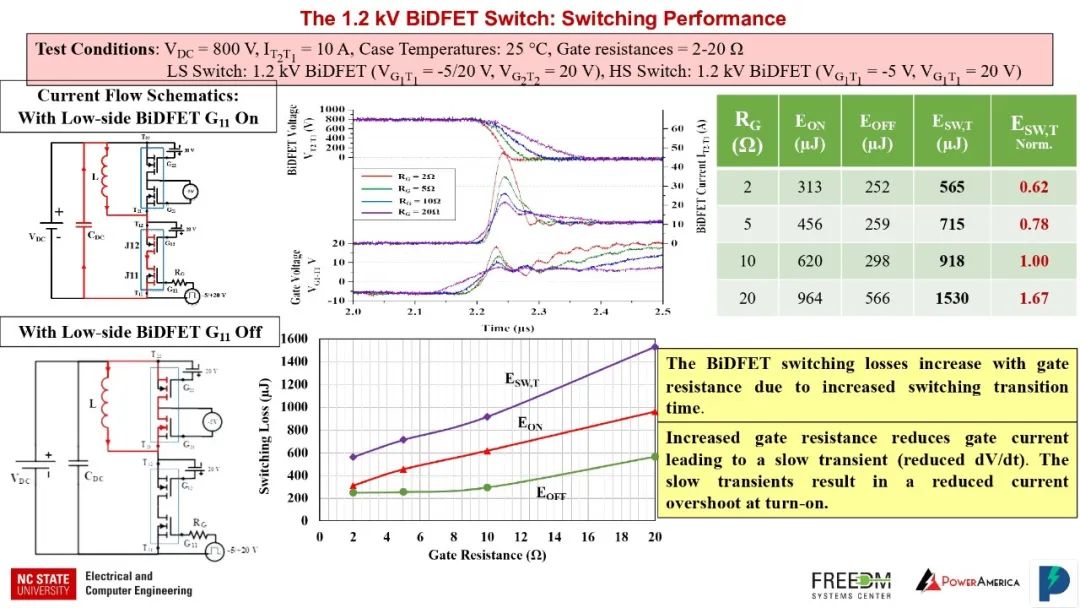

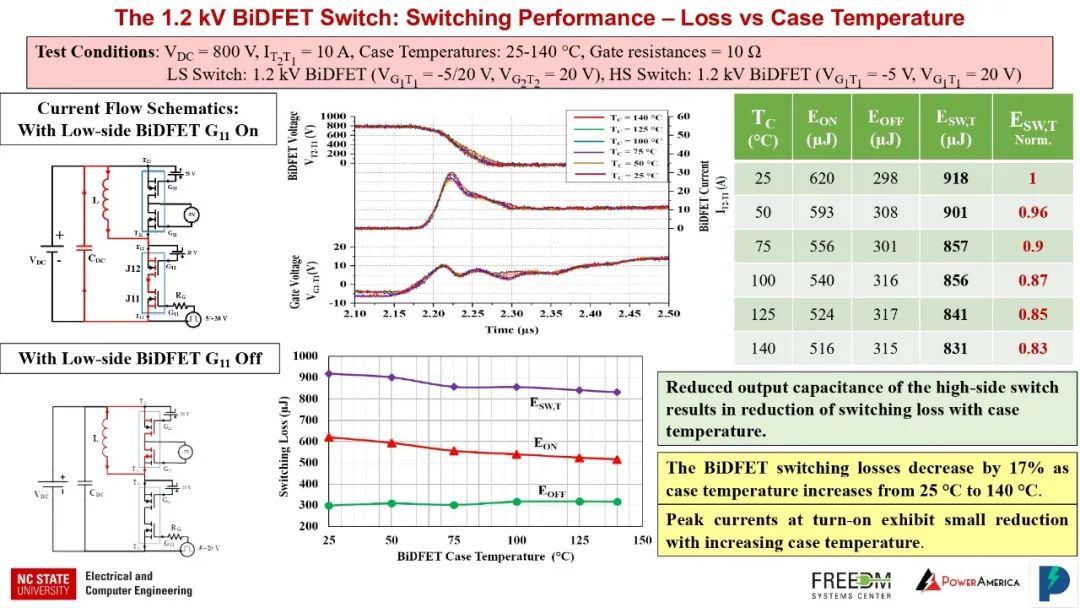

图 3(a) [3]显示了 25 ℃ 时测量到的 Gen-1 BiDFET 器件的阻塞特性。如插图中器件符号所示,当栅极 G1 和 G2 与各自的端子 T1 和 T2 短接时,器件在第一和第三象限均可支持超过 1.4 kV 的电压。JBSFET1 支持第一象限的电压,而 JBSFET2 支持第三象限的电压。如图 3(b) 所示,该器件在 25 ℃ 时具有理想的栅极电压控制输出特性,在较低的栅极偏置电压(如 5 V)下具有饱和漏极电流。在 25 ℃ 时,栅极偏置电压为 20 V,1 代 BiDFET 的总导通电阻为 50 m`Ω。该器件在漏极偏压为 1 V 时可处理 20 A 电流,与表 1 一致。集成 JBS 二极管的压降小于 2.5 V,以确保 MOSFET 体二极管的有效旁路 [2]。在漏极电源电压为 800 V、电流为 10 A 的条件下,通过对 BiDFET 器件进行双脉冲测试[4],得到的开通、关断和总开关损耗分别为 620、300 和 920 µJ。总开关损耗随着温度升高而降低,最高可达 140 ℃。

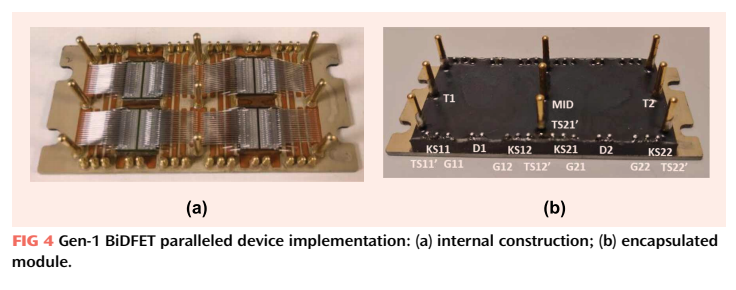

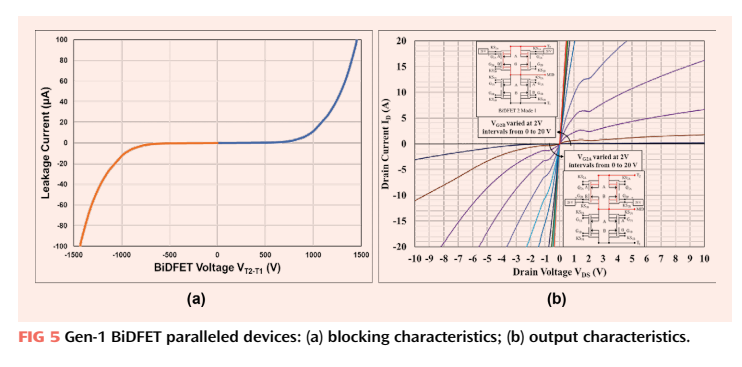

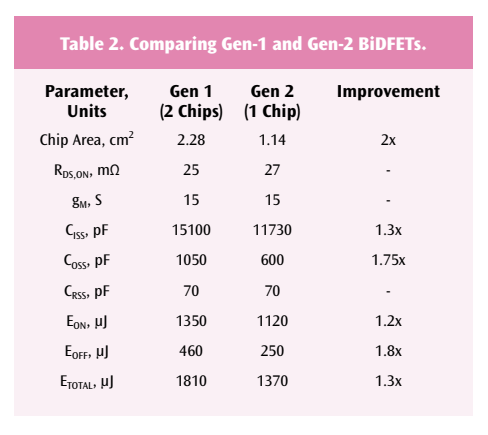

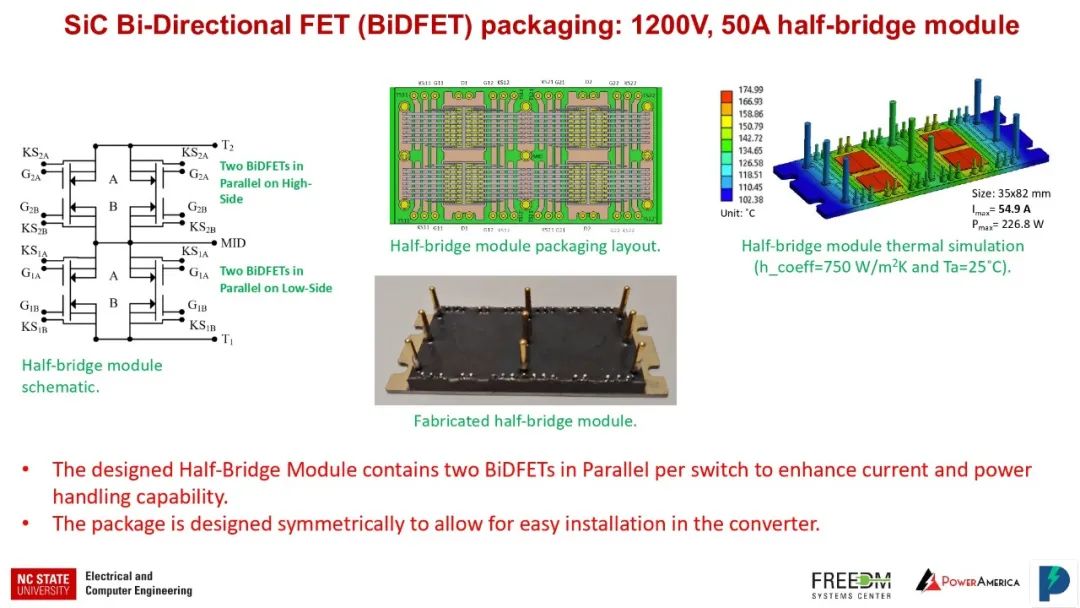

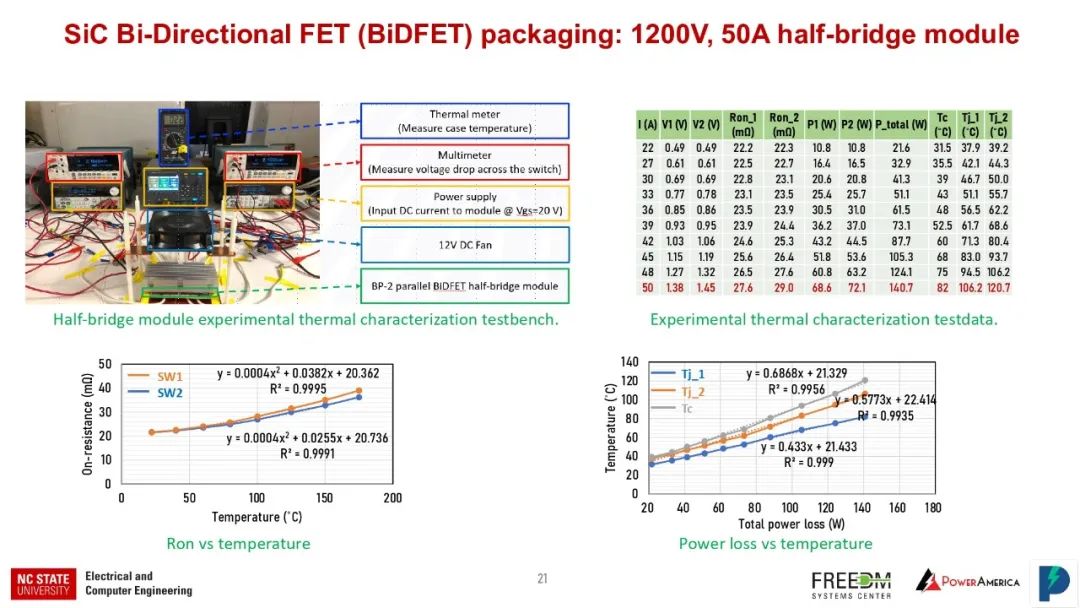

BiDFET 器件可以并联,以提高电流处理能力,用于更高功率的转换器。如图 4(a)所示,通过构建一个半桥模块,在上部和下部包含两个并联的 BiDFET 器件,可以证明这一点。封装模块如图 4(b)所示。第 1 代并联 BiDFET 器件在两个象限的测量阻塞特性如图 5(a)所示。当栅极 G1 和 G2 与各自的端子 T1 和 T2 短接时,器件在第一和第三象限均可支持超过 1.4 kV 的电压。如图 5(b) 所示,该器件具有理想的栅极电压控制输出特性。在 20 V 栅极偏压下,它的总导通电阻为 25 m´Ω,是单个 Gen-1 BiDFET 芯片的一半。在漏极电源电压为 800 V、电流为 20 A 的条件下,对并联 BiDFET 器件进行了双脉冲测试。提取的导通、关断和总开关损耗分别为 1350、460 和 1810 µJ,是单个 Gen-1 BiDFET 芯片的两倍左右。这些结果表明,并联 BiDFET 器件可以提高功率处理能力。

第二代 BiDFET

最近,通过创新的新型芯片设计和工艺技术,BiDFET 芯片的性能得到了大幅提升。Gen-1 芯片设计在 MOSFET 单元内集成了 JBS 二极管,从而产生了 6.1 µm 的大单元间距和较低的沟道密度。为了同时获得 MOSFET 与 N+ 和 P+ 区的欧姆触点,同时实现 JBS 二极管与漂移区的低漏电流肖特基触点,必须在 900 ℃ 下对镍触点进行退火处理*[2]*。这一过程产生的 N+ 源触点比电阻为 0.8 m´Ω-cm²。对 JBSFET 导通电阻的建模表明,由于单元间距大和源触点电阻高,总导通电阻显著增加 [5]。

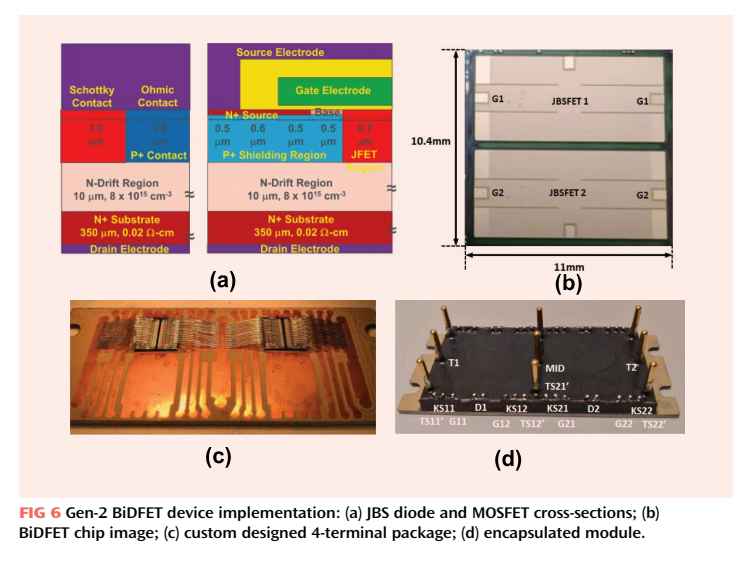

通过将 JBS 二极管从 MOSFET 单元中分离出来,并将其放置在芯片的四个角上,可以大大降低 Gen-2 BiDFET 器件中 MOSFET 单元的特定导通电阻。这样,MOSFET 单元的尺寸就可以减小到 2.8 µm,如图 6(a)右侧所示,从而使沟道密度提高了 2.2 倍。P+ 区域的触点与横截面呈正交,使单元间距更小。MOSFET N+ 源区的镍触点在 1000 ℃ 下退火,以将比接触电阻降至 0.05 m’Ω-cm2。经测量,采用这种设计和工艺制造的 MOSFET 单元的比导通电阻为 4.5 m’Ω-cm2,比 Gen-1 器件提高了 2.5 倍。为了确保 MOSFET 体二极管的有效旁路,JBS 二极管占用了 10% 的有源面积,同时保持了与触点相同的芯片面积。使用 Gen-2 BiDFET 制作的有源面积为 0.045 cm2 的 JBS 二极管测试元件(与 Gen-2 芯片中 JBSFET 内的 JBS 二极管的值相同)的导通压降小于 2.5 V,证实 BiDFET 中的 MOSFET 体二极管可以有效旁路。在其余 90% 的有源区域中,每个 JBSFET 的 MOSFET 单元的计算导通电阻为 12 m’Ω。因此,在保持芯片尺寸不变的情况下,新的芯片结构和工艺产生了导通电阻约为 25 m’Ω 的第 2 代 BiDFET 器件,是第 1 代器件的一半。这对 SiC BiDFET 来说是一项重大的技术改进,可将芯片成本和模块尺寸减半。第 2 代 BiDFET 芯片的图像如图 6(b)所示。芯片四个角上的 JBS 二极管区域是可见的 Gen-1 器件。由于金属纹理的细微差别,JBS 二极管的钛触点是单独制作的,以实现肖特基。第 2 代 BiDFET 芯片封装在为第 1 代并联器件设计的相同半桥模块中,如图 6© 所示,占用一半空间。封装模块如图 6(d)所示。

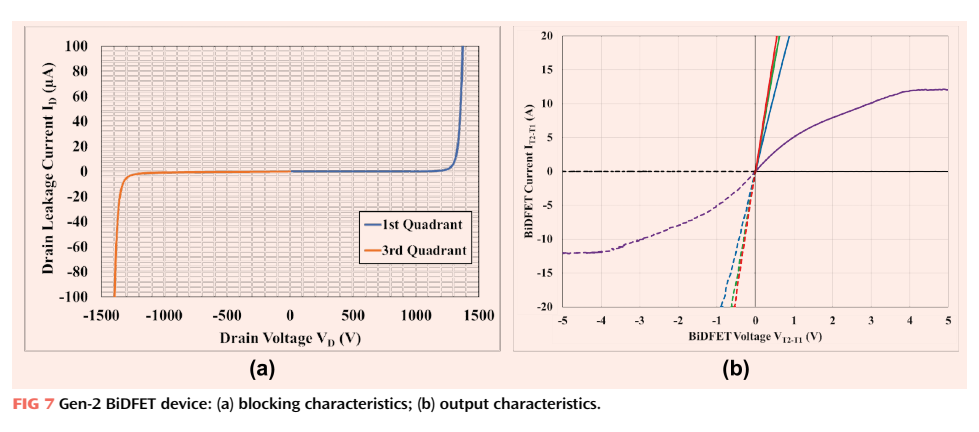

图 7(a) 显示了第 2 代 BiDFET 器件在两个象限的测量阻塞特性。当栅极 G1 和 G2 与各自的端子 T1 和 T2 短接时,该器件在第一和第三象限均可支持 1.4 kV 的电压。如图 7(b)所示,该器件具有理想的栅极电压控制输出特性,在较低的栅极偏置电压下具有饱和漏极电流。在 20 V 栅极偏置电压下,该器件的总导通电阻为 27 m’Ω,接近设计值。在漏极电源电压为 800 V、电流为 20 A 的条件下,对 Gen-2 BiDFET 器件进行了双脉冲测试。这些值小于并联的第一代 BiDFET 器件。

先进的封装方法

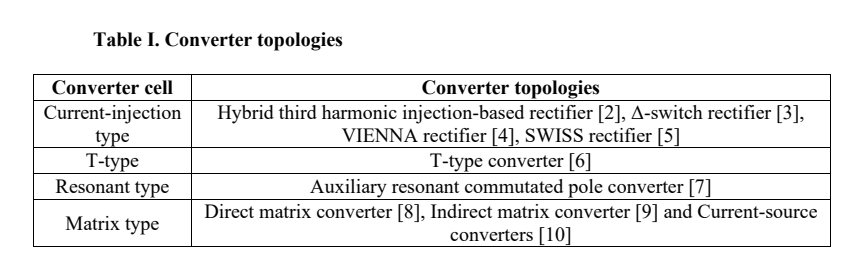

这项研究的目标是在恶劣环境中运行的低成本、可靠的转换器,首选对流冷却。由于 BiDFET 的损耗非常低,因此采用了先进的替代封装方法。研究人员对使用超薄环氧树脂复合电介质(ERCD)替代使用平板陶瓷的传统 DBC 进行了比较。RISHO KOGYO Co. Ltd. 最近推出的 ERCD 材料具有 10 W/mK、40 kV/mm B.V.、53 Gpa 模量、工作温度 ≤300 °C 和 120 µm 厚度的特点。该材料可作为金属化薄膜、层压材料或覆在厚铜上以形成绝缘金属基板。使用有机方法可使高端印刷电路板公司在大幅降低成本和缩短周转时间的情况下加工金属化基板或完整模块。

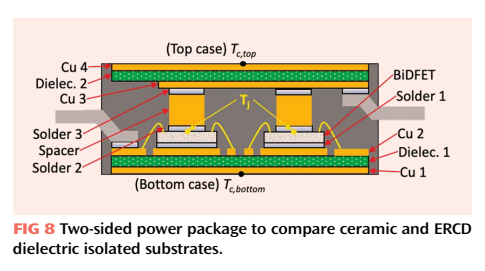

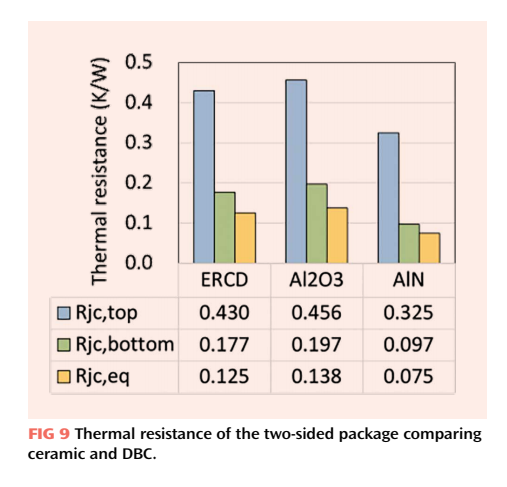

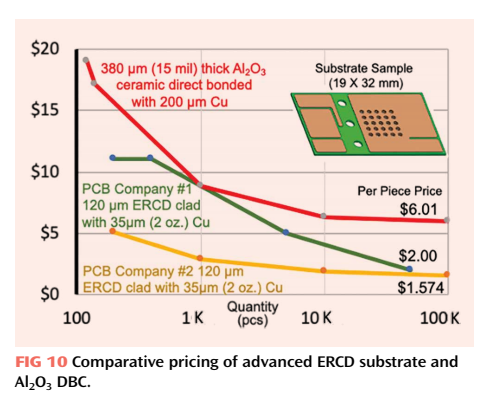

为了比较陶瓷和 ERCD,我们设计了一个双面模块结构(图 8),并在 ANSYS 中进行了模拟,如文献 [6] 所述。安装并封装了两个 SiC 芯片,以允许热量从两个表面流出。假定垫片覆盖芯片面积的 60%。对于双面结构,考虑了陶瓷和 ERCD 的顶部和底部电介质的四种可能组合,并进一步考虑了 Al2O3 和 AlN 两种陶瓷。陶瓷的厚度为 380 微米,覆有 127 微米的铜,ERCD 的厚度为 120 微米,覆有 100 微米的铜。Al2O3、AlN 和 ERCD 的导热系数分别为 24、170 和 10 W/mK。热阻的比较结果如图 9 所示,显示出 ERCD 的 Rjc,eq 比 Al2O3 高 10%。虽然 ERCD 的电导率较低,但其厚度较薄,因此电导率较高。由于成本问题,而且使用 ERCD 的功率耗散能力完全符合项目要求,因此可以避免使用成本更高的氮化铝和陶瓷工艺。由于成本是重中之重,因此我们向三家供应商提供了 19 毫米 × 32 毫米的示例基底,供其定价。图 10 显示,ERCD 方法的成本仅为 Al2O3 DBC 的三分之一或更低。如上段所述,ERCD 的额定连续工作温度高达 300 °C。BiDFET 的过温不会明显影响成本比较,可靠性问题主要是 DBC 和 ERCD 的芯片附着问题。

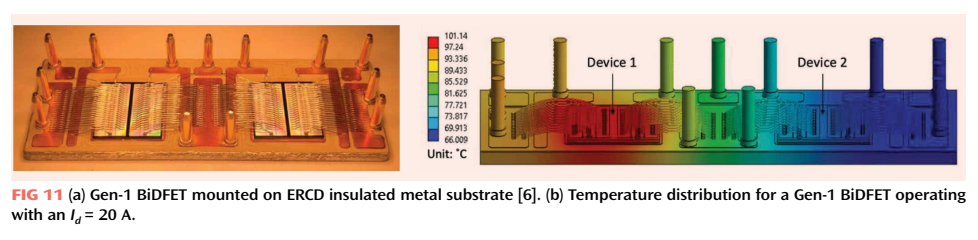

如图 11(a) 所示,第一代 BiDFET 非封装单面模块将芯片安装在 ERCD 绝缘金属基板 (eIMS) 上 [6]。ANSYS 热分析(图 11(b))显示,在 ID = 20 A 的传导冷却条件下,66 °C 环境中的最坏情况温度为 101 °C。

对转换器的影响

四象限开关可实现矩阵式转换器拓扑结构,其运行不需要笨重的电感器或电解电容。然而,这种转换器在商业上并不流行主要原因是器件数量多于电压源转换器。要了解 BiDFET 的发明对此类转换器商业可行性的影响,可以考虑 BiDFET 对可靠性、尺寸和效率这三个转换器性能指标的影响。

转换器的可靠性取决于元件的数量和每个元件的可靠性。BiDFET 可以取代使用多个分立器件的四象限开关实施方案,这不仅减少了每个转换器的器件数量,还减少了不可靠的接线数量。与基于分立器件的四象限开关相比,单片器件显然需要更少的空间。开关的尺寸减小,封装更简单,因此电感换向回路更小,同样的 di/dt 转换,过电压更低,或者同样的过电压,di/dt 转换更快。器件的开关损耗通常会随着 di/dt 转换速度的加快而降低。

此外,与 MOSFET 相比,构成 BiDFET 的 JBSFET 具有许多优势。由于 JBS 二极管的反向恢复电荷比 MOSFET 的 Pi-N 体二极管低得多,因此 JBSFET 的导通损耗更低,在温度变化时的总开关损耗几乎保持不变。此外,JBS 二极管的存储电荷或反向恢复时间几乎不随死区时间的变化而变化,因此导通电流峰值较小,从而允许更快的 dv/dt 转换,这进一步降低了器件的开关损耗。

根据转换器的调制方案,BiDFET 的一个成分 FET 可能比另一个成分 FET 的电流导通时间更长或开关更频繁。例如,在单相矩阵转换器中,一个组成场效应晶体管在整个正交流半周期内保持导通,而另一个则在负交流半周期内进行调制,反之亦然。BiDFET 中这些组成 FET 的温度循环范围要比四象限开关实施中的分立器件窄。由于 BiDFET 的单片性质,一个 FET 的损耗也会使另一个 FET 发热。器件温度周期的缩短将进一步提高其可靠性。这一现象有望为输出频率较低 [如 < 10 Hz] 的电机驱动应用带来显著优势。

因此,BiDFET 器件在高效、功率密度高和可靠的矩阵转换器方面具有巨大潜力,在某些应用中从根本上优于电压源转换器。通过使用 BiDFET 器件,电流源转换器、T 型电压源转换器、维也纳整流器、基于三次谐波注入的混合整流器、辅助谐振换向极逆变器和其他利用四象限开关的转换器的性能也能得到改善。通过 800 V、20 A 的开关测试 [4],以及单相隔离交流-直流转换器硬件在 2.3 kW、400 VDC 输入和 277 VRMS 输出条件下的连续运行 [7],BiDFET 芯片和封装的运行已得到成功验证。

采用碳化硅 BiDFET 器件的功率转换系统

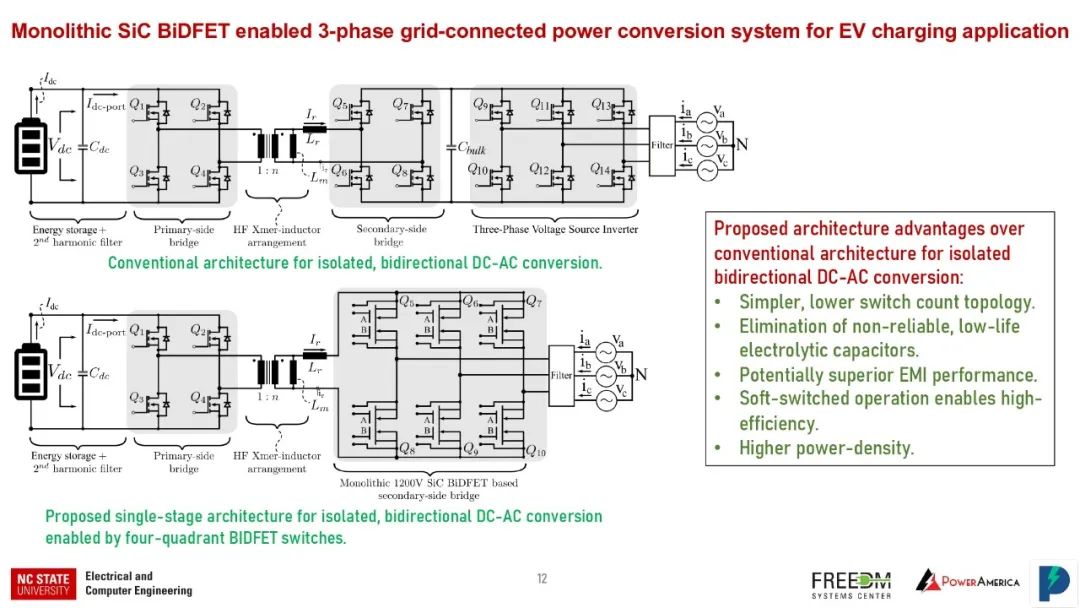

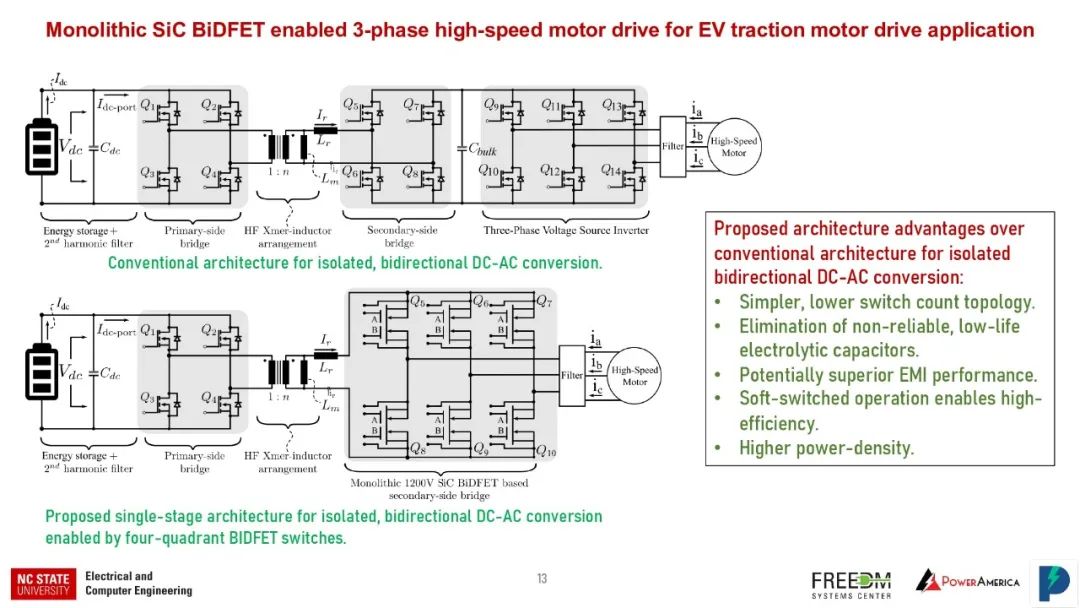

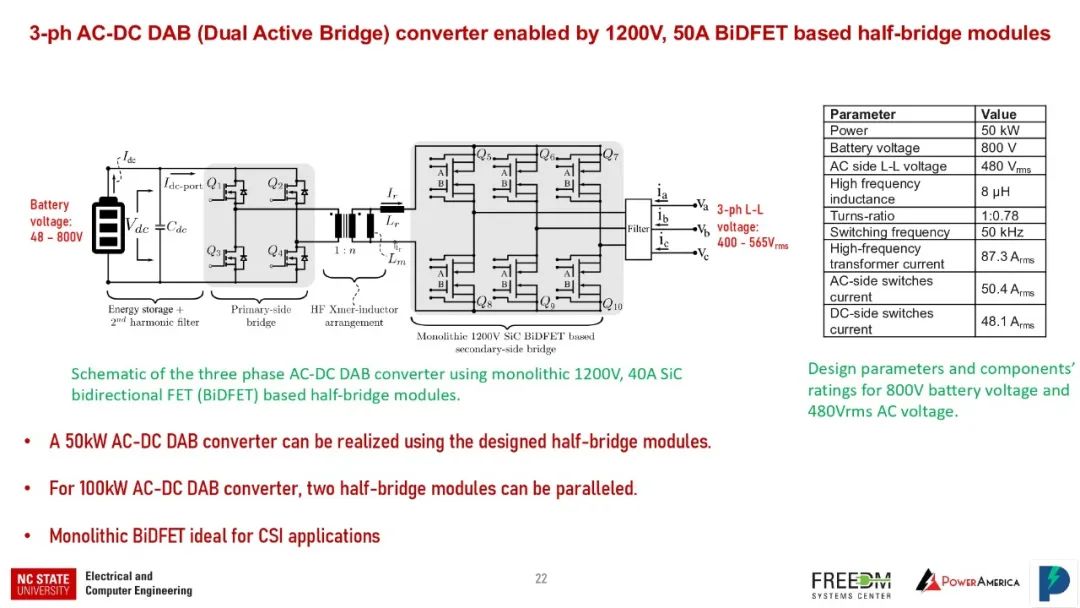

双向场效应晶体管 (BiDFET) 可实现需要四象限开关的电路拓扑结构,而这些电路拓扑结构在早期的设计中使用的是 MOSFET、IGBT、GaN HEMT 和 PiN 二极管的离散组合。BiDFET 的单片特性允许更少的器件数量、更小的开关体积、更低的电感和更简单的封装,因此在电力电子转换器中的应用更可靠、更具商业可行性。使用 BiDFET 现在可行的矩阵转换器拓扑结构可以消除交流-交流和交流-直流应用中传统电压源或电流源转换器所需的笨重且不可靠的直流链路电容器或电感器。1.2 kV BiDFET 有可能颠覆所有使用 1.2 kV 开关的应用,包括电动汽车 (EV) 传动系统、双向电动汽车充电器、工业电机驱动器、固态变压器、数据中心电源、电梯驱动器、直流微电网、储能电网集成、固态断路器等。

使用 BiDFET 的转换器拓扑

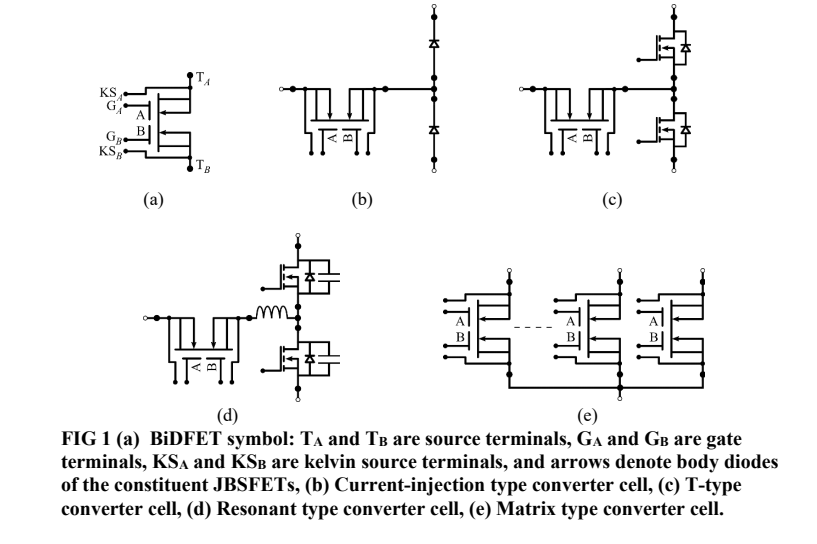

使用 BiDFET 实现的转换器拓扑结构可通过识别用于实现这些拓扑结构的转换器单元来进行分类。图 1(b) - (e) 显示了四种不同的使用 BiDFET 的转换器单元,表 I 列出了与每种转换器单元相对应的流行转换器拓扑。

BiDFET 器件是作为单片四端开关制造的,由两个内部 1.2 kV 4H-SiC JBS(结势垒肖特基)-二极管嵌入式功率 MOSFET(JBSFET)组成,以共漏配置连接*[1]*。任何四象限开关(包括背靠背连接的 SiC MOSFET)都需要至少四个半导体器件才能实现相同的功能。BiDFET 作为单片式四象限开关,由于器件数量较少,不需要线键,最终封装尺寸也较小,因此可以实现具有较小电感换向单元的转换器。

使用 1.2 kV SiC BiDFET 的首个转换器硬件演示

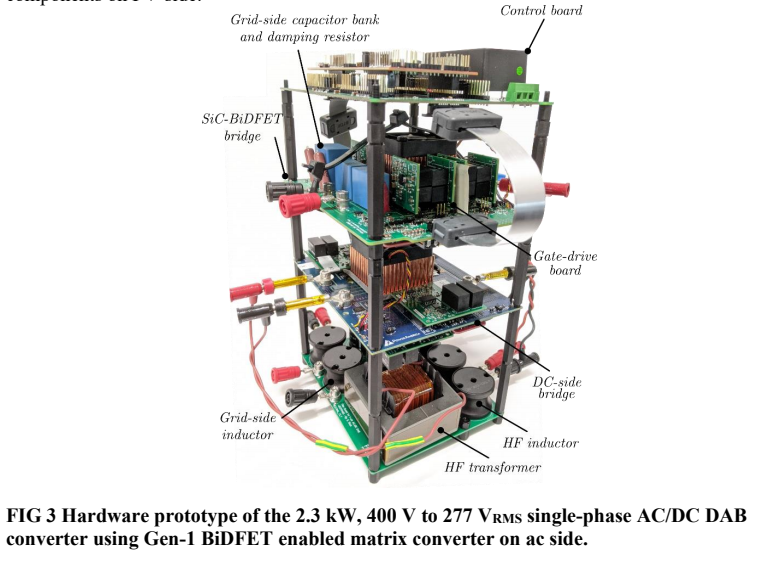

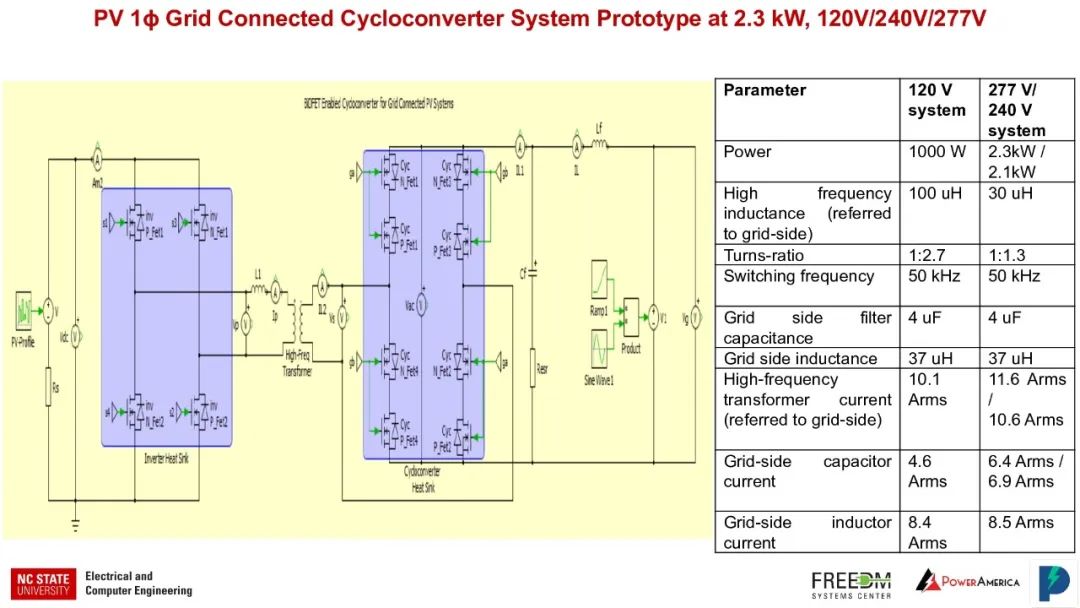

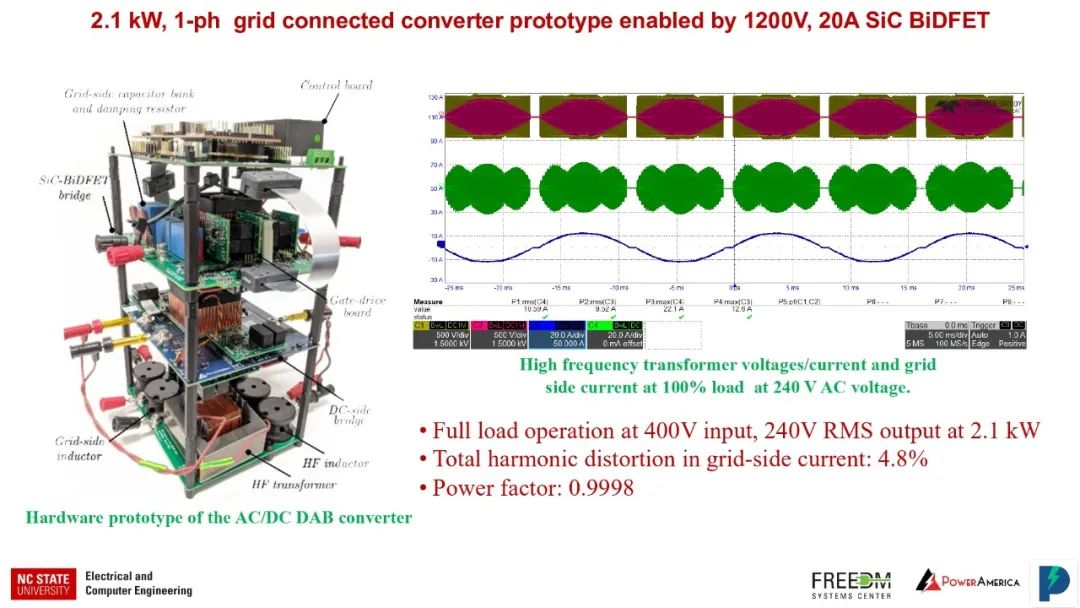

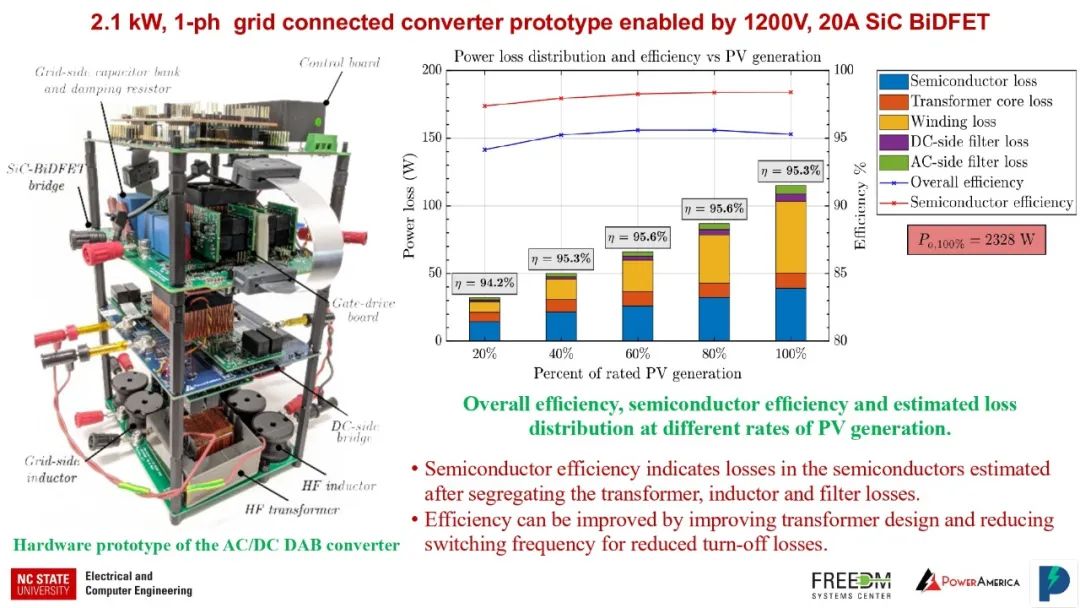

针对太阳能光伏应用,我们设计、开发并实现了一种单相、单级、隔离式交流-直流转换器,该转换器在电网侧采用了启用 BiDFET 的单相矩阵转换器*[11]*(图 2)。这种启用了 BiDFET 的转换器与传统的交流-直流隔离转换器相比,有了显著的改进,传统的交流-直流隔离转换器采用 PWM 逆变器级联的直流-直流双有源桥 (DAB),或使用笨重、不可靠的电解电容的文件夹-解文件夹级联和直流链路。所开发的转换器只需较少数量的开关,无需电解电容,是一种体积更小、可靠性更高的解决方案。硬件原型由四块印刷电路板堆叠而成(图 3)。最上面的 PCB 是控制板,负责提供辅助电源、接受传感器信号、生成 PWM 栅极信号,并通过硬件和软件跳闸设置保护转换器免受故障影响。第二块 PCB 板是电网侧全桥转换器,由 1.2 kV 第 1 代 SiC BiDFET 和滤波电容器 Cf 以及同一块板上的并联 Rf - Cb 阻尼支路供电。第三块 PCB 板是光伏侧全桥转换器,由 650 V GaN Systems 的增强型 GaN 晶体管(GS66516T)供电。第四块 PCB 板是滤波器和高频交流链路板,包括电网侧电感器 Lf/2、光伏侧二次谐波滤波电容器 Cdc、高频电感器 Lr 和高频变压器。滤波器 PCB 靠近光伏侧全桥转换器 PCB,因为它包含了光伏侧线路频率二次谐波滤波元件所需的电容器 Cdc。

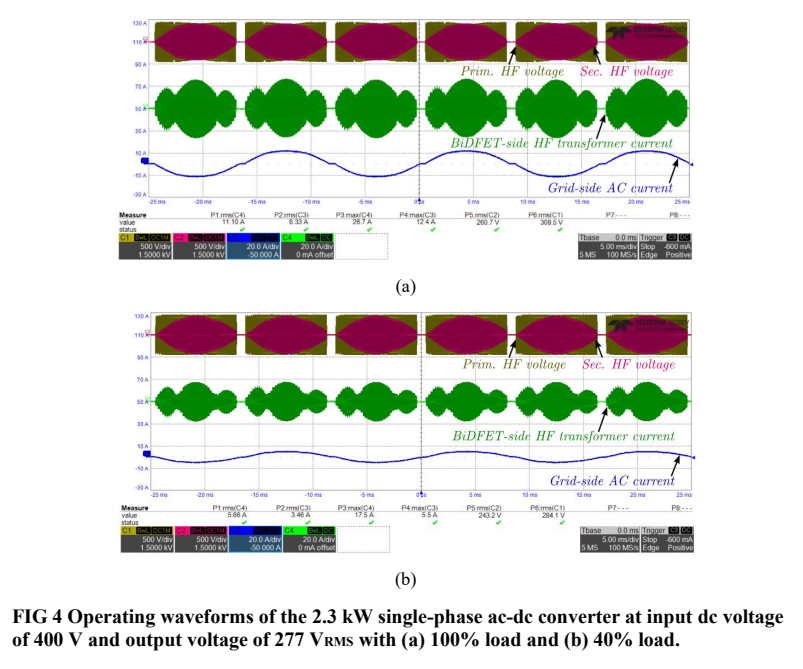

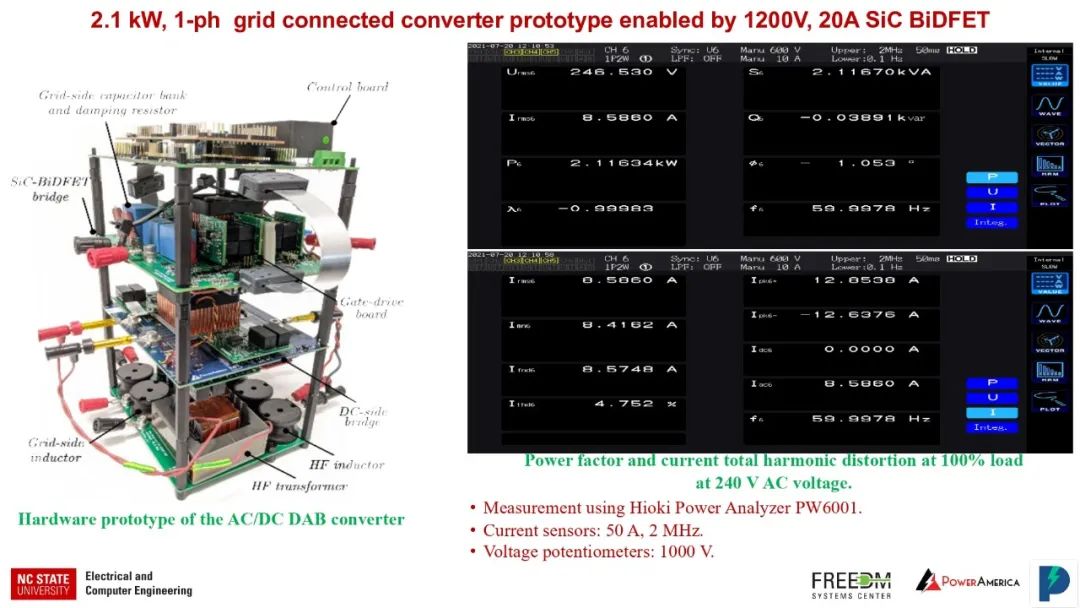

为了优化转换器设计和调制方案,我们采用了一种包含交流-直流 DAB 转换器所有调制策略和工作模式的算法。它利用三个自由度(直流侧全桥转换器输出占空比、交流侧全桥转换器输出占空比、直流侧和交流侧全桥输出之间的相移),优化了转换器的高频均方根电流、磁性元件尺寸和软开关区域。图 4 显示了 40% 和 100% 负载时的硬件实验结果。交流输出电流过零点附近的死区时间确保了 BiDFET 组成场效应晶体管的安全换向。即使存在过零失真,用 Hioki 功率分析仪 PW6001 在转换器输出端测量到的 100%负载时的总功率因数和电流总谐波失真(THD)分别为 0.999 和 4.7%。为进一步改善电流总谐波失真,可采用矩阵转换器使用的基于电压或电流的四步换向方案来降低零交叉失真。

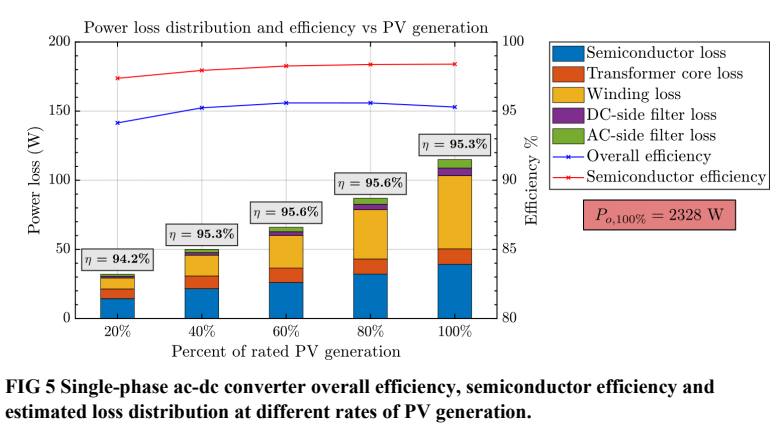

图 5 显示了所测得的转换器跨负载效率以及不同组件的估计损耗分布。这些损耗包括半导体、变压器铁芯、变压器和高频电感器绕组、直流侧滤波电容器(高频和低频损耗)以及交流侧滤波电容器中的损耗。在该原型中,变压器和电感器采用实心线绕组,因此绕组损耗在总损耗中占很大比例。如果磁性元件使用荔枝线绕组,则可以提高转换器的效率。假设除半导体损耗外的所有损耗均为零,则还绘制了称为 “半导体效率 ”的转换器效率指标,以标明所选半导体元件的最大可能效率。在 2.3 kW、400 VDC 输入和 277 VRMS 输出电压、50 kHz 开关频率条件下,电流总谐波失真(THD)、总效率和半导体效率分别为 4.7%、95.3% 和 98.4%。在栅侧全桥转换器中用 Gen-2 BiDFET 替代 Gen-1 BiDFET,可进一步提高转换器的半导体效率。Gen-2 BiDFET 的导通电阻为 25 mΩ,约为 Gen-1 BiDFET 的一半,而由于芯片尺寸相同,两种器件的开关损耗几乎相同。使用基于第 2 代 BiDFET 的栅侧全桥单相交流-直流转换器的半导体效率估计可提高 0.2%。使用第 1 代和第 2 代 BiDFET 器件的转换器半导体效率差异将随着器件工作电流水平的增加而增大,也就是说,当器件的传导损耗比器件的开关损耗更为显著时,半导体效率差异将增大。

结论

BiDFET 作为单芯片 SiC 四象限开关的开发,为实现基于可靠的 1.2 kV 四象限开关的功率转换系统铺平了道路。根据冷却方法和所需的转换器效率,最近开发的第 2 代 BiDFET(导通电阻为 25 mΩ)可实现多千瓦的应用。2.3 kW、400 VDC 输入和 277 VRMS 输出单相隔离式 AC/DC 转换器的实验结果表明,SiC BiDFET 器件可以连续工作。

附:BiDFET器件介绍

关于作者

B. Jayant Baliga(电气和电子工程师学会会员)是美国北卡罗来纳州罗利市北卡罗来纳州立大学(NCSU)电气和计算机工程专业的进步能源杰出大学教授。他是美国国家工程院院士。他撰写/编辑了 22 本著作和 700 多篇科学论文,获得 122 项美国专利。他于 2011 年获得奥巴马总统颁发的国家技术与创新奖章,2014 年获得电气和电子工程师学会荣誉奖章,2015 年获得全球能源奖,2016 年作为 IGBT 的唯一发明人入选美国国家发明家名人堂。

道格拉斯-霍普金斯是美国北卡罗来纳州罗利市北卡罗来纳州立大学(NCSU)电气与计算机工程系教授。他还是电子能源系统封装研究实验室(PREES)主任,该实验室是美国国家科学基金会 FREEDM 系统中心的一部分,同时也是快速成型制造和物流中心(CAMAL)的附属学院成员。他拥有 20 多年的学术和工业经验,主要研究高频、高密度电力电子器件,重点是封装。

Aditi Agarwal 是美国加利福尼亚州埃尔塞贡多纳维塔斯半导体公司的功率器件科学家。

Tzu-Hsuan Cheng 目前正在美国北卡罗来纳州罗利市的北卡罗来纳州立大学攻读博士学位。

Ramandeep Narwal 目前正在美国北卡罗来纳州罗利市的北卡罗来纳州立大学攻读博士学位。

Ajit Kanale 目前正在美国北卡罗来纳州罗利市的北卡罗来纳州立大学攻读博士学位。

Suyash Sushilkumar Shah 在美国北卡罗来纳州罗利市的北卡罗来纳州立大学获得电气工程博士学位。他曾在北卡罗来纳州立大学国家科学基金会 FREEDM 系统中心担任博士后研究员,期间开发了单相交流-直流 DAB 转换器。

Kijeong Han 获得美国北卡罗来纳州罗利市北卡罗来纳州立大学电气工程博士学位。他是美国北卡罗来纳州 Cree Wolfspeed 公司的 SiC 功率器件设计工程师。

参考链接

[1] B. J. Baliga, “Monolithically-integrated AC switch having JBSFETs there in with commonly connected drain and cathode electrodes,” U.S. Patent 10 804 393, Oct. 13, 2020.

[2] W. Sung and B. J. Baliga, “Monolithically integrated 4H-SiC MOSFET and JBS diode (JBSFET) using a single ohmic/Schottky process scheme,” IEEE Electron Device Lett., vol. 37, no. 12, pp. 1605–1608, Dec. 2016.

[3] K. Han et al., “Monolithic 4-terminal 1.2 kV/20 a 4H-SiC bi-directional field effect transistor (BiDFET) with integrated JBS diodes,” in Proc. IEEE Int. Symp. Power Semiconductor Devices ICs (ISPSD), Sep. 2020, pp. 242–245.

[4] A. Kanale et al., “Switching characteristics of a 1.2 kV, 50 mΩ SiC mono lithic bidirectional field effect transistor (BiDFET) with integrated JBS diodes,” in Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC), Jun. 2021, pp. 1267–1274.

[5] A. Agarwal and B. J. Baliga, “Optimization of linear cell 4H-SiC power JBSFETs: Impact of N+ source contact resistance,” Power Electron. Devices Compon., vol. 2, Jun. 2022, Art. no. 100008, doi: 10.1016/j.pedc.2022.100008. [6] T.-H. Cheng et al., “Thermal and reliability characterization of an epoxy resin-based double-side cooled power module,” J. Microelectron. Electron. Packag., vol. 18, no. 3, pp. 123–136, Jul. 2021.

[7] S. S. Shah et al., “Optimized AC/DC dual active bridge converter using monolithic SiC bidirectional FET (BiDFET) for solar PV applications,” in Proc. IEEE Energy Convers. Congr. Expo. (ECCE), Oct. 2021, pp. 568–575, doi: 10.1109/ECCE47101.2021.9595533.

[8] W. Sung and B. J. Baliga, “A near ideal edge termination technique for 4500V 4H-SiC devices: The hybrid junction termination extension,” IEEE Electron Device Lett., vol. 37, no. 12, pp. 1609–1612, Dec. 2016, doi: 10.1109/ LED.2016.2623423.

[9] B. J. Baliga, “Third generation PRESiCETM technology for manufacturing SiC power devices in a 6-inch commercial foundry,” IEEE J. Electron Devic es Soc., vol. 8, pp. 1111–1117, Sep. 2020, doi: 10.1109/JEDS.2020.3014568.

END

IGBT发明者,获巨额奖金

原创 半导体行业观察 2024年09月09日 09:10 安徽

据报道,2024 年千年技术奖(2024 Millennium Technology Prize)授予了北卡罗来纳州立大学班特瓦尔·贾扬特·巴利加(Bantval Jayant Baliga)教授,以表彰其发明了绝缘栅双极晶体管 (IGBT)。

自 20 世纪 80 年代开发以来,IGBT 已成为风能、太阳能等高压可再生能源应用以及消费和工业用途的电动汽车和电动机的关键。

该项价值100万欧元的全球技术奖由芬兰技术学院监督,于2004年首次颁发。

“能够获此殊荣,我感到非常兴奋。我尤其高兴的是,千年技术奖将使我的创新受到关注,因为 IGBT 是一种隐藏在社会视线之外的嵌入式技术,”本月早些时候被授予进步能源杰出大学名誉教授头衔的 Bantval Jayant Baliga 教授说道。“它使大量产品成为可能,这些产品改善了全球数十亿人的舒适度、便利性和健康,同时减少了二氧化碳排放,缓解了全球变暖。向公众介绍这一影响深远的创新将展示现代技术对人类的改善。”

Baliga 和他的团队目前正在研究两项新发明,以进一步提高太阳能发电、电动汽车和人工智能服务器电力输送领域的效率。

他说道:“我最近的第一项发明是 Baliga 短路改进概念 (BaSIC),旨在消除工业和电动汽车应用的电机驱动器中使用的碳化硅功率 MOSFET 短路耐受时间较差的障碍。”

“我的第二项新发明是双向场效应晶体管 (BiDFET),它使矩阵转换器能够用于电力电子应用。与现有的电压源逆变器相比,矩阵转换器在尺寸、效率和可靠性方面实现了前所未有的改进。这位电力电子专家表示,这将对电力输送和管理产生革命性的影响。”

芬兰技术学院(该奖项的颁发机构)董事会主席 Minna Palmroth 教授表示:“IGBT 已经并将继续对可持续发展产生重大影响,提高全球生活水平,同时减轻环境影响。应对全球变暖的主要解决方案是电气化和转向可再生能源。IGBT 是解决这些问题的关键技术。”

“我特别高兴的是,该奖项阐明了一项创新,它具有绝对关键性,影响巨大,但大多数人却不知道。我认为这是强调科学和创新力量的绝佳方式。”

千年技术奖国际评选委员会主席 Päivi Törmä 教授表示:“全球三分之二的电力用于驱动消费和工业应用中的电机。Baliga 教授的创新使我们能够高效地利用电力发展社会,同时大幅降低能源消耗。”

“电力电子技术是现代社会的关键技术,其中流程和能源系统的自动化发挥着越来越重要的作用。在过去的 40 年里,直到今天,IGBT 仍然是最重要的功率半导体器件。”

千年技术奖将于 10 月 30 日在芬兰举行的颁奖典礼上颁发给班特瓦尔·贾扬特·巴利加教授,同时该颁奖典礼也是为了庆祝该奖项成立 20 周年。千年技术奖将由其赞助人芬兰总统颁发。

IGBT,伟大的发明

IGBT 是一种高速半导体晶体管,可控制各种设备中的电流。“简单来说,IGBT 可以看作是墙上的电源开关,”Baliga 教授解释道。“它可以改变运行任何负载时控制电源的方式。”

巴利加的职业生涯始于印度理工学院马德拉斯分校的本科生,和他那个时代的许多其他人一样,他迷上了物理学家理查德费曼在 20 世纪 60 年代在加州发表的传奇演讲。

“这本书不在我的课程范围内,而在我们的书店里,”他说。“我以前在其他学生去看电影的时候读这本书,它给了我灵感。”

后来,他在美国获得了电气工程博士学位,并进入通用电气公司工作。巴利加回忆说,他在那里从事晶体管和晶闸管领域的工作,当时半导体行业“已经被认为非常成熟”。

尽管这意味着很难取得重大突破,但他充满了可能产生巨大影响的想法,特别是在如何提高通用电气正在研究的全部产品的电气效率方面。

在向他的上司推荐后,巴利加获得了难得的机会,可以将一个新兴想法从研究阶段快速推进到加州生产线的制造阶段。

当时人们对全球变暖的担忧远没有那么严重。然而,后来人们清楚地认识到,减少 IGBT 设备的耗电量(从 CAT 扫描仪和微波炉到冰箱和日本的子弹头列车等各种设备)将对碳排放产生巨大的积极影响。

20 世纪 80 年代,巴利加教授是通用电气研究实验室的电气工程师。他面临的挑战是制造一种晶体管,这种晶体管可以用于各种工业和家用电器,而且比现有的晶体管效率高得多。巴利加教授回忆起这项发明的早期阶段时说:“当时,我并没有想过它能节省多少电力或减少多少二氧化碳。”“但是,一旦你制造出这种高效的功率半导体,你的目标永远都是提高效率,因为这可以减少半导体的热量,使芯片运行得更好、更可靠,”他补充道。“所以 [降低能耗] 是自然而然的结果。”

当时,巴利加还是一名电气工程师,现年 76 岁的他开发出了绝缘栅双极晶体管(IGBT)的雏形。该技术有望大幅提高电气设备的效率。更高的效率意味着更大的成本节约。

因此,当韦尔奇——这家美国企业集团的领军人物——听说某个想法有可能降低成本时,他便准备接受。“半个小时后,我就说服了他,这是一个好主意,”巴利加告诉《商业内幕》。

如今,IGBT 几乎存在于所有电子产品中:医院的 X 光机、CAT 扫描仪和 MRI 装置等医疗诊断机器;便携式除颤器;微波炉和电磁炉;空调和冰箱……所有风能和太阳能装置都利用基于 IGBT 的技术将产生的电能转换为适合消费和工业应用的形式。“我有一本关于 IGBT 的大书,”Baliga 教授举起一本厚厚的书。“它有 700 页的应用。”它在提高电能使用效率和减少汽油消耗方面发挥了重要作用,因此在过去 40 年的全球减少污染的努力中发挥了关键作用。

巴利加教授拥有 120 多项专利,同时也是一位成功的企业家,他能够在尖端技术与商业化和广泛应用的实际考虑之间找到平衡。“当你创造某种东西时,你首先要关注它的功能并证明它是有效的,”他说。“你想证明它比现有的所有东西都好。否则,从商业化的角度来看,它不会引起太大的兴趣。”他认为功率半导体器件的未来将围绕其在电动汽车、可再生能源系统中的持续使用以及向碳化硅和氮化镓等先进半导体材料的过渡展开。

根据巴利加自己的计算,1990年至2020年间,IGBT通过减少电能和燃料消耗,帮助全球减少碳排放量超过820亿吨,即180万亿点。

回顾自己半个世纪的工作,他回忆说,如果他没有牢记申请美国大学时写的一句话:“开发一种造福人类的技术”,那么他获奖的发明就不可能实现。

“对于一个 21 岁的年轻人来说,这是一个天真的想法,但它真的实现了,所以怎么样,”巴利加说。“所以我对年轻人的鼓励是:要有雄心壮志,但也要做一些对社会有益的事情。”

END

-

IGBT发明者,新的目标 原创 编辑部 半导体行业观察 2024年09月23日 09:10 安徽

-

IGBT发明者,获巨额奖金 半导体行业观察 2024年09月09日 09:10 安徽

IGBT发明者新目标:BiDFET器件

IGBT发明者新目标:BiDFET器件

313

313

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?