随着技术的发展,数字电路的集成度越来越高,设计也越来越复杂。很少有系统会只工作在同一个时钟频率。一个系统中往往会存在多个时钟,这些时钟之间有可能是同步的,也有可能是异步的。如果一个系统中,异步时钟之间存在信号通道,则就会存在CDC(clock domain crossing)问题。在下面的文章里,我们将会讨论CDC的一些技术细节。

一, CDC的基本概念

我们首先来看CDC的一些基本的概念:

1. 时钟域(Clock domain)

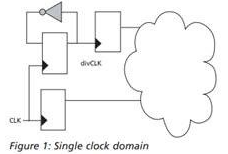

如果某一设计只有一个或者几个有固定相位关系的时钟驱动,我们称这个设计属于一个时钟域。比如,一个时钟和它的反相时钟以分频时钟一般有固定的相位关系,属于同一个时钟域。而如果两个或者多个时钟之间没有固定的相位关系,则它们属于不同的时钟域。

如下图中,divCLK是由CLK分频得到的,divCLK和CLK被认为是同步时钟,而由divCLk和CLK驱动的设计被认为是属于同一个时钟域。

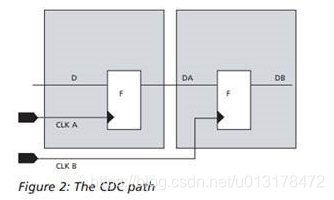

如下图中,CLKA和CLKB之间没有固定的相位关系,是异步时钟。前半部分设计属于时钟域CLKA,后半部分设计属于时钟域CLKB。DA信号从时钟域CLKA进入到时钟域CLKB,是一个跨时钟域的信号,这条path也会被称为CDC path。

如今的数字电路设计中,跨时钟域的情况及其普遍。举一个最简单的例子,一个USB转串口的模块,串口因为波特率的不同,会工作在不同的时钟频率下,USB接口也会因为工作在不同的速度而有不同的工作频率。USB接口的时钟和串口的时钟之间不存在任何相位上的关系,也就是说,USB接口模块和串口模块属于不同的时钟域,他们之间相连的path就是跨时钟域的path。

二 跨时钟域设计的潜在问题

一般来讲,如果设计中存在有多个时钟域,那么就必然会存在跨时钟域的timing path。如果对跨时钟域的timing path处理不当,则容易导致亚稳态,glitch,多路扇出,重新聚合等等问题,导致设计不能稳定工作或者就根本不能正常工作。

1. 亚稳态

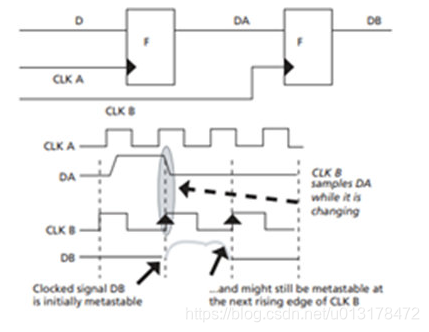

对时序逻辑电路来说,一个DFF的输入信号必须在该DFF的时钟沿前后一段时间内都保持稳定才能保证DFF能锁存到正确的值。这既我们所说的setup time和hold time,其中信号在时钟沿之前的保持时间为setup time,信号在时钟沿之后的保持时间为hold time。正常情况下,如果DFF的输入能满足setup time和hold time的要求,那么在tCO(the clock to output delay)时间内DFF的输出就会达到一个有效的逻辑值(高电平或者低电平)。否则,DFF的输出就需要远大于tCO的时间来达到有效的逻辑值,这段时间内,DFF的输出信号是不稳定的,被称为不稳定状态,或者叫亚稳态。

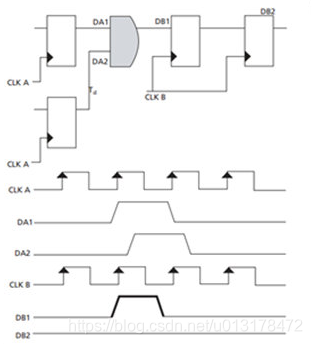

在下图中,如果CLK B在DA变化的时候来对DA进行采样,那么DB就会出现亚稳态。

对于同时钟域的信号。无论是在ASIC设计还是在FPGA设计中,我们也可以方便的通过STA来保证同时钟域的信号能满足setup/hold time的要求,不会出现亚稳态的问题。

但对于异步信号,相位关系是完全不可控的,而且会随时间发生变化,这就必然会存在亚稳态的问题,而且STA工具也没有办法对不同时钟域之间的timing path进行分析。也就是说,我们是没有办法完全避免异步信号之间的亚稳态问题的,但是可以通过在跨时钟域的信号上加入一些特殊的电路来减少亚稳态问题对电路功能所产生的负面影响。

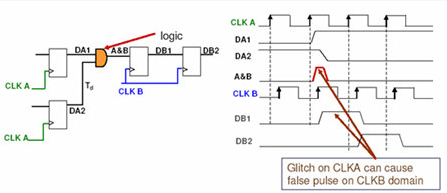

2. Glitch

前面我们讲过,STA工具室不会对跨时钟域的信号做STA。跨时钟域的信号很容易产生glitch并最终影响电路功能。如下图中,CLKA domain中,DA1和DA2分别为两个DFF的输出,理想状态下,DA1和DA2到达与门两个输入端的时间是一样的,这样设计就不会出问题。但由于后端布局,环境等等因素导致的传播延迟Td会使A&B存在一个Glitch。而由于CLKB和CLKA为两个clock domain,之间不存在固定的相位关系,假设这个Glitch恰好被CLKB锁存住,那么就会在DB2生成一个有效的高电平信号,这个高电平信号不是我们的设计所期望的,那就会导致后继的电路功能出现问题。

也有可能是下面的情况,因为Td的影响,导致本应该传递到CLKB的高电平信号没有被传递过去,从而导致后继电路的功能出现问题。

在实际系统中,如果没有处理好跨时钟域的信号,那么由此导致的问题是很容易出现的。我在做silicon debug的时候,曾经多次遇到过由CDC导致的问题。由CDC导致的问题,在实际系统上的表现并不是非常一致,但经常表现出来的就是设计时而可以正常工作,时而出错,而且出错的概率不尽相同,这对问题的分析解决是非常不利的。我曾经遇到过一个CDC导致问题,需要执行数千次的操作,才可能复现出来,但问题一出现就是致命的,会导致系统出错。由于非常难复现问题,分析解决起来就特别困难。所以我们在做设计的时候,要尽量从一开始就解决掉这些问题。

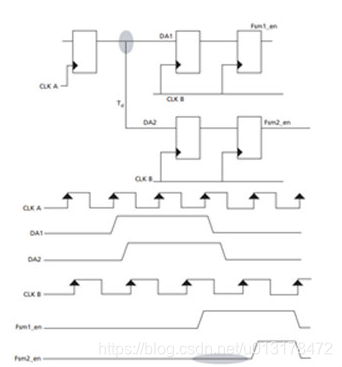

3 多路扇出

如果信号从一个时钟域分多路进入另外一个时钟域,那么很有可能会导致功能上的错误。如下图所示,由于Td的存在,DA1和DA2到达CLKB的时间不同,最终导致fsm1_en和fsm2_en这两个本应该同时有效的信号实际上相差一个CLKB的周期。这很可能会影响到后继的电路功能。

l 重新聚合

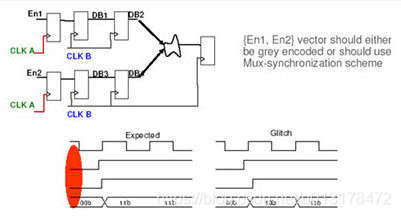

如果多个信号从一个时钟域进入另外一个时钟域,然后这些信号在目标时钟域中又聚合到一起,那么就有可能因为信号的重新聚合导致电路功能上的异常。

如下图所示,原本EN1和EN2转换时钟域后,期望得到的值是2’b00和2’b11,但由于EN1和EN2到达CLKB时钟域的时间有差异,实际得到的值是2’b00,2’b10和2’b11,最终导致后继电路功能出现问题。

本文探讨了数字电路设计中跨时钟域(CDC)的基本概念及潜在问题,包括亚稳态、glitch、多路扇出和重新聚合等,阐述了这些问题如何影响电路功能,并提出了解决方案。

本文探讨了数字电路设计中跨时钟域(CDC)的基本概念及潜在问题,包括亚稳态、glitch、多路扇出和重新聚合等,阐述了这些问题如何影响电路功能,并提出了解决方案。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?