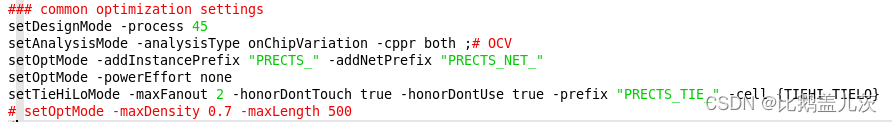

一、优化设置

1.setDesignMode 工艺节点

2.setAnnalysisMode -OCV -cppr

3.名称标记

4.setTieHiLoMode

honorDontTouch 遵守DontTouch DontUse设置 这个DontTouch DontUse属性一般都是工程师设定的,为了后面调用不发生矛盾,设置true属性

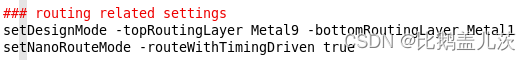

二、routing设置

1.绕线层

2.Timing Driven

Timing Driven顾名思义就是指基于时序驱动进行的placement。大部分的设计都是需要做timing driven的placement优化。

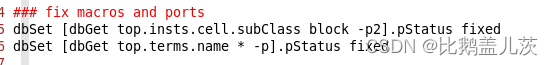

三、固定port和macro

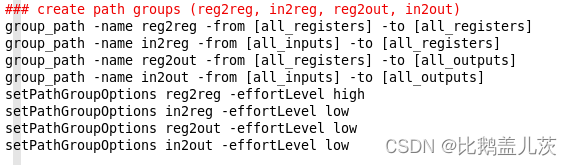

四、设置timing路径和优化力度

主要就是reg-reg时序检查

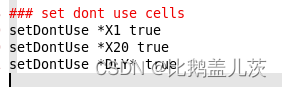

五、dontuse cell

驱动能力小的X1 驱动能力弱的X20

DLY delay cell主要是修hold,一般不用,在eco 修hold会被调用

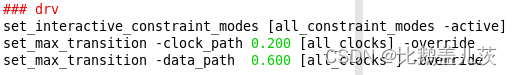

六、 drv

max_transition设置,做设计一般不用库里的,因为太大了,要覆盖lib里的最大,重新设置一个严格的transition。clock path, 一般定义 5%-8%,data path 一般定义 15%-20%,不同厂商不同工艺可能不同。需要注意的是设置这个属性,要先把set_interactive_constrants_mode打开,这是规定。

注:本设计clock cycle 4ns

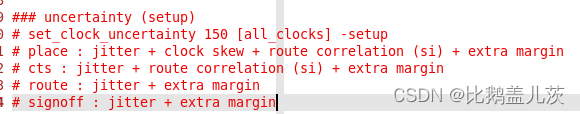

七、clock uncertainty

这个细节可以注意一下

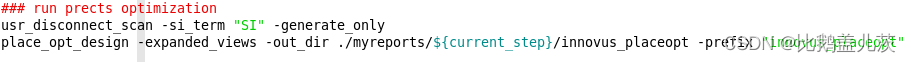

八、place_opt_design

expand_view 让工具严格的根据是多个view分析, 不要merge

expand_view 让工具严格的根据是多个view分析, 不要merge

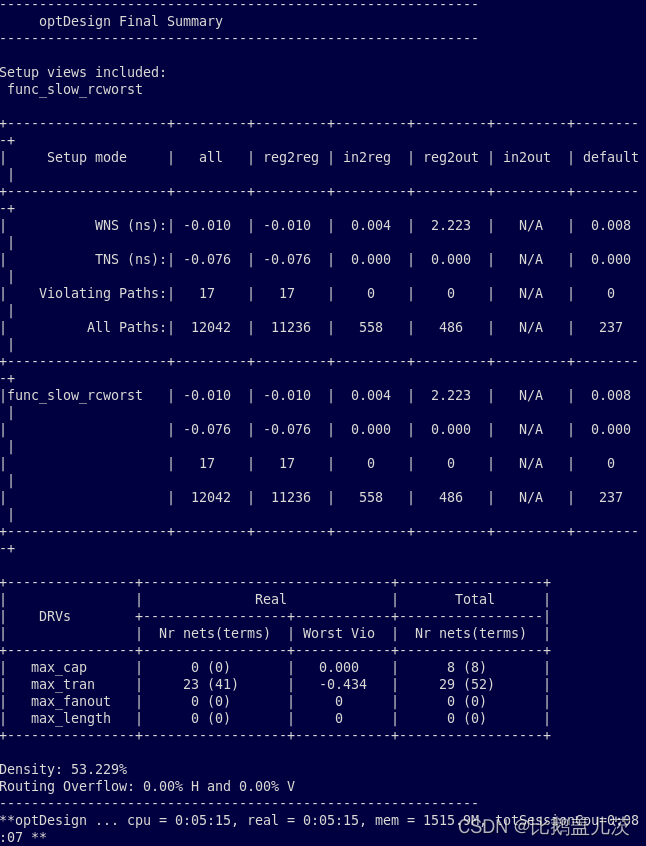

八、报告:

九、

本文详细介绍了集成电路设计中的关键步骤,包括设置工艺节点、时序驱动的placement优化、routing策略、端口和宏的固定、时序路径的定义以及transition限制。还强调了clockuncertainty的考虑和放置优化设计的注意事项。

本文详细介绍了集成电路设计中的关键步骤,包括设置工艺节点、时序驱动的placement优化、routing策略、端口和宏的固定、时序路径的定义以及transition限制。还强调了clockuncertainty的考虑和放置优化设计的注意事项。

2949

2949

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?