计算机的基本组成

基本概念

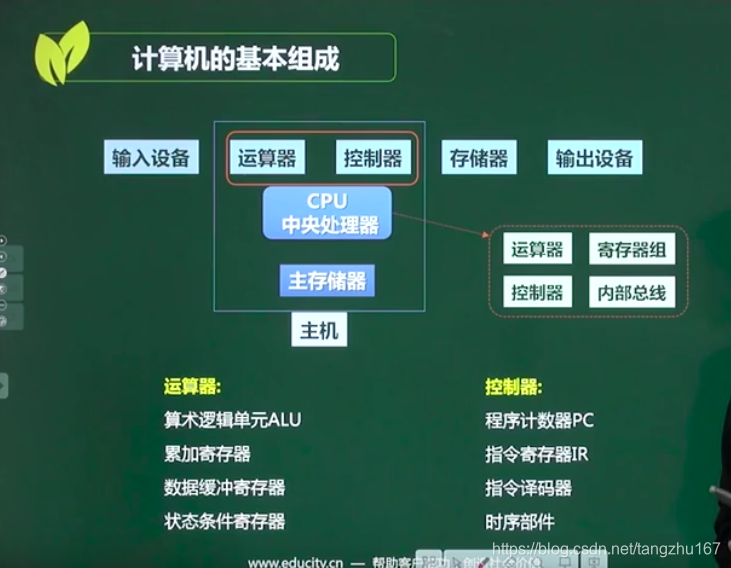

计算器由输入设备(如键盘鼠标摄像头)运算器,控制器(组成CPU)存储器(如硬盘),输出设备(显示器,声音播放)组成

运算器和控制器合称为CPU(中央处理器)

运算器和控制器合称为CPU(中央处理器)

运算器的组成:

算数逻辑运算单元ALU(执行算数和逻辑运算的单元)

累加寄存器(用来存储进行运算操作的运算数和操作结果,如计算5+6,先把5取出来保存到累加寄存器中,再去取6,运算完成后,11也保存在内,累加计算器只能存一个操作数和运算结果)

数据缓冲寄存器(保存操作数和运算结果的寄存器,与累加计算器相似,但是它可以存多个)

状态条件寄存器(比如说溢出,进位各种状态变化寄存在这)

控制器的组成

程序计数器PC(CPU需要通过它找到指令,作用为告诉CPU下一条要执行的指令在哪)

指令寄存器IR(指令从内存取出来后,放到指令寄存器IR中)

指令译码器(对指令进行译码,让CPU能够执行)

时序部件(产生时帧脉冲,不知道是啥,估计是指挥CPU执行哪个指令的)

控制器记忆方法:指令需要从内存中读到CPU里保存,然后译码成CPU能执行的指令,译码完成后执行

***寄存器组:***在CPU里,有一些专用的寄存器组,用来寄存一些指令,数据,状态条件等

内部总线:连接芯片内的总线,把芯片内的各个部件连接在一起

主机的概念:在计算机组成原理中,CPU+主存储器(内存),就称为主机(与现实不同,现实我们把主机箱里的所有组成称为主机)

章节主要考点

1,cpu由哪两个部分组成?

2,cpu由哪四个部分组成?

3,运算器和控制器包含哪些?

4,运算器或控制器某个部件的功能是什么?

CPU、总线的性能指标

CPU性能指标:

主频(CPU运行频率,多少赫兹,如3.2GHZ)

字长(指CPU一次能处理2进制的位数,如一次能处理8位2进制数00000001,那么他就是8位的CPU)

CPU缓存

核心数量(指CPU中独立的计算引擎数量)

注意,字节和字长:如CPU字长为8位,如00000001,是算一个字节,那么32位的CPU一次就能处理4个字节,64位的一次就是8个字节

总线的分类(重点):

数据总线(负责传输数据)

控制总线(负责传递控制信号)、

地址总线(决定系统能够使用多少内存,如32位系统之所以被淘汰,内存只能是2^32位=4G,最大内存只能是4G,它没法配8G,16G的内存)。

总线的性能指标

带宽(单位事件内传输数据的量,如MB/S)

位宽(常考内容,指总线能够同时传送多少位二进制,数据总线的位宽一般与字长相等)

指令和寻址

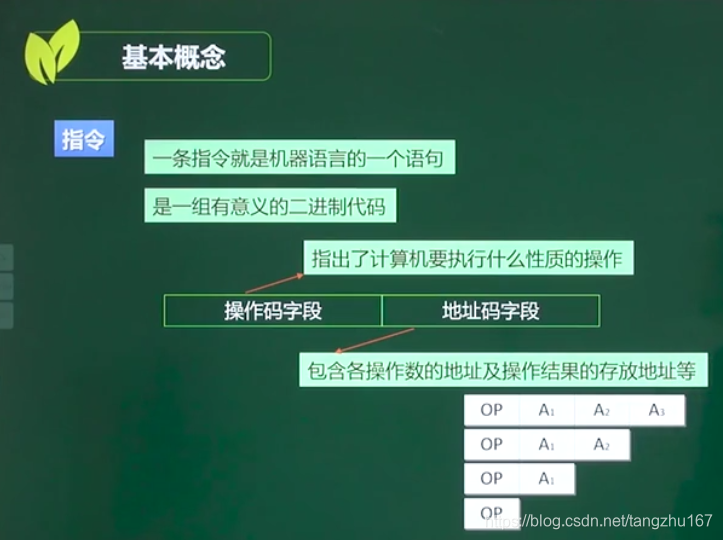

指令:就是指挥CPU进行操作的计算机语句,是一组有意义的二进制代码,它由操作码字段和地址码字段组成,个人理解可以看做一个HTTP请求,以GET方法作为操作码字段(告诉计算机要执行什么性质的操作),请求地址作为地址码字段(包含操作数的地址、操作结果的存放地址等)

指令:就是指挥CPU进行操作的计算机语句,是一组有意义的二进制代码,它由操作码字段和地址码字段组成,个人理解可以看做一个HTTP请求,以GET方法作为操作码字段(告诉计算机要执行什么性质的操作),请求地址作为地址码字段(包含操作数的地址、操作结果的存放地址等)

CPU进行运算时,你的操作数在哪?,上述内容,我们知道了操作数的地址在指令的地址码字段中,这时候就要根据指令寻找操作数,就需要寻找数据地址的方式

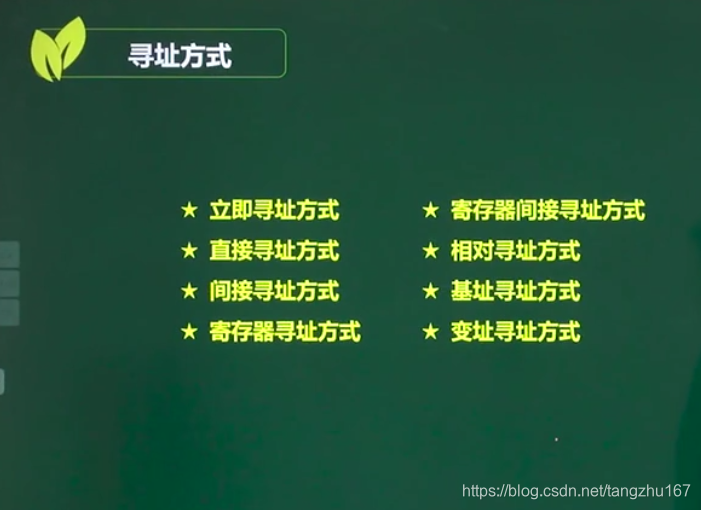

需要掌握的有如下几个:

需要掌握的有如下几个:

立即寻址方式:操作数就放在指令的地址码部分,读这条指令时直接就读到了这个数

直接寻址 :操作数在主存内,指令里放了操作数在哪一个地址(门牌号)

间接寻址:操作数在主存某个地址B,在指令里放了地址A,让指令去读取地址A获取操作数B的地址(找人时,问路人(指令),张三(B)在哪?路人(指令)说他不知道,但是他知道李四(存在指令地址码中的地址A)知道,让你去问李四(A),你去问李四(A),李四告诉你张三的地址在B)

寄存器寻址方式:指令地址码字段写的是告诉CPU数据在哪个寄存器里(不在主存里)

寄存器间接寻址:指令地址码字段写的是张三寄存器的地址,张三寄存器告诉你李四在哪个寄存器

相对寻址方式,基址寻址方式,变址寻址方式,这三种很少考察,需要了解自行百度

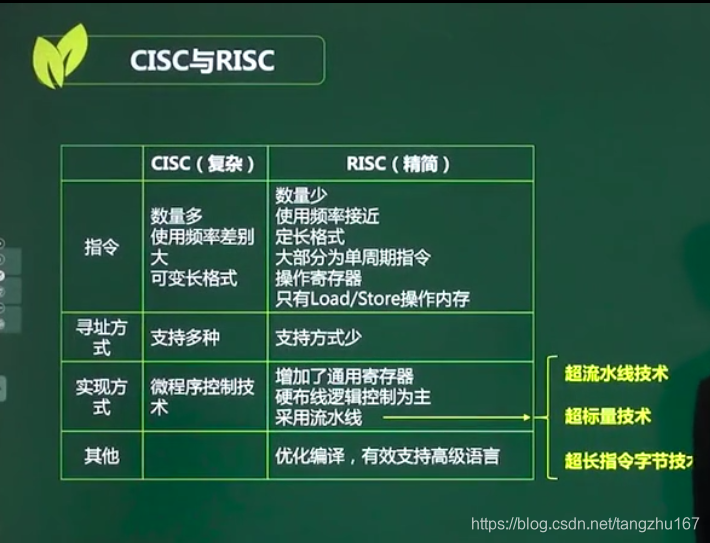

CISC和RISC

CISC(Complex Instruction Set Computer )复杂指令集计算机

RISC(Reduced Instruction Set Computer)精简指令集计算机

都是计算机中央处理器的一种设计模式

考试记忆法(记一半):

考试记忆法(记一半):

精简指令(使用频率接近,定长格式,大部分为单周期指令,操作寄存器,只有Load/Store操作内存) 明显指令数量少

实现方式:硬布线及控制为主(通过集成电路实现),由于操作的是寄存器,所以需要增加通用寄存器,采用流水线(超流水线技术,超标量技术,超长指令字节技术)

优化编译,有效支持高级语言

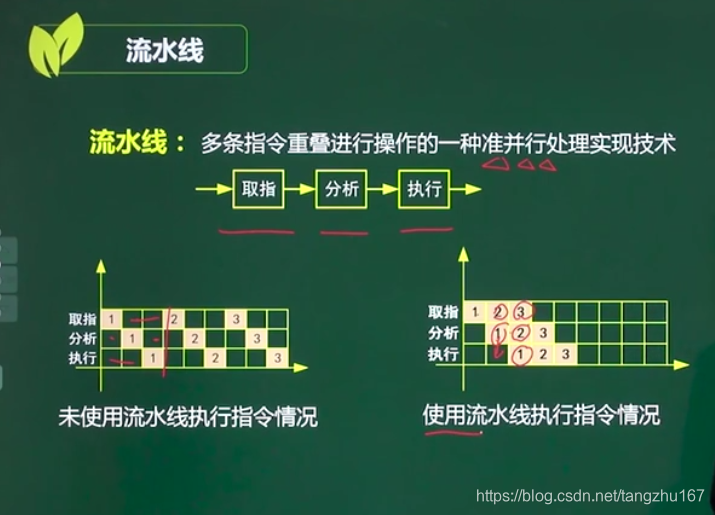

流水线

多条指令重叠进行操作的一种准并行处理实现技术

解析:如下图,一个流水线从取指-分析-执行,在取指完成时,任务1到了分析步骤,取指部分就空闲下来了,这时候就可以继续取指任务2,分析任务1完成后,分析1到了执行步骤,分析部分就可以继续分析任务2,这样不用等待执行完成,前序步骤就可以继续下一个任务,能够较大提高CPU性能

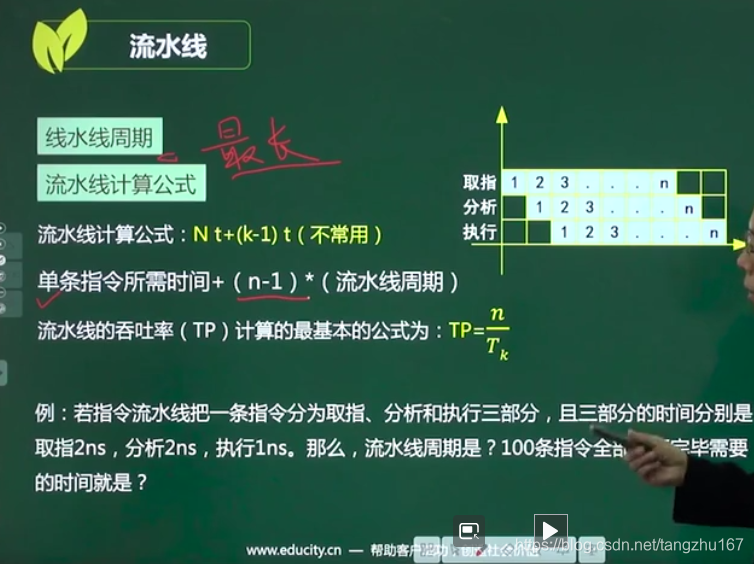

流水线考点:

1,流水线周期:由最大花费时间的步骤决定,如取指需要(2S),分析需要(5S),执行需要(4S),那么这个流水线的周期就为5S

图中例题,求100条指令全部执行完毕需要的时间:

图中例题,求100条指令全部执行完毕需要的时间:

单条指令所需时间:(2ns+2ns+1ns)=5ns

流水线周期:2ns

套入公式: 单条指令所需时间+(n-1)流水线周期=5ns+992ns=203ns

流水线吞吐率:指令条数/所需时间=100条/203ns=0.49条/ns

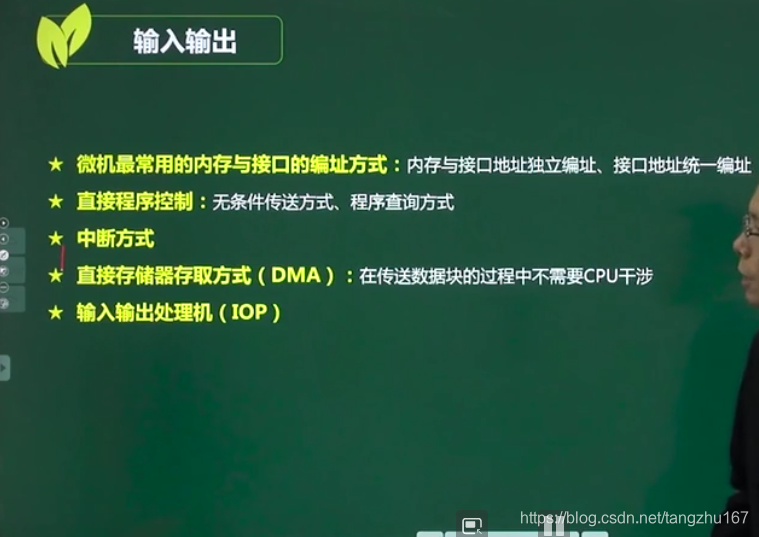

输入输出(重点在于中断和DMA)

中断(在外层要传数据时,它发出中断信号,CPU收到信号,中断工作以响应外层的请求)

中断(在外层要传数据时,它发出中断信号,CPU收到信号,中断工作以响应外层的请求)

1,中断响应时间(指的CPU收到指令,保存正在进行的工作,再响应外层请求的时间)

2,中断向量(矢量)(处理完外层请求时间后,继续进行中断之前保存的工作,通过中断向量获取到之前保存的工作在哪))

DMA(直接存储区存取方式)考点1:英文缩写与汉字件的关系,考点2:DMA的特点:在传送数据块的过程中不需要CPU干涉,提高了CPU性能

多级存储器结构

**虚拟存储:**利用程序在运行过程中,在主存和外存之间来扩展主存的一项技术(如天刀上百G,为啥能在几个G的内存中运行,这是因为在程序运行过程中,允许部分加载)

**虚拟存储:**利用程序在运行过程中,在主存和外存之间来扩展主存的一项技术(如天刀上百G,为啥能在几个G的内存中运行,这是因为在程序运行过程中,允许部分加载)

外存(比如光盘,闪盘),主存(如硬盘),高速缓存(如内存),寄存器(CPU上)

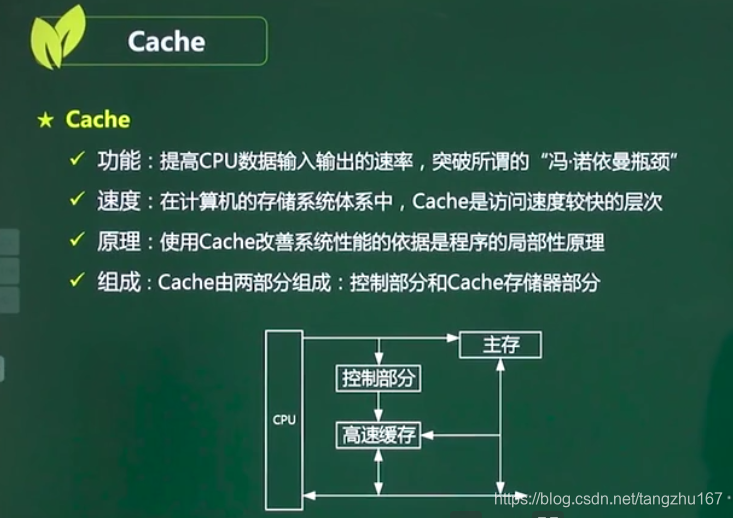

cache分两部分:控制部分,高速缓存的存储部分,它是由硬件进行控制的

cache分两部分:控制部分,高速缓存的存储部分,它是由硬件进行控制的

cache存在的原因主要是解决CPU和主存间的速度差,CPU飞的起来,主存相对很慢

考点:cache是由硬件部分实现的

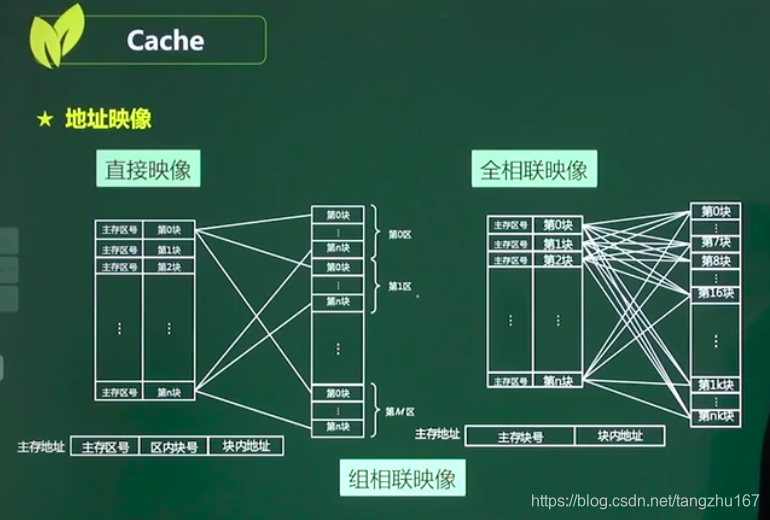

直接映像特点:把主存和缓存都划分成块,块内地址对应逻辑清晰,缓存中对应区的第0块放在主存对应区号第0块,但是如果缓存中另一个区的第0块要放入主存,就不能放在第0块(因为满了),且其他块是空的也不能放在其它块,因为这种方式不允许,这就容易产生冲突

直接映像特点:把主存和缓存都划分成块,块内地址对应逻辑清晰,缓存中对应区的第0块放在主存对应区号第0块,但是如果缓存中另一个区的第0块要放入主存,就不能放在第0块(因为满了),且其他块是空的也不能放在其它块,因为这种方式不允许,这就容易产生冲突

全相联映象:可以随机空位放入主存某个区的某个块,但是这样地址逻辑比较复杂,需要通过计算才能实现,比较复杂

**组相联映像:**把cache和主存都分成组,组内分成块,第一组只能放入第一组,第二组只能放第二组,这样,但是缓存第一组里的块,可以放入主存第一组内任意的块里面

这块老师说一半视频没了,后面补

这块老师说一半视频没了,后面补

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?