在后仿过程中,由于仿真过程非常漫长,所以一般会评审出关键路径进行仿真覆盖。另外问题定位也很麻烦,所以希望在环境中拉取一些网表中的信号(比较明确的信号,在网表迭代中不会发生大的变化)辅助定位。

1. 比如可能需要过程中复位,或者过程中掉电的场景进行覆盖。那么case中会在不确定的时间点进行复位或掉电,然后设计中一般是异步复位同步释放。复位的瞬间有可能导致violation的产生,所以确定希望各个模块或者子系统的复位和解复位的时间点,辅助进行排除。那么环境中可以进行以下处理。

`define postsim_rsts_detect(signals) \

forever begin: rsts_rose \

@ (posedge signals) `uvm_info("``signals`` rose", $sformatf("``signals`` posedge @%0t", $realtime), UVM_LOW) \

end \

forever begin: rsts_fall \

@ (negedge signals) `uvm_info("``signals`` fall", $sformatf("``signals`` negedge @%0t", $realtime), UVM_LOW) \

end

initital begin

fork

`postsim_rsts_detect(tb_top.dut.rst_n)

`postsim_rsts_detect(tb_top.dut.xxx.rst_n)

`postsim_rsts_detect(tb_top.dut.xxx.rst_2nd_n)

`postsim_rsts_detect(tb_top.dut.yyy.rst_n)

`postsim_rsts_detect(tb_top.dut.yyy.rst_2nd_n)

...

join

end

或者可以使用ucli的相应命令对特定时间段进行排除(还没测试过,初步看可行,各位工程师朋友可以提一些建议或想法)

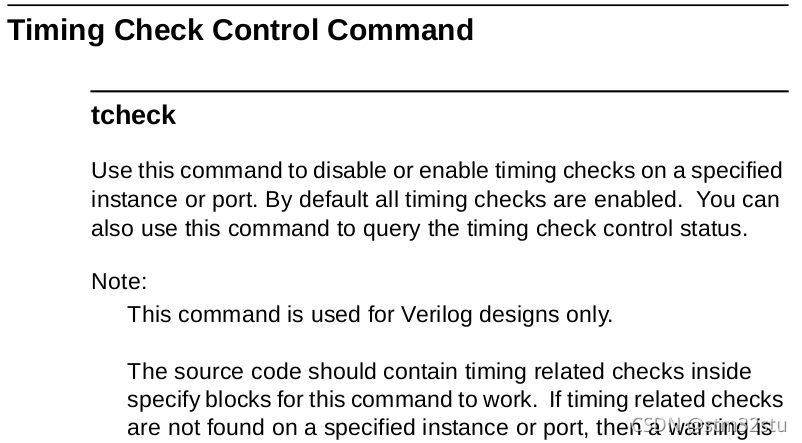

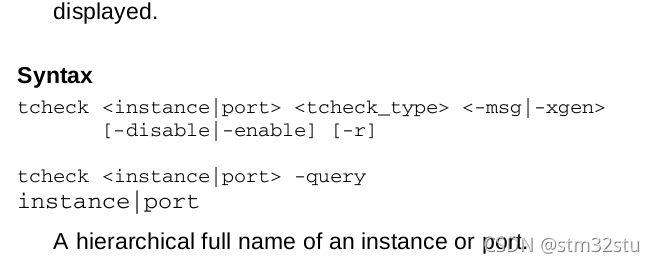

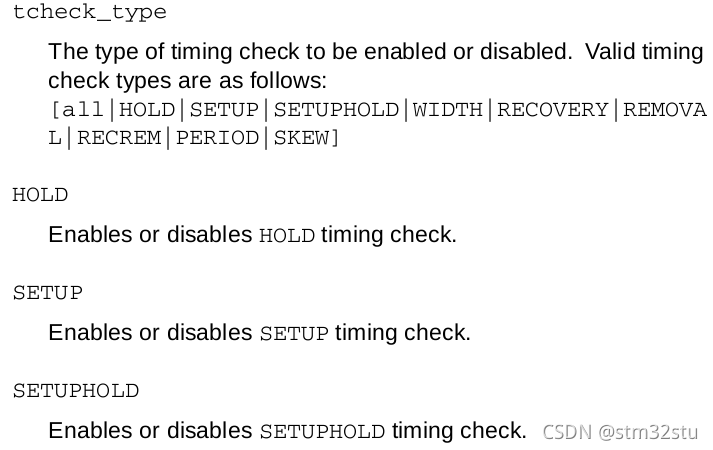

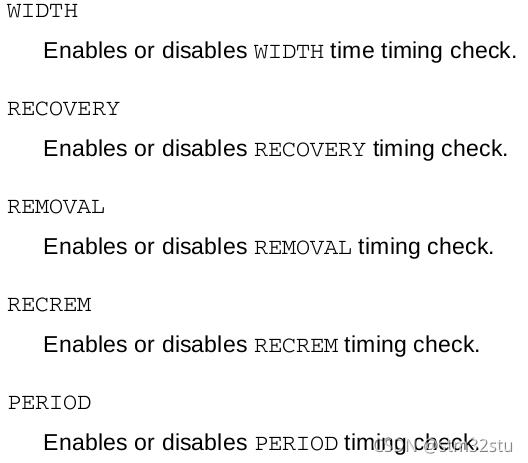

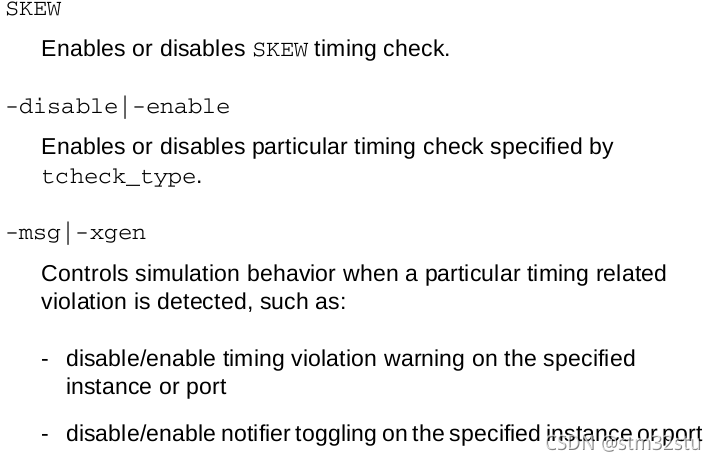

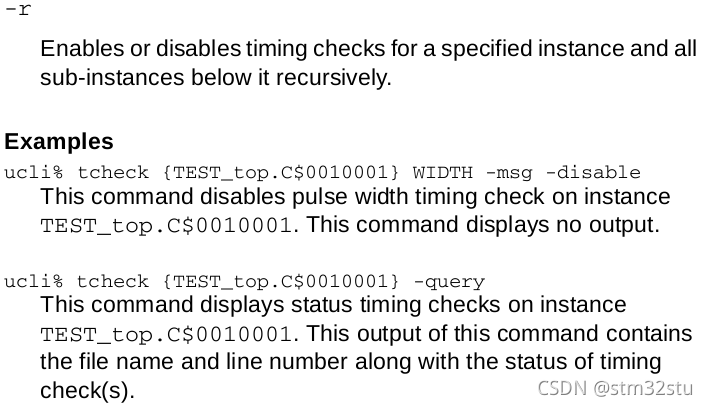

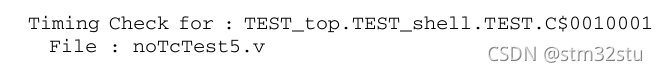

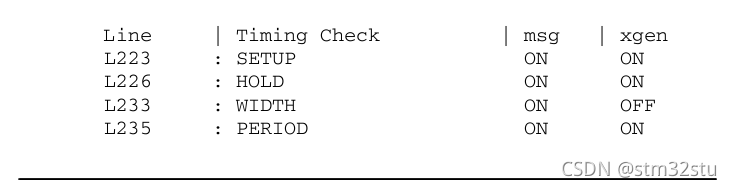

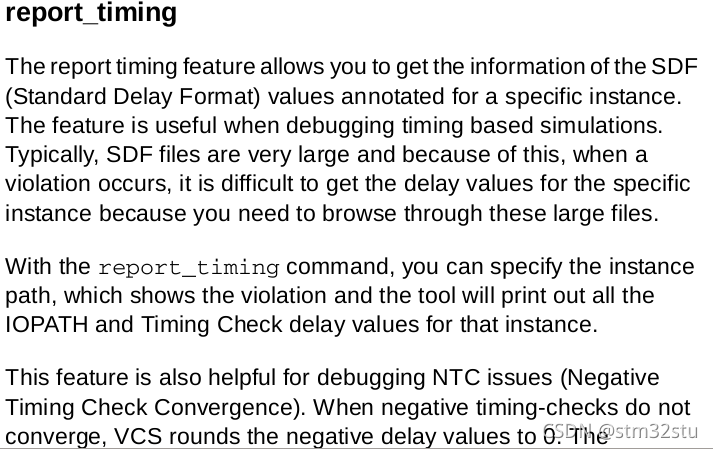

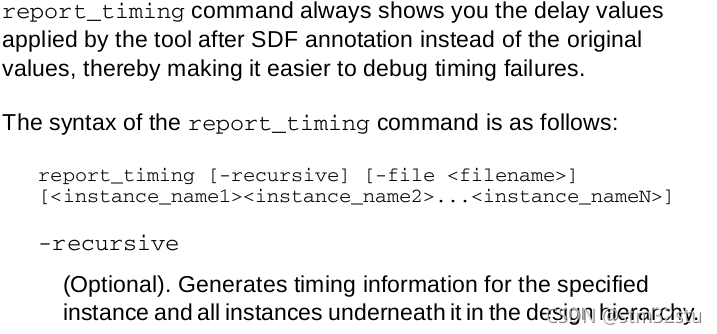

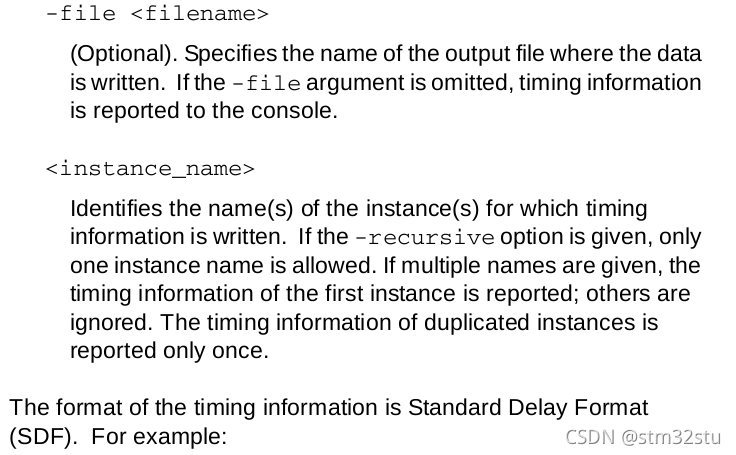

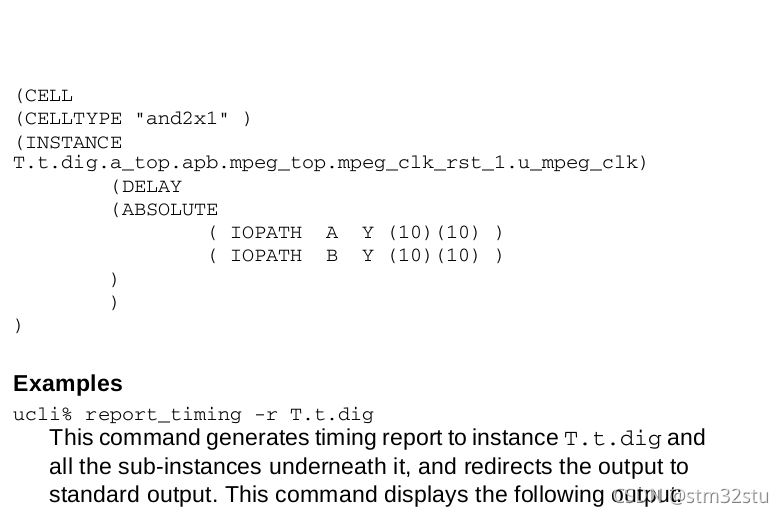

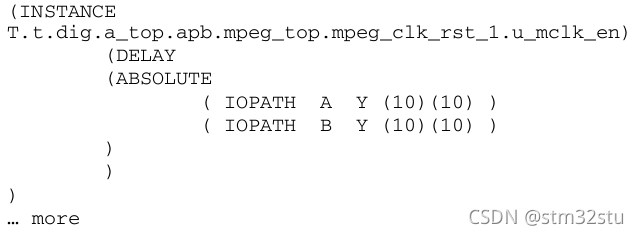

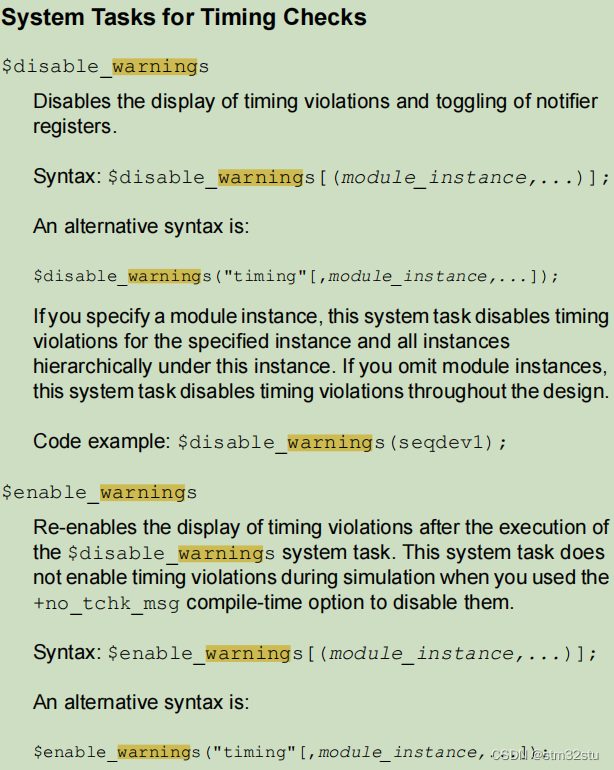

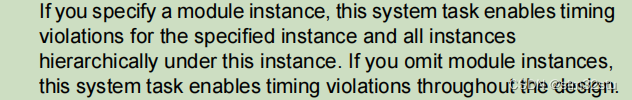

ucli的user guild(和vcs的user guild是两个不同的文档)可以在vcs的安装目录找到,如下图所示部分的 tcheck命令。

本文探讨了在长时仿真的后仿过程中,如何通过检测关键信号如复位和掉电来辅助定位问题。通过定义`postsim_rsts_detect`函数和使用UCLI命令,作者提出在不确定时刻监控复位事件,以帮助确定模块间复位时间点,减少violation。建议工程师们分享相关经验和建议。

本文探讨了在长时仿真的后仿过程中,如何通过检测关键信号如复位和掉电来辅助定位问题。通过定义`postsim_rsts_detect`函数和使用UCLI命令,作者提出在不确定时刻监控复位事件,以帮助确定模块间复位时间点,减少violation。建议工程师们分享相关经验和建议。

3967

3967

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?