概要

通常Quartus大型工程中都含有IP核,如果联合Questasim仿真就需要在Questasim中添加Altera仿真库。

QuestaSim添加altera仿真库

QuestaSim仿真功能强大,但是没有跟具体的器件相结合所以仿真带有IP核的工程时就会出错。那么通过添加相应器件的仿真库就可以了。关于器件,可以是lattice的,也可以是altera的,添加的方法其实都是一样的。我这里使用的是altera的仿真库。quartus软件中自带有altera的仿真库,我们只要把它拿到modelsim中去编译一下就可以了。具体步骤如下:

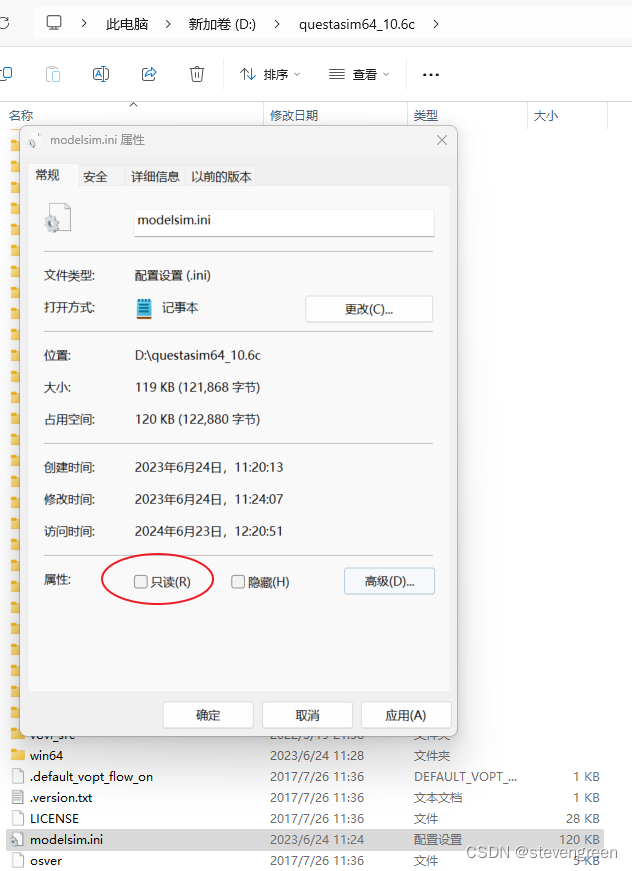

1、去除QuestaSim安装目录下modelsim.ini的只读属性,添加库的时候会在里面写入路径(使得这个.ini的配置文件可以被修改)

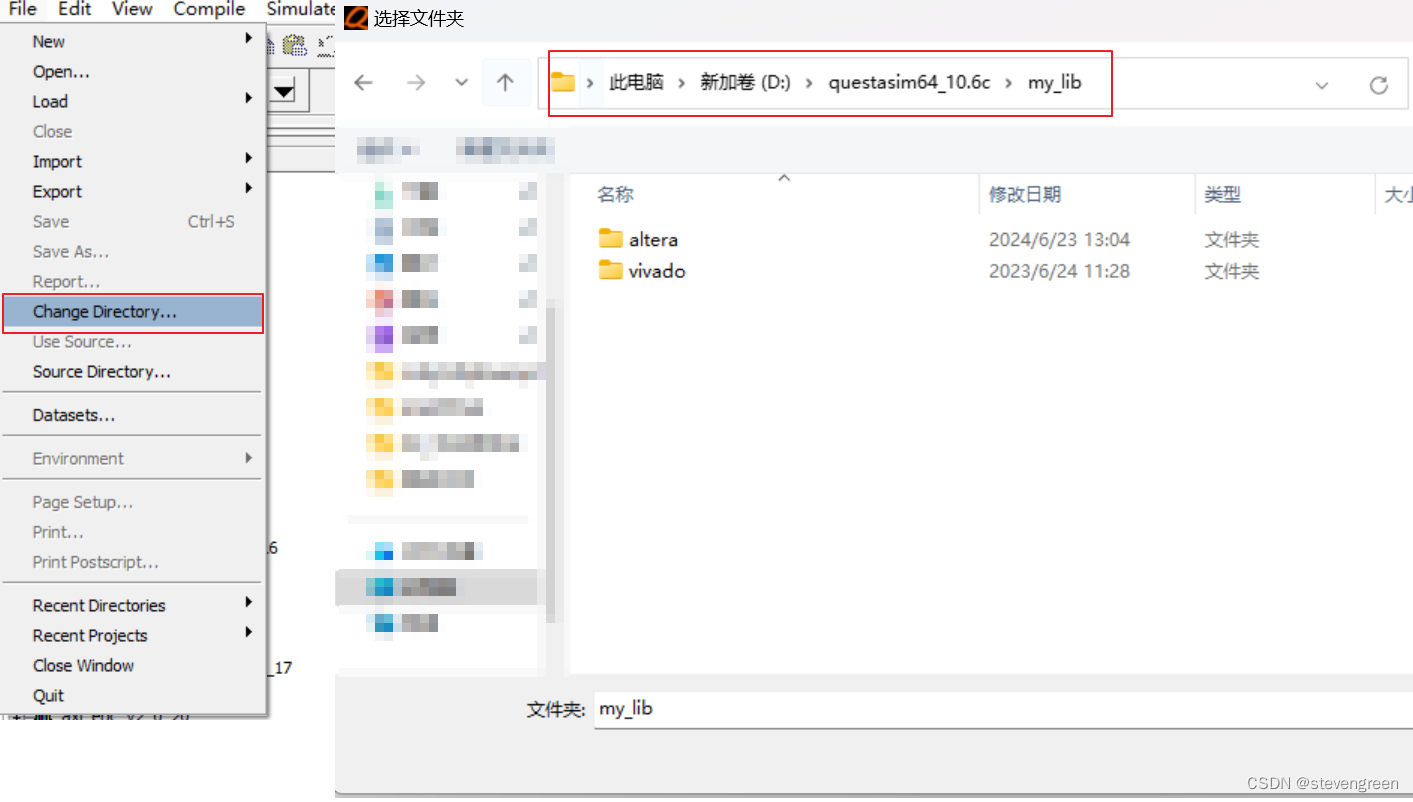

2、打开QuestaSim,更改目录File->Change directory到根目录下或者自己新建的文件夹(这里我切换到了自己新建的文件夹my_lib,后续其他器件的仿真库都在这个文件夹内,方便查找)

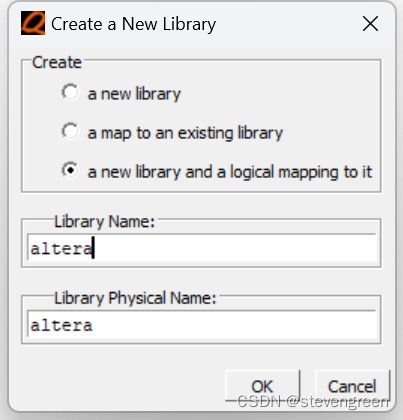

3、点击file-new-library,新建一个库,输入库名称,在modelsim的library界面下会新建一个altera库。

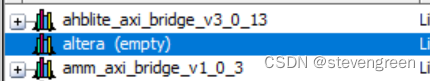

点击OK后就会出现一个空的altera库目录

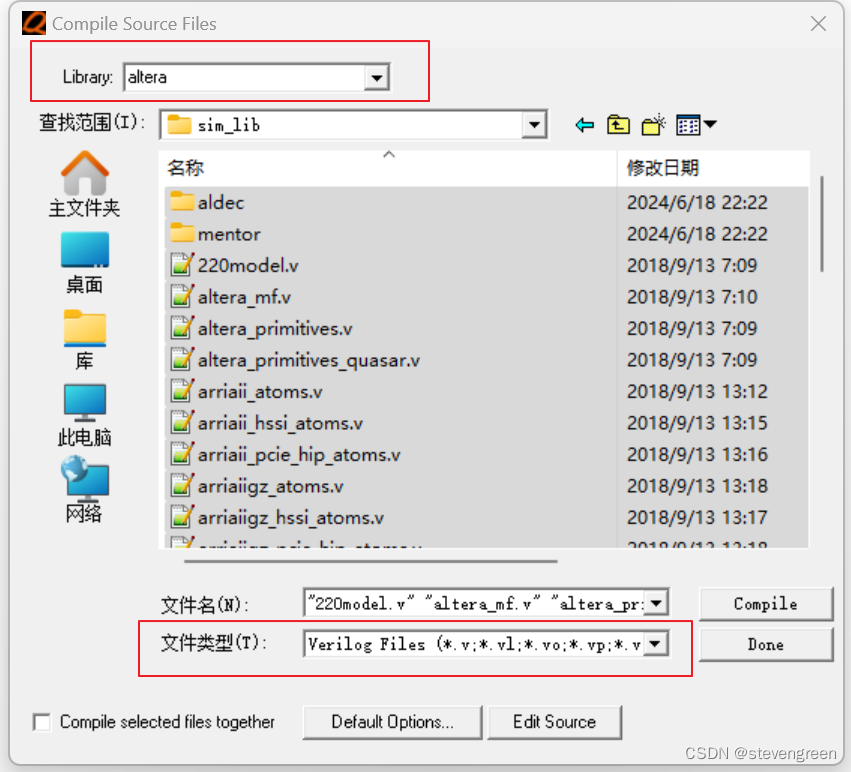

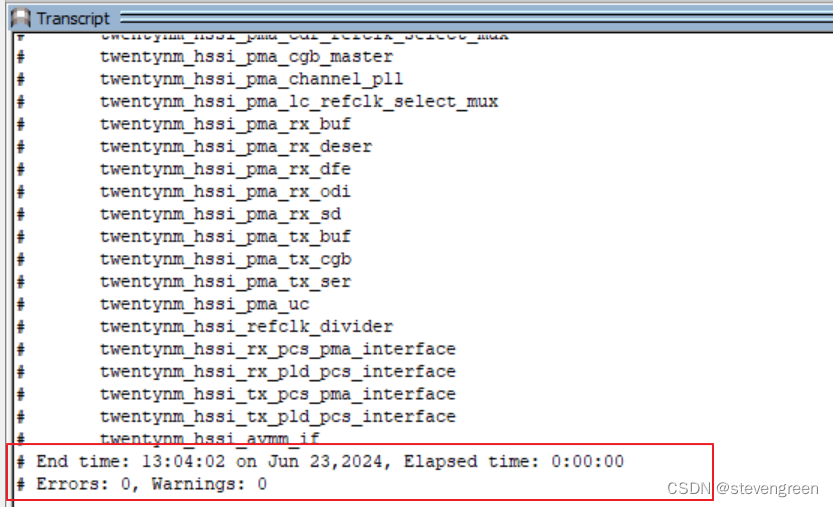

4、点击Modelsim菜单栏的compile–compile,出现编译窗口,将library选为你新建的库,在查找范围内选择altera库文件的所在地,我这里是D:\intelFPGA\18.1\quartus\eda\sim_lib,如果你是用vhdl编写代码的则选择vhdl,verilog编写代码的话就选verilog。点击compile开始编译,编译完成后点Done结束。

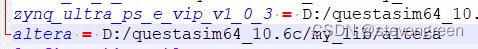

5、此时打开"modelsim.ini",里面多了一句altera = altera,将后面那个改为你的物理路径:altera = D:/questasim64_10.6c/my_lib/altera(否则会出现unname什么的,注意这里用 / 而不是用 \ )。最后将modelsim.ini的只读勾上。

Quartus联合QuestaSim仿真

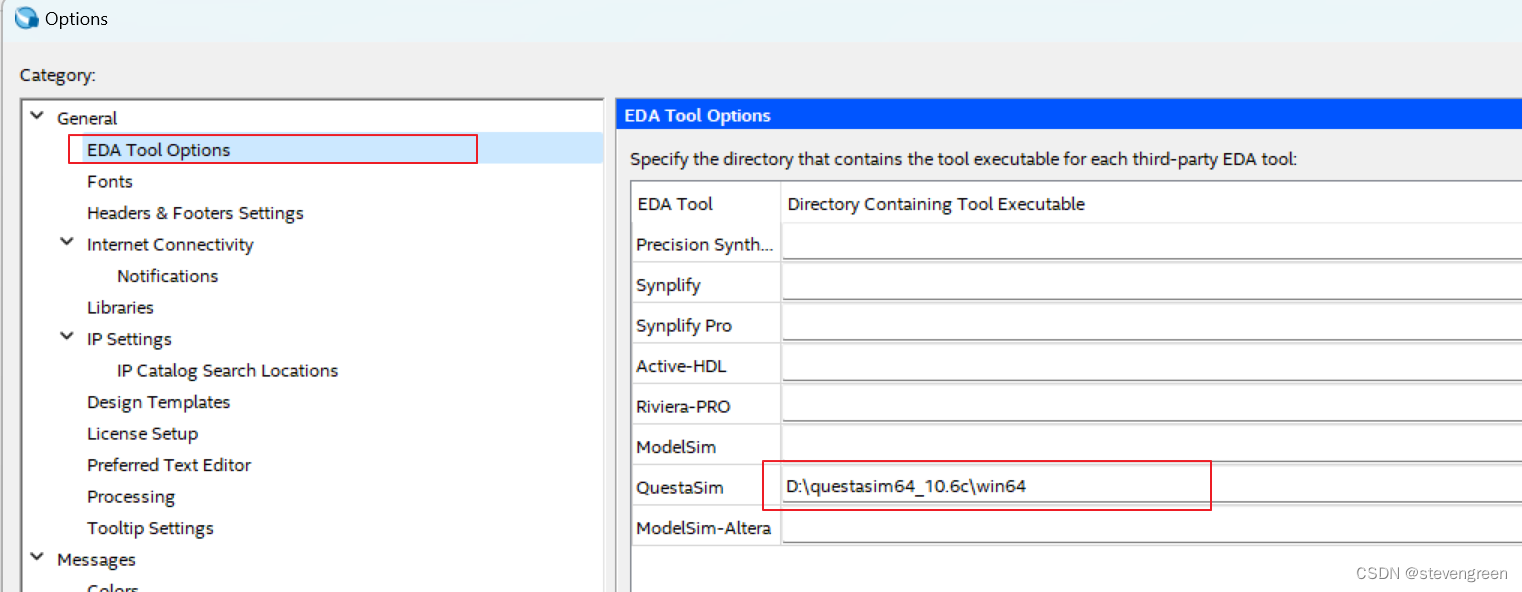

1、设置QuestaSim工具路径:Tools-Options,打开如下设置菜单。

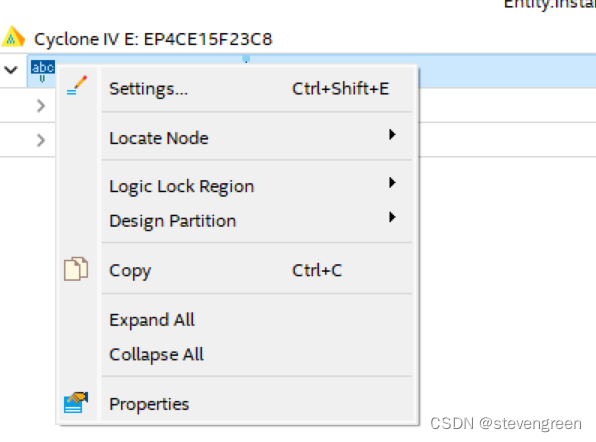

2、设置仿真tb文件:在工程的顶层文件中,右击选择settings。

2、设置仿真tb文件:在工程的顶层文件中,右击选择settings。

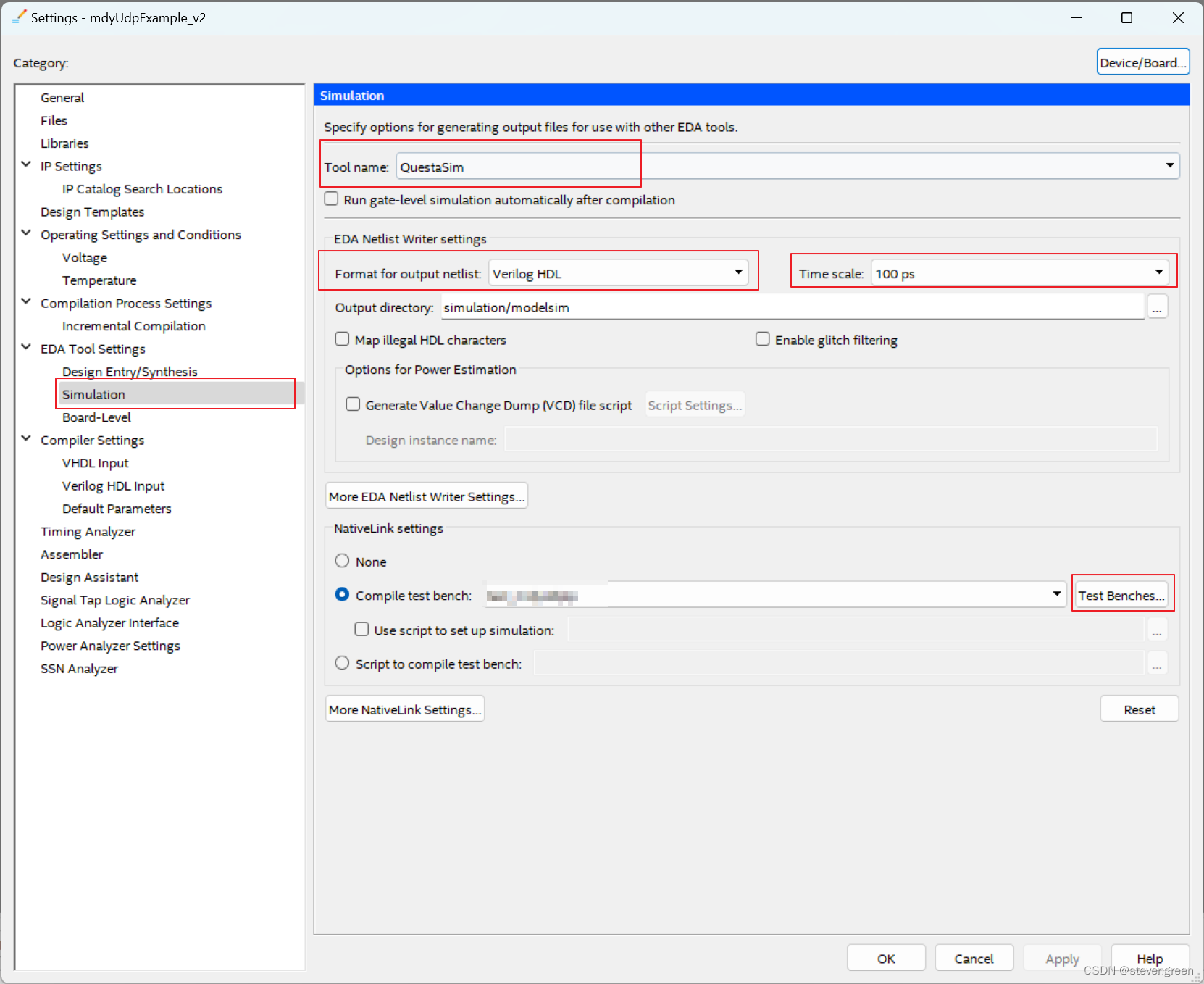

在弹出的窗口中,设置如下:

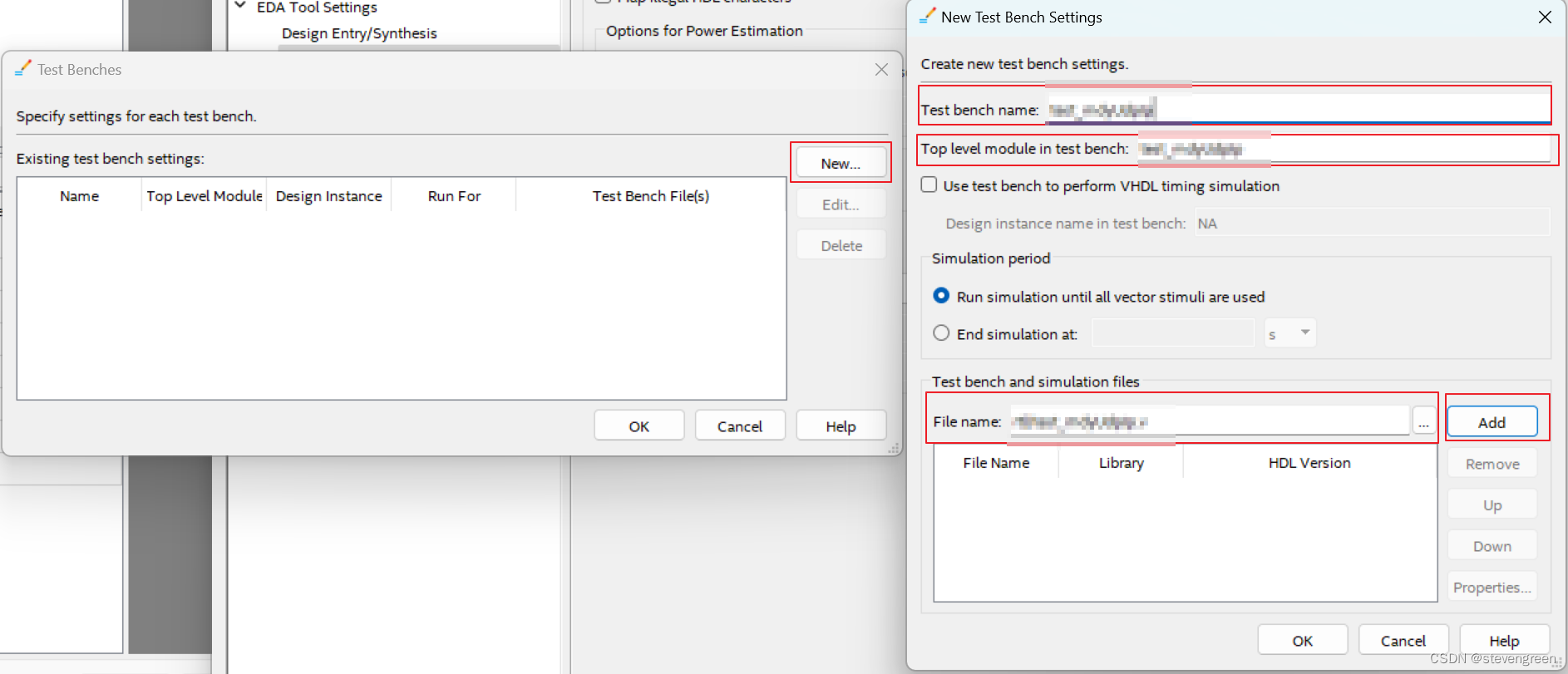

最后点击Test Benches按键,开始进行tb文件设置:

在 Test bench name 中,填写测试文件名。即tb文件名。

在 Top level module in test bench 中,填写tb文件中的模块名,即 module name。一般规范的是模块名与测试文件名一致,此处填写一样即可。

在File name一栏中填写tb文件的路径,点击Add即可。设置完成后,点击OK。

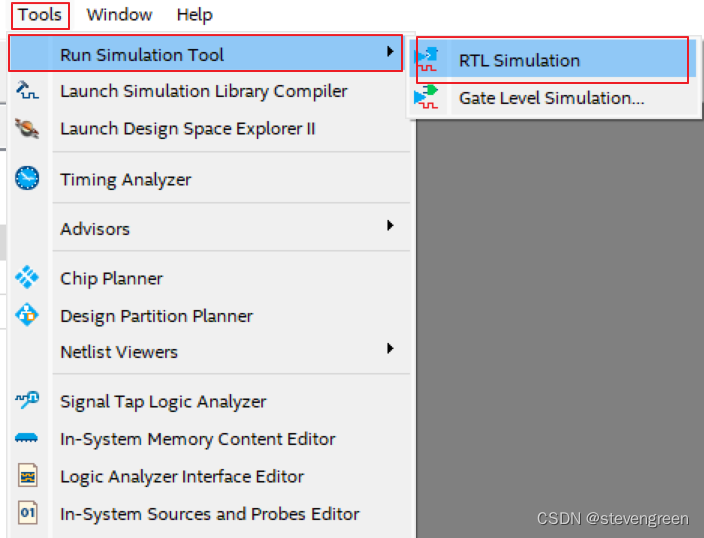

3、运行RTL仿真:调用QuestaSim进行编译和仿真。

点击完后,就会自动打开QuestaSim进行仿真。

小结

以上总结了Quartus联合QuestaSim仿真的准备工作,当然联合其他如lattice,xilinx等也可以作为参考。

1229

1229

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?